Table of Contents

PHYTEC Meßtechnik GmbH 2003 L-623e_1

Preface ......................................................................................................1

1 Introduction .........................................................................................3

1.1 Block Diagram..............................................................................6

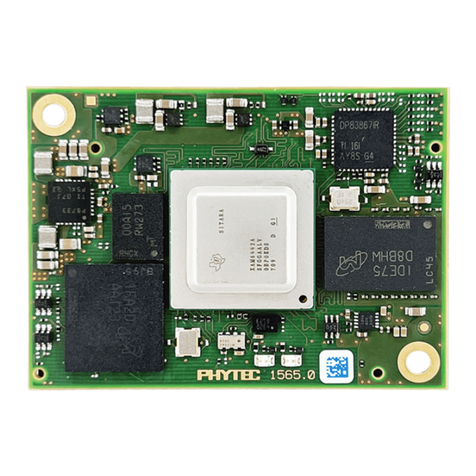

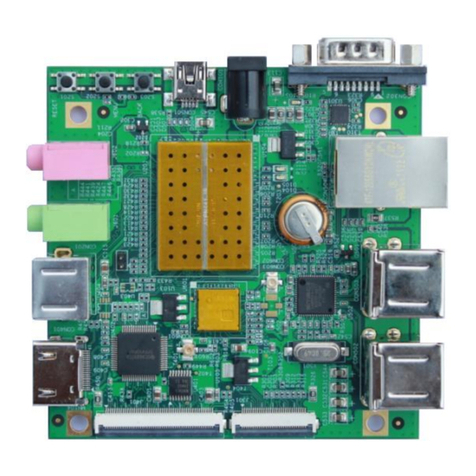

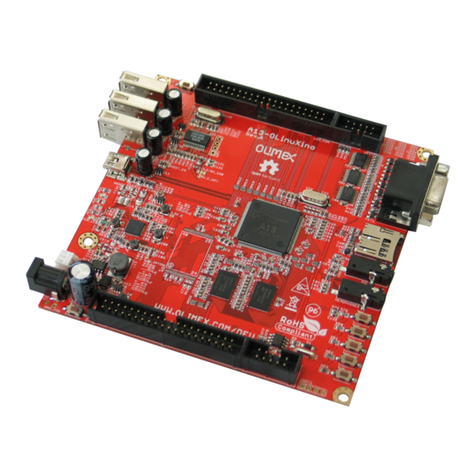

1.2 View of the phyCORE-XC167.....................................................7

2 Pin Description.....................................................................................9

3 Jumpers..............................................................................................17

3.1 J1, J2 A/D Reference Voltage ...................................................23

3.2 J3 Internal or External Program Memory..................................23

3.3 J4, J35 SRAM U6/U7 Chip Select ............................................24

3.4 J5 SRAM Memory Size.............................................................25

3.5 J6 E²PROM/FRAM Supply Voltage .........................................25

3.6 J7 Write Protection of E²PROM /FRAM ..................................26

3.7 J8, J9 Address of the Serial E²PROM/ FRAM..........................26

3.8 J11, J12, J15, J16 CAN Interfaces.............................................27

3.9 J13, J14, J17, J18 CAN Transceiver..........................................28

3.10 J19 RTC Interrupt Output..........................................................29

3.11 J20, J21 Configuration of P9.4 and P9.5 for I²C Bus................29

3.12 J22 RTC (U13) Clock Output....................................................30

3.13 J23, J24 First Serial Interface ....................................................30

3.14 J25, J26 Second Serial Interface................................................31

3.15 J27 Ethernet Controller Chip Select..........................................32

3.16 J29 Ethernet Controller Sleep Mode..........................................32

3.17 J30 Ethernet Controller IRQ Signal...........................................33

3.18 J32 Write Protection of Flash....................................................33

3.19 J33, J34 SRAM Chip Select U5 ................................................34

3.20 J36 Organization of E²PROM U15...........................................34

4 System Configuration........................................................................35

4.1 System Startup Configuration.....................................................35

5 Memory Models.................................................................................39

5.1 Bus Cycle Phases........................................................................42

6 Serial Interfaces.................................................................................45

6.1 RS-232 Interface.........................................................................45

6.2 CAN Interface.............................................................................46

7 Real-Time Clock RTC-8564 (U13)...................................................47

8Serial E²PROM/FRAM (U8) ............................................................49

9 Flash Memory (U4)............................................................................51

10 Battery Buffer and Voltage Supervisor Chip (U9).........................52

11 CS8900A Ethernet Controller..........................................................53