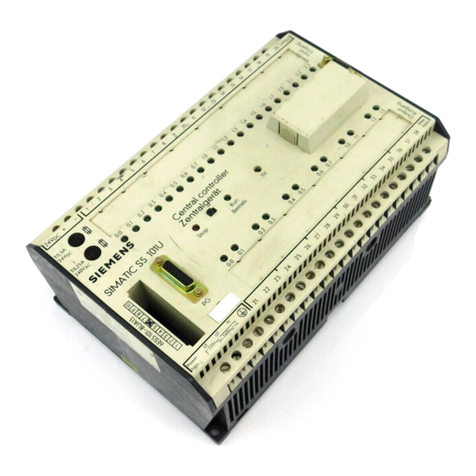

Index-2 PLC S7-300, CPU Specifications CPU 312 IFM to CPU 318-2 DP

A5E00111190-01

!Danger

indicates that death, severe personal injury or substantial property damage will result if proper precautions

are not taken.

!Warning

indicates that death, severe personal injury or substantial property damage can result if proper

precautions are not taken.

!Caution

indicates that minor personal injury can result if proper precautions are not taken.

Caution

indicates that property damage can result if proper precautions are not taken.

Notice

draws your attention to particularly important information on the product, handling the product, or to a

particular part of the documentation.

Qualified Personnel

Only qualified personnel should be allowed to install and work on this equipment. Qualified persons are

defined as persons who are authorized to commission, to ground and to tag circuits, equipment, and

systems in accordance with established safety practices and standards.

Correct Usage

Note the following:

!Warning

This device and its components may only be used for the applications described in the catalog or the

technical description, and only in connection with devices or components from other manufacturers which

have been approved or recommended by Siemens.

This product can only function correctly and safely if it is transported, stored, set up, and installed

correctly, and operated and maintained as recommended.

Trademarks SIMATIC, SIMATIC HMIand SIMATIC NETare registered trademarks of SIEMENS AG.

Third parties using for their own purposes any other names in this document which refer to trademarks

might infringe upon the rights of the trademark owners.

Safety Guidelines

This manual contains notices intended to ensure personal safety, as well as to protect the products and

connected equipment against damage. These notices are highlighted by the symbols shown below and

graded according to severity by the following texts:

We have checked the contents of this manual for agreement

with the hardware and software described. Since deviations

cannot be precluded entirely, we cannot guarantee full

agreement. However, the data in this manual are reviewed

regularly and any necessary corrections included in

subsequent editions. Suggestions for improvement are

welcomed.

Disclaimof LiabilityCopyright W Siemens AG 2001 All rights reserved

The reproduction, transmission or use of this document or its

contents is not permitted without express written authority.

Offenderswill be liable for damages. All rights, including rights

created by patent grant or registration of a utility model or

design,are reserved.

Siemens AG

Bereich Automatisierungs- und Antriebstechnik

Geschaeftsgebiet Industrie-Automatisierungssysteme

Postfach 4848, D- 90327 Nuernberg SiemensAG 2001

Technical data subject to change.

Siemens Aktiengesellschaft A5E00111190