UG_1210F_035 73S1210F Evaluation Board User Guide

Rev. 1.2 3

Table of Contents

1Introduction ...................................................................................................................................4

1.1 Evaluation Kit Contents.........................................................................................................5

1.2 Evaluation Board Features....................................................................................................5

1.3 Recommended Equipment and Test Tools............................................................................5

2Evaluation Board Setup.................................................................................................................6

2.1 Connecting the Evaluation Board with an Emulation Tool......................................................7

2.2 Loading User Code into the Evaluation Board .......................................................................8

3Using the PCCID Application......................................................................................................10

3.1 Host Demonstration Software Installation............................................................................10

4Evaluation Board Hardware Description....................................................................................11

4.1 Jumpers, Switches and Modules.........................................................................................11

4.2 Test Points .........................................................................................................................16

4.3 Schematic...........................................................................................................................17

4.4 PCB Layouts.......................................................................................................................18

4.5 Bill of Materials ...................................................................................................................24

4.6 Schematic Information ........................................................................................................26

4.6.1 Reset Circuit..............................................................................................................26

4.6.2 Oscillator...................................................................................................................26

4.6.3 LCD ..........................................................................................................................27

4.6.4 Smart Card Interface .................................................................................................28

5Ordering Information...................................................................................................................29

6Related Documentation...............................................................................................................29

7Contact Information.....................................................................................................................29

Revision History..................................................................................................................................30

Figures

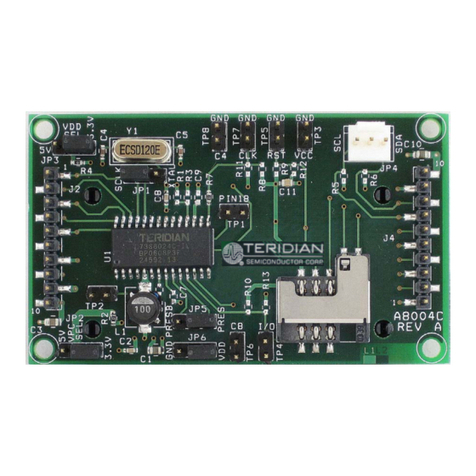

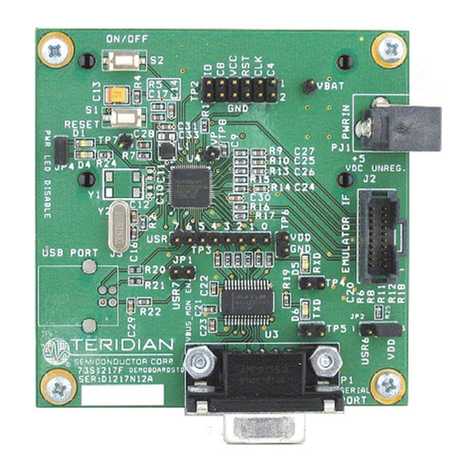

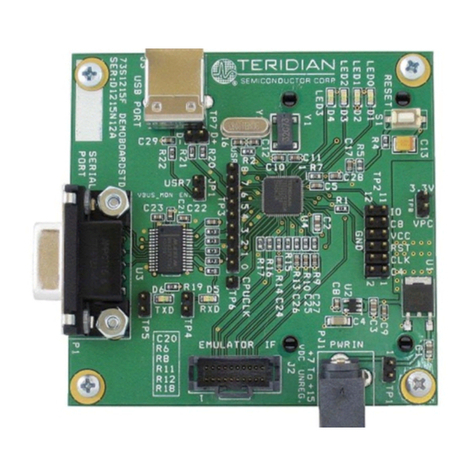

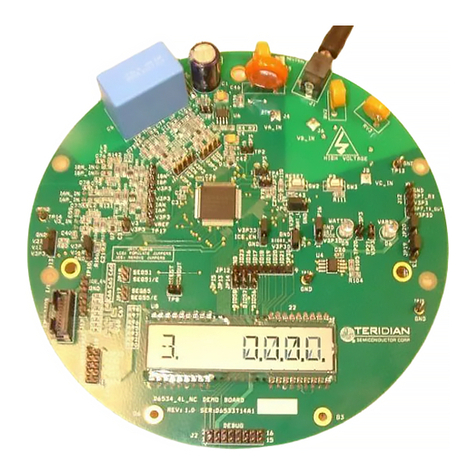

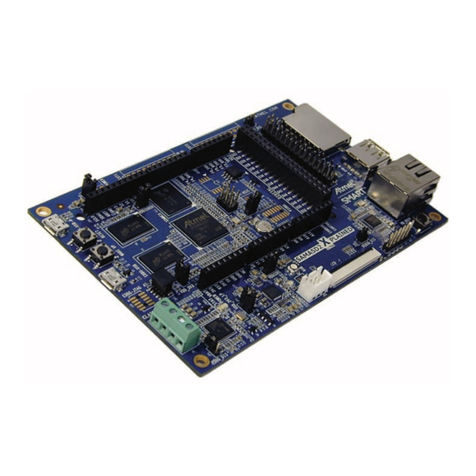

Figure 1: 1210F Evaluation Board............................................................................................................4

Figure 2: 73S1210F Evaluation Board Basic Connections........................................................................6

Figure 3: 73S1210F Evaluation Board Basic Connections with ADM-51 ICE............................................7

Figure 4: EmulatorWindow Showing RESETand ERASE Buttons...........................................................9

Figure 5: Emulator Window Showing Erased Flash Memory and File Load Menu.....................................9

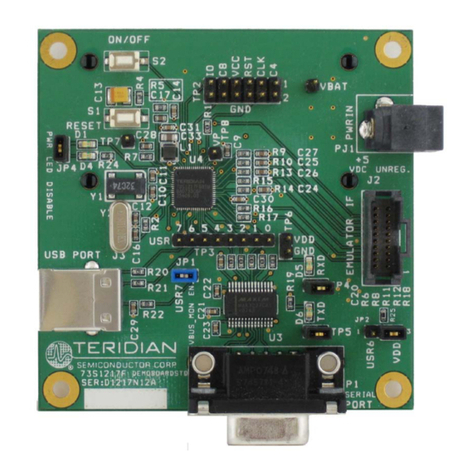

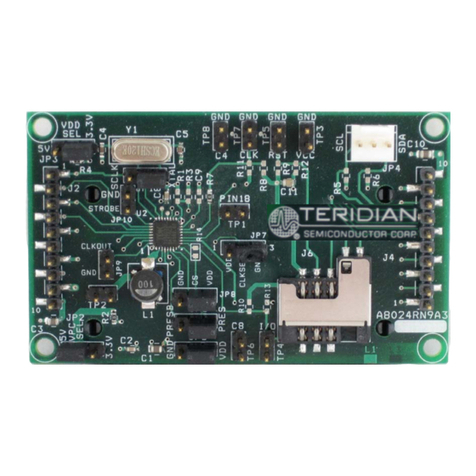

Figure 6: 73S1210F Evaluation Board Jumper, Switch and Module Locations........................................15

Figure 7: 73S1210F Evaluation Board Electrical Schematic ...................................................................17

Figure 8: 73S1210F Evaluation Board Top View (Silkscreen).................................................................18

Figure 9: 73S1210F Evaluation Board Bottom View (Silkscreen)............................................................19

Figure 10: 73S1210F Evaluation Board Top Signal Layer ......................................................................20

Figure 11: 73S1210F Evaluation Board Middle Layer 1 – Ground Plane.................................................21

Figure 12: 73S1210F Evaluation Board Middle Layer 2 – Supply Plane .................................................22

Figure 13: 73S1210F Evaluation Board Bottom Signal Layer .................................................................23

Figure 14: External Components for RESET..........................................................................................26

Figure 15: Oscillator Circuit....................................................................................................................26

Figure 16: LCD Connections..................................................................................................................27

Figure 17: Smart Card Connections.......................................................................................................28

Tables

Table 1: Flash Programming Interface Signals.........................................................................................8

Table 2: Evaluation Board Jumper, Switch and Module Description .......................................................11

Table 3: Evaluation Board Test Point Description...................................................................................16

Table 4: 73S1210F Evaluation Board Bill of Materials............................................................................24

Downloaded from Arrow.com.Downloaded from Arrow.com.Downloaded from Arrow.com.