73S8023C Demo Board User Manual UM_8023C_027

4 Rev. 1.3

Figures

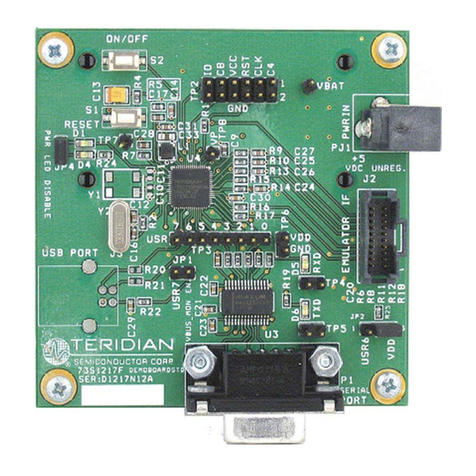

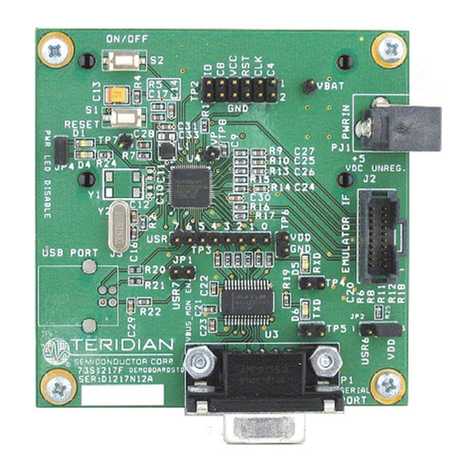

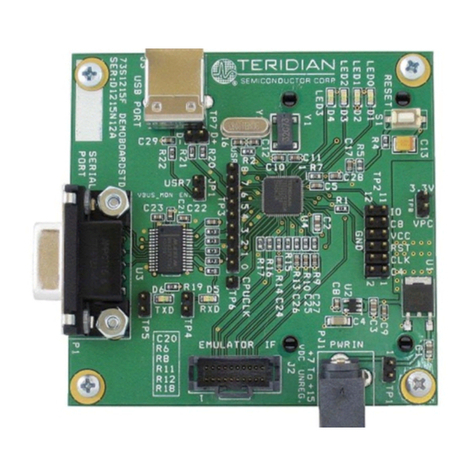

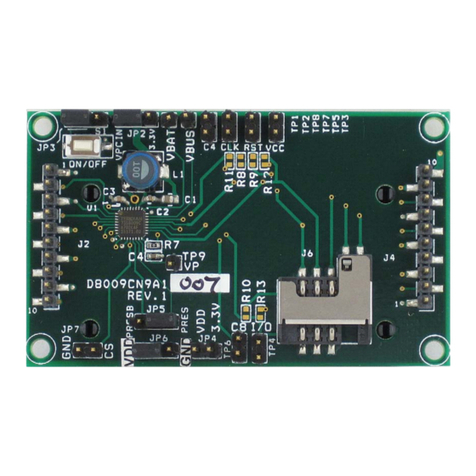

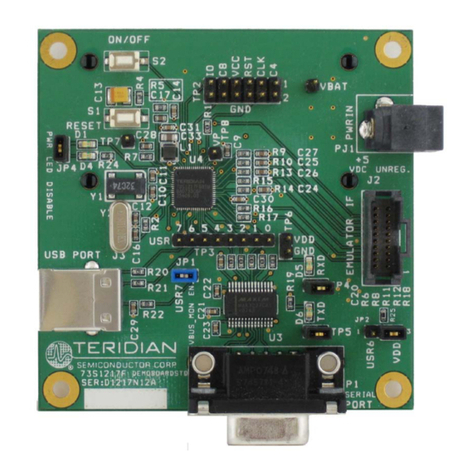

Figure 1: 73S8023C Demo Board............................................................................................................5

Figure 2: 73S8023C Demo Board Basic Connections..............................................................................6

Figure 3: 73S8023C Demo Board Connectors, Jumpers and Test Points.................................................8

Figure 4: 73S8023C 32QFN Pinout (Top View)......................................................................................11

Figure 5: 73S8023C Demo Board Electrical Schematic..........................................................................13

Figure 6: 73S8023C Demo Board Top View...........................................................................................15

Figure 7: 73S8023C Demo Board Bottom View......................................................................................15

Figure 8: 73S8023C Demo Board Top Signal Layer...............................................................................16

Figure 9: 73S8023C Demo Board Middle Layer 1, Ground Plane...........................................................16

Figure 10: 73S8023C Middle Layer 2, Supply Plane ..............................................................................17

Figure 11: 73S8023C Demo Board Bottom Signal Layer........................................................................17

Tables

Table 1: 73S8023C Demo Board Connector, Jumper and Test Points......................................................7

Table 2: Recommended Operating Conditions.........................................................................................9

Table 3: Absolute Maximum Ratings........................................................................................................9

Table 4: 73S8023C Card Interface Pins...................................................................................................9

Table 5: 73S8023C Miscellaneous Pins.................................................................................................10

Table 6: 73S8023C Power and Ground Pins..........................................................................................10

Table 7: 72S8023C Microcontroller Interface Pins..................................................................................10

Table 8: 73S8023C Demo Board Bill of Materials...................................................................................14

Table 9: Order Numbers and Packaging Marks......................................................................................18