2SLAU320Z–July 2010–Revised July 2017

Submit Documentation Feedback

Copyright © 2010–2017, Texas Instruments Incorporated

Contents

Contents

Preface ........................................................................................................................................ 5

1 Programming Using the JTAG Interface.................................................................................. 6

1.1 Introduction ................................................................................................................... 6

1.1.1 MSP430 JTAG Restrictions (Noncompliance With IEEE Std 1149.1)....................................... 6

1.1.2 TAP Controller State Machine .................................................................................... 6

1.2 Interface and Instructions................................................................................................... 7

1.2.1 JTAG Interface Signals ............................................................................................ 7

1.2.2 JTAG Access Macros .............................................................................................. 8

1.2.3 Spy-Bi-Wire (SBW) Timing and Control ....................................................................... 11

1.2.4 JTAG Communication Instructions.............................................................................. 16

1.3 Memory Programming Control Sequences ............................................................................. 22

1.3.1 Start-Up............................................................................................................. 22

1.3.2 General Device (CPU) Control Functions...................................................................... 25

1.3.3 Accessing Non-Flash Memory Locations With JTAG ........................................................ 34

1.3.4 Programming the Flash Memory (Using the Onboard Flash Controller)................................... 39

1.3.5 Erasing the Flash Memory (Using the Onboard Flash Controller).......................................... 45

1.3.6 Reading From Flash Memory.................................................................................... 49

1.3.7 Verifying the Target Memory..................................................................................... 49

1.3.8 FRAM Memory Technology...................................................................................... 52

1.4 JTAG Access Protection .................................................................................................. 53

1.4.1 Burning the JTAG Fuse - Function Reference for 1xx, 2xx, 4xx Families................................. 54

1.4.2 Programming the JTAG Lock Key - Function Reference for 5xx, 6xx, and FRxx Families ............. 56

1.4.3 Testing for a Successfully Protected Device .................................................................. 57

1.4.4 Unlocking a Password-Protected Device ...................................................................... 58

1.4.5 Memory Protection Unit Handling............................................................................... 59

1.4.6 Intellectual Property Encapsulation (IPE) ...................................................................... 59

1.4.7 FRAM Write Protection........................................................................................... 59

1.5 JTAG Function Prototypes................................................................................................ 60

1.5.1 Low-Level JTAG Functions ...................................................................................... 60

1.5.2 High-Level JTAG Routines....................................................................................... 61

1.6 JTAG Features Across Device Families ................................................................................ 64

1.7 References.................................................................................................................. 75

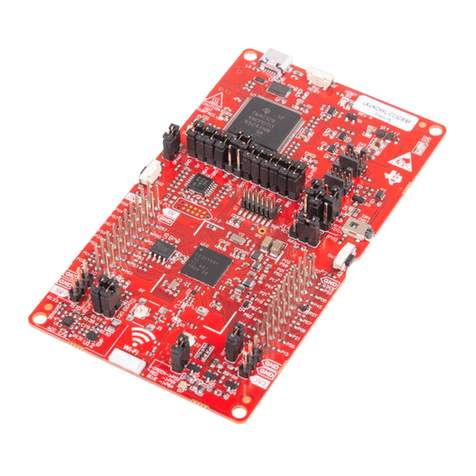

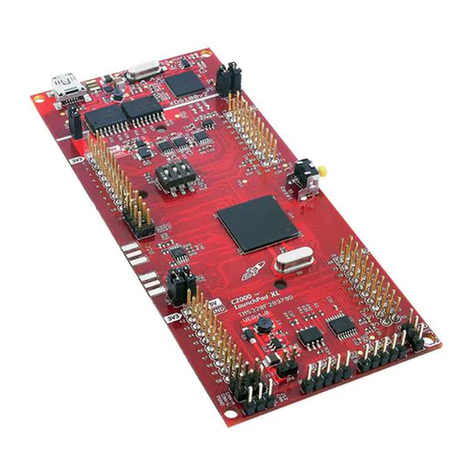

2 JTAG Programming Hardware and Software Implementation................................................... 76

2.1 Implementation History .................................................................................................... 76

2.2 Implementation Overview ................................................................................................. 76

2.3 Software Operation ........................................................................................................ 77

2.4 Software Structure ......................................................................................................... 77

2.4.1 Programmer Firmware............................................................................................ 77

2.4.2 Target Code........................................................................................................ 79

2.5 Programmer Operation .................................................................................................... 80

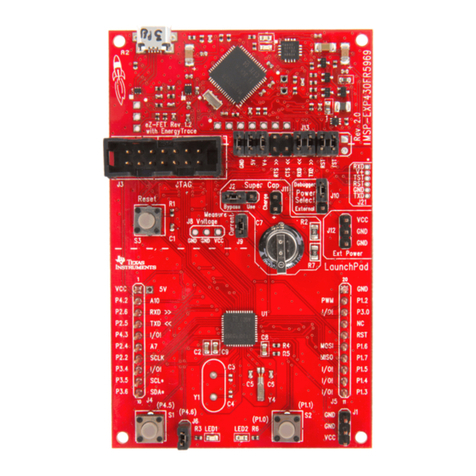

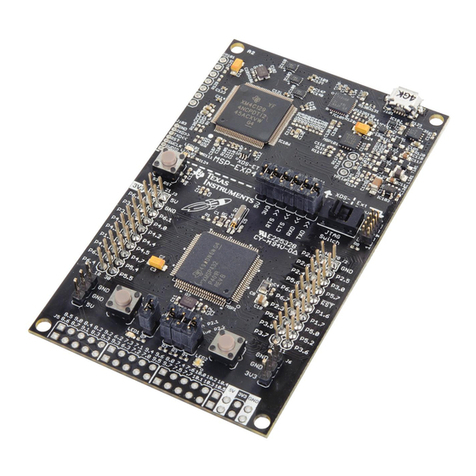

2.6 Hardware Setup ............................................................................................................ 80

2.6.1 Host Controller..................................................................................................... 80

2.6.2 Target Connection................................................................................................. 80

2.6.3 Host Controller or Programmer Power Supply ................................................................ 83

2.6.4 Third-Party Support ............................................................................................... 83