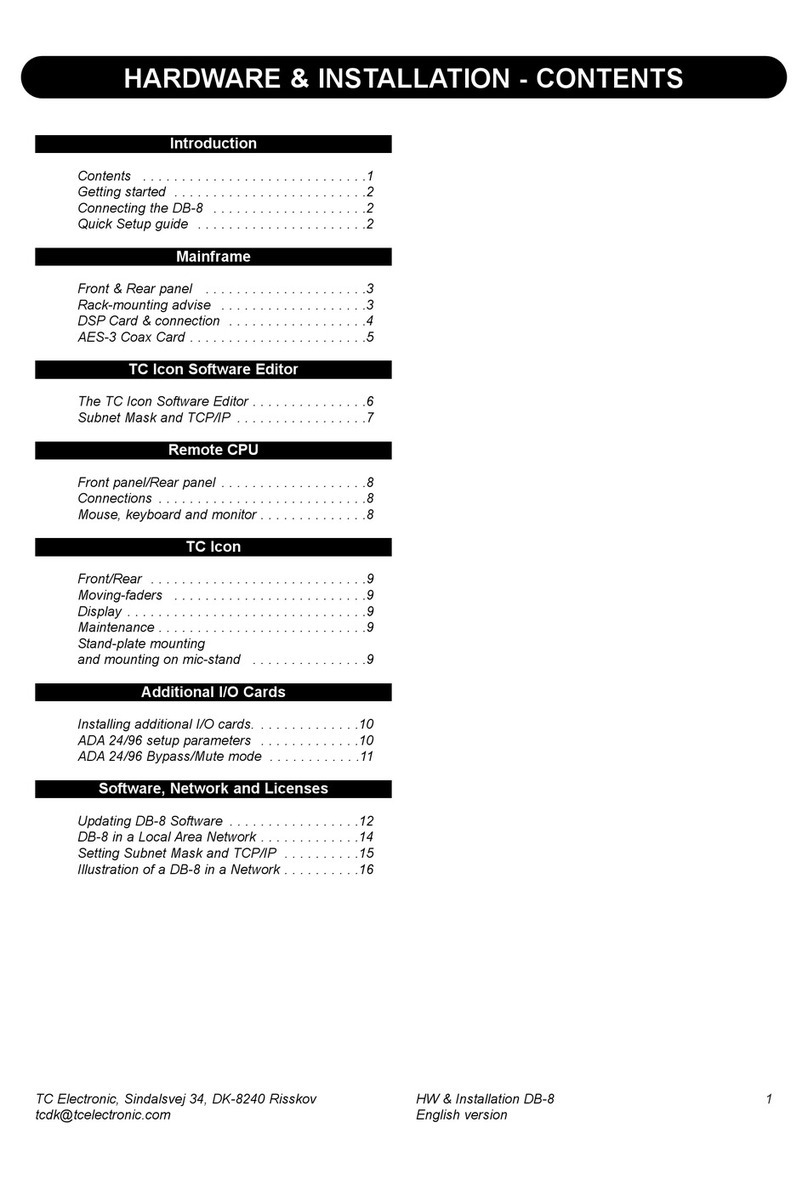

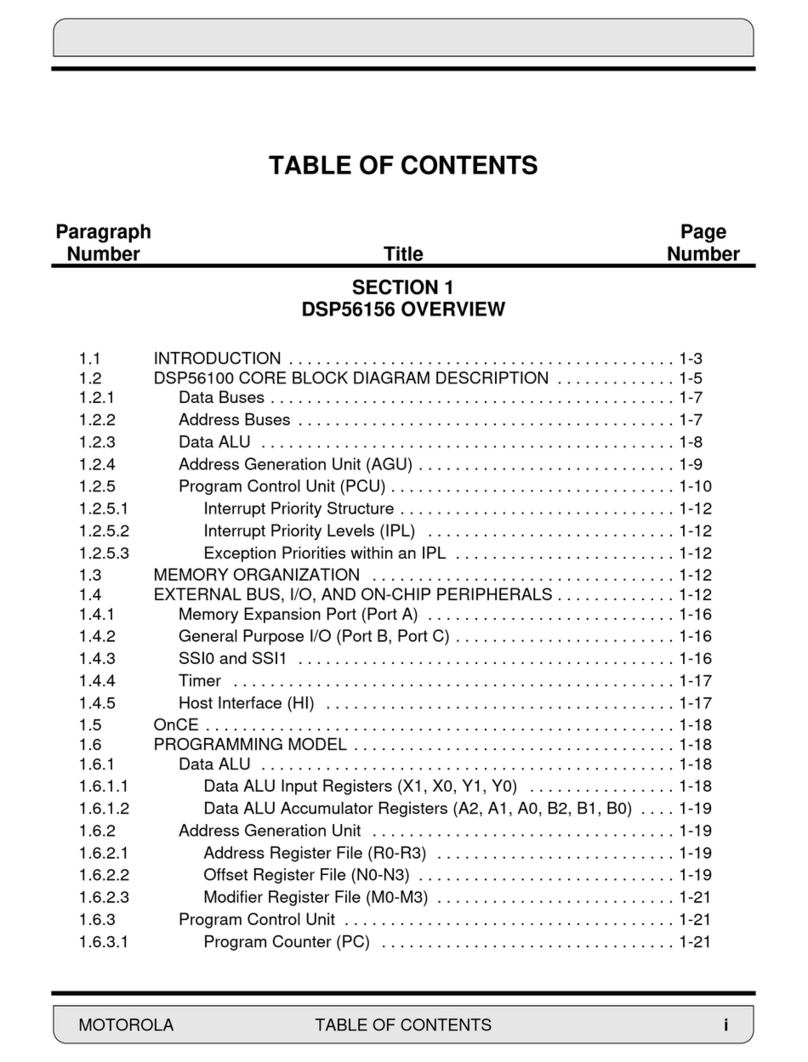

Contents

x

3 TMS320C62x/C67x Fixed-Point Instruction Set 3Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the assembly language instructions that are common to both the TMS320C62x and

TMS320C67x, including examples of each instruction. Provides information about addressing

modes, resource constraints, parallel operations, and conditional operations.

3.1 Instruction Operation and Execution Notations 3Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.2 Mapping Between Instructions and Functional Units 3Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.3 TMS320C62x/C67x Opcode Map 3Ć9. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.4 Delay Slots 3Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5 Parallel Operations 3Ć13. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.1 Example Parallel Code 3Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.5.2 Branching Into the Middle of an Execute Packet 3Ć15. . . . . . . . . . . . . . . . . . . . . . . .

3.6 Conditional Operations 3Ć16. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7 Resource Constraints 3Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.1 Constraints on Instructions Using the Same Functional Unit 3Ć17. . . . . . . . . . . . . .

3.7.2 Constraints on Cross Paths (1X and 2X) 3Ć17. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.3 Constraints on Loads and Stores 3Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.4 Constraints on Long (40-Bit) Data 3Ć18. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.5 Constraints on Register Reads 3Ć19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7.6 Constraints on Register Writes 3Ć19. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8 Addressing Modes 3Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.1 Linear Addressing Mode 3Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.2 Circular Addressing Mode 3Ć21. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8.3 Syntax for Load/Store Address Generation 3Ć23. . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.9 Individual Instruction Descriptions 3Ć24. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4 TMS320C67x Floating-Point Instruction Set 4Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes the TMS320C67x floating-point instruction set, including examples of each

instruction. Provides information about addressing modes and resource constraints.

4.1 Instruction Operation and Execution Notations 4Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.2 Mapping Between Instructions and Functional Units 4Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.3 Overview of IEEE Standard Single- and Double-Precision Formats 4Ć6. . . . . . . . . . . . . . . .

4.4 Delay Slots 4Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.5 TMS320C67x Instruction Constraints 4Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

4.6 Individual Instruction Descriptions 4Ć15. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5 TMS320C62x Pipeline 5Ć1. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

Describes phases, operation, and discontinuities for the TMS320C62x CPU pipeline.

5.1 Pipeline Operation Overview 5Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.1 Fetch 5Ć2. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.2 Decode 5Ć4. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.3 Execute 5Ć5. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.1.4 Summary of Pipeline Operation 5Ć6. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2 Pipeline Execution of Instruction Types 5Ć11. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5.2.1 Single-Cycle Instructions 5Ć12. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .