Not Recommended for New Designs NRND

3

CC1021

www.ti.com

SWRS045F –JANUARY 2006–REVISED NOVEMBER 2018

Submit Documentation Feedback

Product Folder Links: CC1021

Revision HistoryCopyright © 2006–2018, Texas Instruments Incorporated

Table of Contents

1 Device Overview ......................................... 1

1.1 Features .............................................. 1

1.2 Applications........................................... 1

1.3 Description............................................ 1

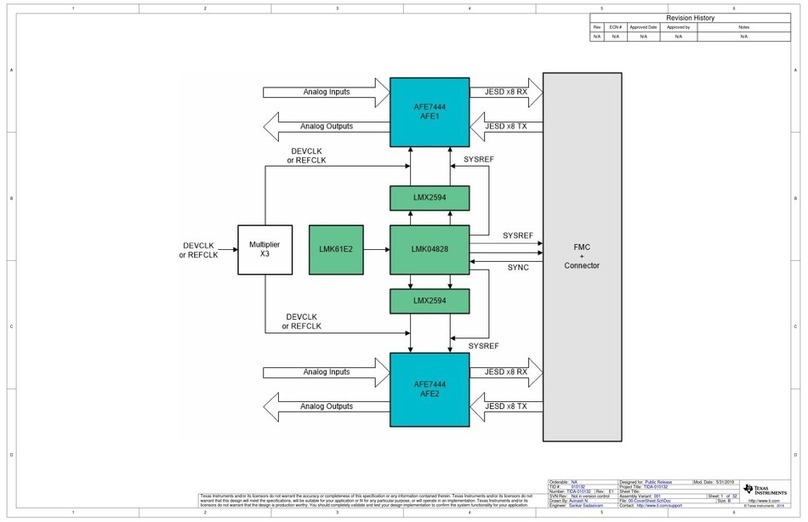

1.4 Functional Block Diagram ............................ 2

2 Revision History ......................................... 3

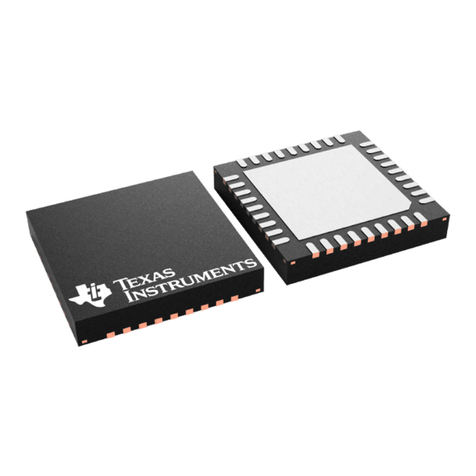

3 Terminal Configuration and Functions.............. 4

3.1 Pin Diagram .......................................... 4

3.2 Pin Configuration ..................................... 4

4 Specifications ............................................ 6

4.1 Absolute Maximum Ratings .......................... 6

4.2 ESD Ratings.......................................... 6

4.3 Recommended Operating Conditions................ 6

4.4 RF Transmit .......................................... 6

4.5 RF Receive........................................... 8

4.6 RSSI / Carrier Sense................................ 10

4.7 Intermediate Frequency (IF) ........................ 11

4.8 Crystal Oscillator.................................... 11

4.9 Frequency Synthesizer.............................. 12

4.10 Digital Inputs / Outputs.............................. 12

4.11 Current Consumption ............................... 13

4.12 Thermal Resistance Characteristics for VQFNP

Package ............................................. 14

5 Detailed Description ................................... 15

5.1 Overview ............................................ 15

5.2 Functional Block Diagram........................... 15

5.3 Configuration Overview ............................. 16

5.4 Microcontroller Interface............................. 17

5.5 4-wire Serial Configuration Interface................ 18

5.6 Signal Interface...................................... 20

5.7 Data Rate Programming ............................ 22

5.8 Frequency Programming............................ 24

5.9 Receiver............................................. 25

5.10 Transmitter .......................................... 38

5.11 Input and Output Matching and Filtering............ 40

5.12 Frequency Synthesizer.............................. 44

5.13 VCO and LNA Current Control...................... 48

5.14 Power Management................................. 48

5.15 On-Off Keying (OOK) ............................... 50

5.16 Crystal Oscillator.................................... 51

5.17 Built-in Test Pattern Generator ..................... 53

5.18 Interrupt on Pin DCLK............................... 54

5.19 PA_EN and LNA_EN Digital Output Pins ........... 54

5.20 System Considerations and Guidelines............. 55

5.21 Antenna Considerations............................. 58

5.22 Configuration Registers ............................. 59

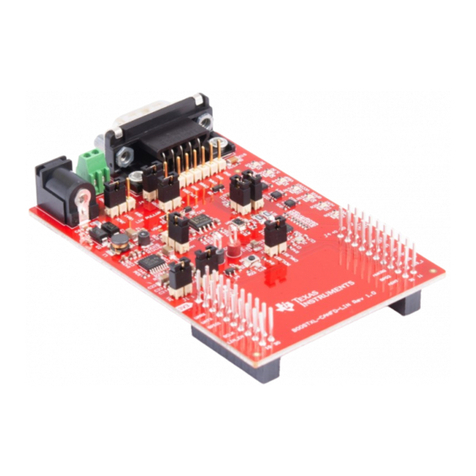

6 Applications, Implementation, and Layout........ 78

6.1 Application Information.............................. 78

6.2 Design Requirements ............................... 80

6.3 PCB Layout Guidelines ............................. 81

7 Device and Documentation Support ............... 82

7.1 Device Support...................................... 82

7.2 Documentation Support ............................. 82

7.3 Trademarks.......................................... 83

7.4 Electrostatic Discharge Caution..................... 83

7.5 Export Control Notice ............................... 83

7.6 Glossary............................................. 83

8 Mechanical Packaging and Orderable

Information .............................................. 83

8.1 Packaging Information .............................. 83

2 Revision History

Changes from August 20, 2016 to November 30, 2018 Page

• Global: Changed upper frequency from 960 MHz to 930 MHz................................................................. 1

• Global: Removed references to ARIB STD-T96.................................................................................. 1