ASAHI KASEI [AKD4633-A]

<KM079407> 2016/10

- 2 -

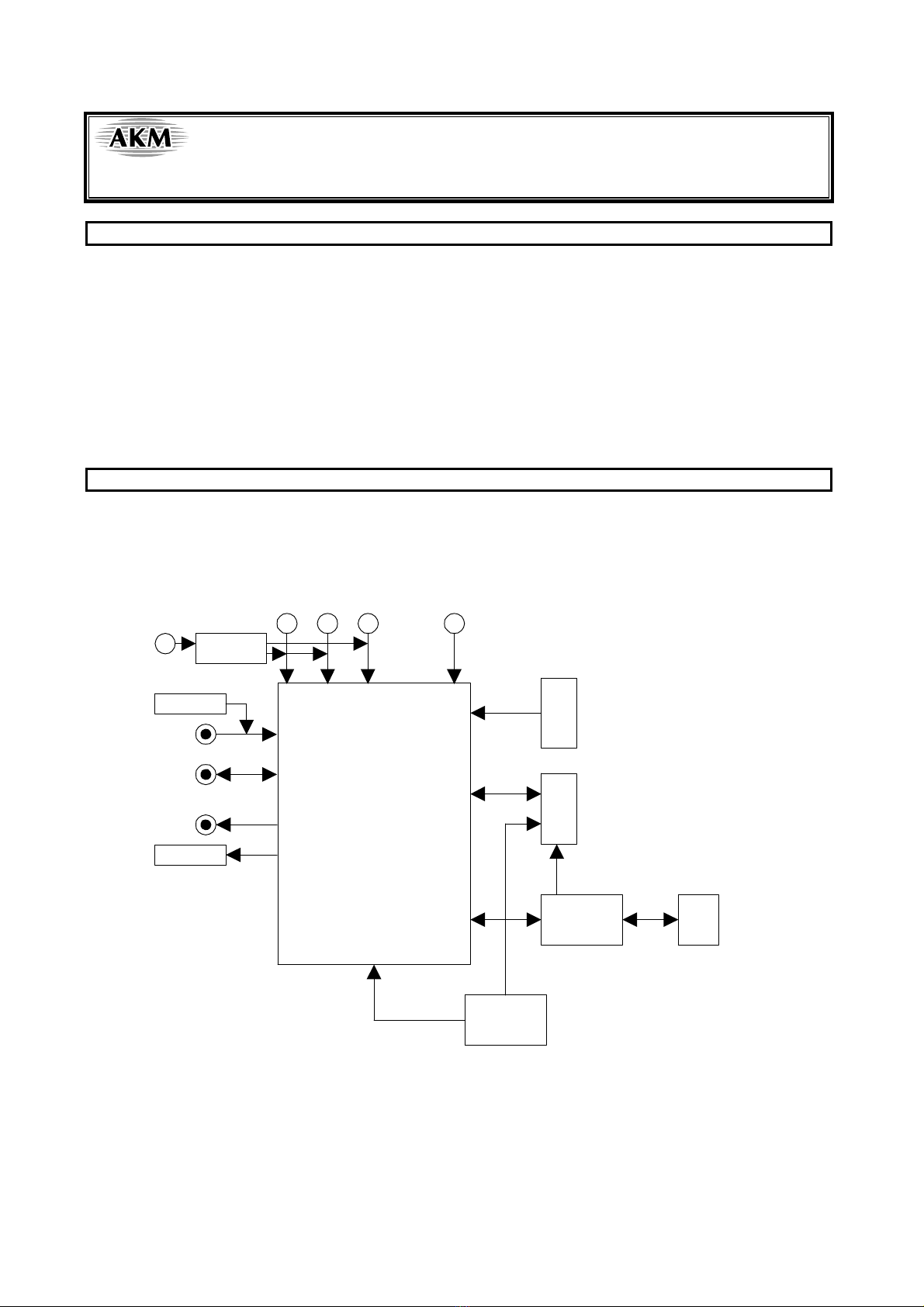

Evaluation Board Manual

Operation sequence

1) Set up the power supply lines.

1-1) When AVDD,DVDD, SVDD, and VCCare supplied from the regulator. (AVDD, DVDD, SVDD, and VCC

jack should be open.). See “Other jumper pins set up (page 10)”. <default>

[REG] (red ) = 5V

[AVDD] (orange) = open : 3.3V is supplied to AVDD of AK4633VN from regulator.

[DVDD] (orange) = open : 3.3V is supplied to DVDD of AK4633VN from regulator.

[SVDD](blue) = open : 3.3V is supplied to SVDD of AK4633VN from regulator.

[VCC] (orenge) = open : 3.3V is supplied to logic block from regulator.

[AVSS] (black) = 0V : for analog ground

[AGND] (black) = 0V : for analog ground

[DGND] (black) = 0V : for logic ground

1-2) When AVDD, DVDD, SVDD, and VCC are not supplied from the regulator. (AVDD, DVDD, SVDD, and

VCC jack should be junction.) See “Other jumper pins set up (page 10)”.

[REG] (red) = “REG” jack should be open.

[AVDD] (orange) = 2.6 3.6V : for AVDD of AK4633VN (typ. 3.3V)

[DVDD] (orange) = 2.6 3.6V : for DVDD of AK4633VN (typ. 3.3V)

[SVDD] (blue) = 2.6 5.25V: for SVDD of AK4633VN (typ. 3.3V, 5.0V)

[VCC] (orenge) = 2.6 3.6V : for logic (typ. 3.3V)

[AVSS] (black) = 0V : for analog ground

[AGND] (black) = 0V : for analog ground

[DGND] (black) = 0V : for logic ground

Each supply line should be distributed from the power supply unit.

AVDD and DVDD must be same voltage level.

2) Set up the evaluation mode, jumper pins and DIP switches. (See the followings.)

3) Power on.

The AK4633VN and AK4114 should be reset once bringing SW1, 2 “L” upon power-up.

Evaluation mode

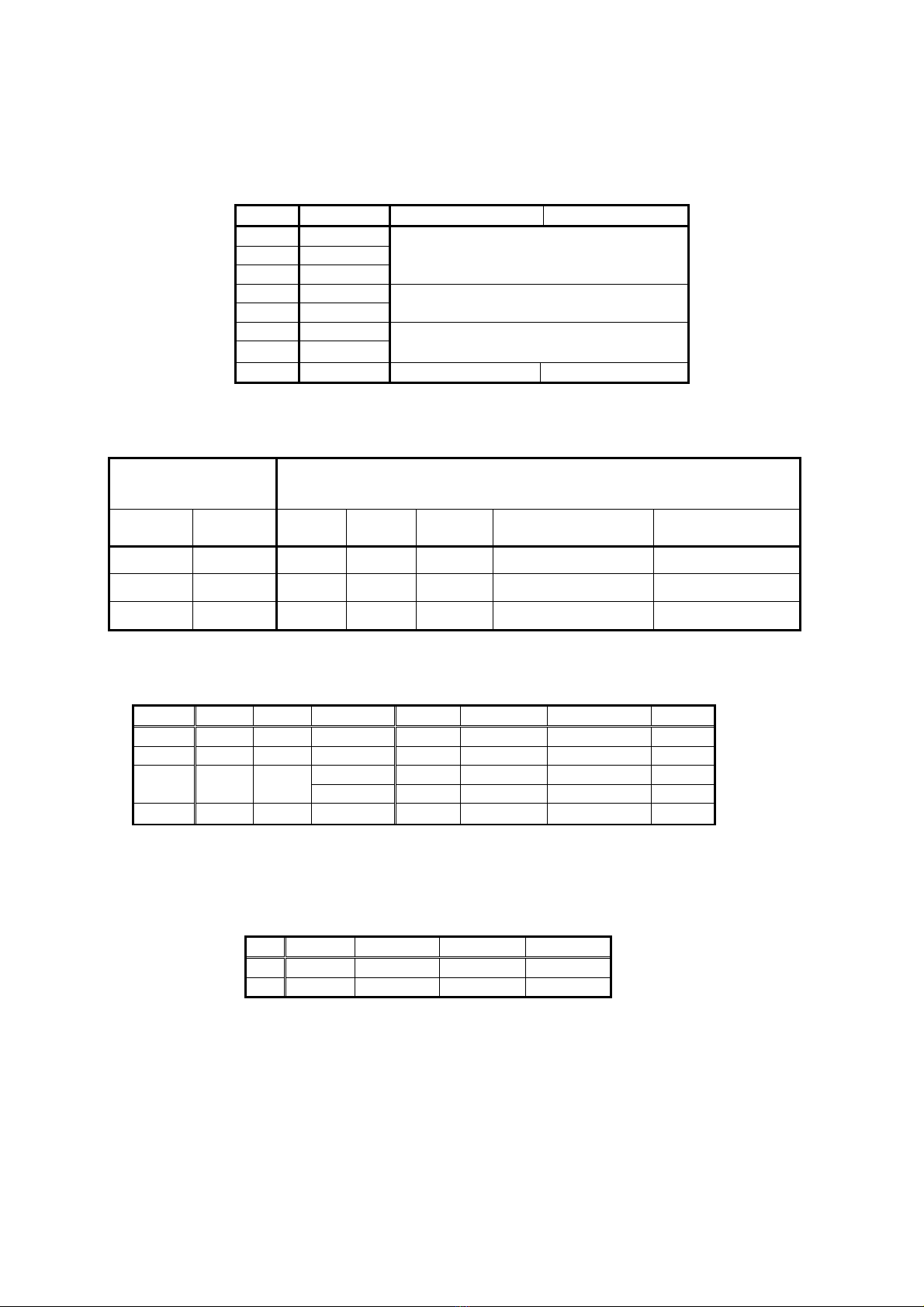

In case of AK4633VN evaluation using AK4114, it is necessary to correspond to audio interface format for

AK4633VN and AK4114. About AK4633VN’s audio interface format, refer to datasheet of AK4633VN.

About AK4114’s audio interface format, refer to Table 2 in this manual.

Applicable Evaluation Mode

(1) Evaluation of loop-back mode (A/D D/A) : PLL, Master Mode

(2) Evaluation of loop-back mode (A/D D/A) : PLL, Slave Mode (PLL Reference CLOCK: MCKI

pin)

(3) Evaluation of loop-back mode (A/D D/A) : PLL, Slave Mode (PLL Reference CLOCK: BICK or

FCK pin)

(4) Evaluation of using DIR of AK4114 (opt-connector) : EXT, Slave Mode

(5) Evaluation of using DIT of AK4114 (opt-connector) : EXT, Slave Mode