[AKD5367A-A]

<KM095000> 2008/06

- 2 -

Operation Sequence

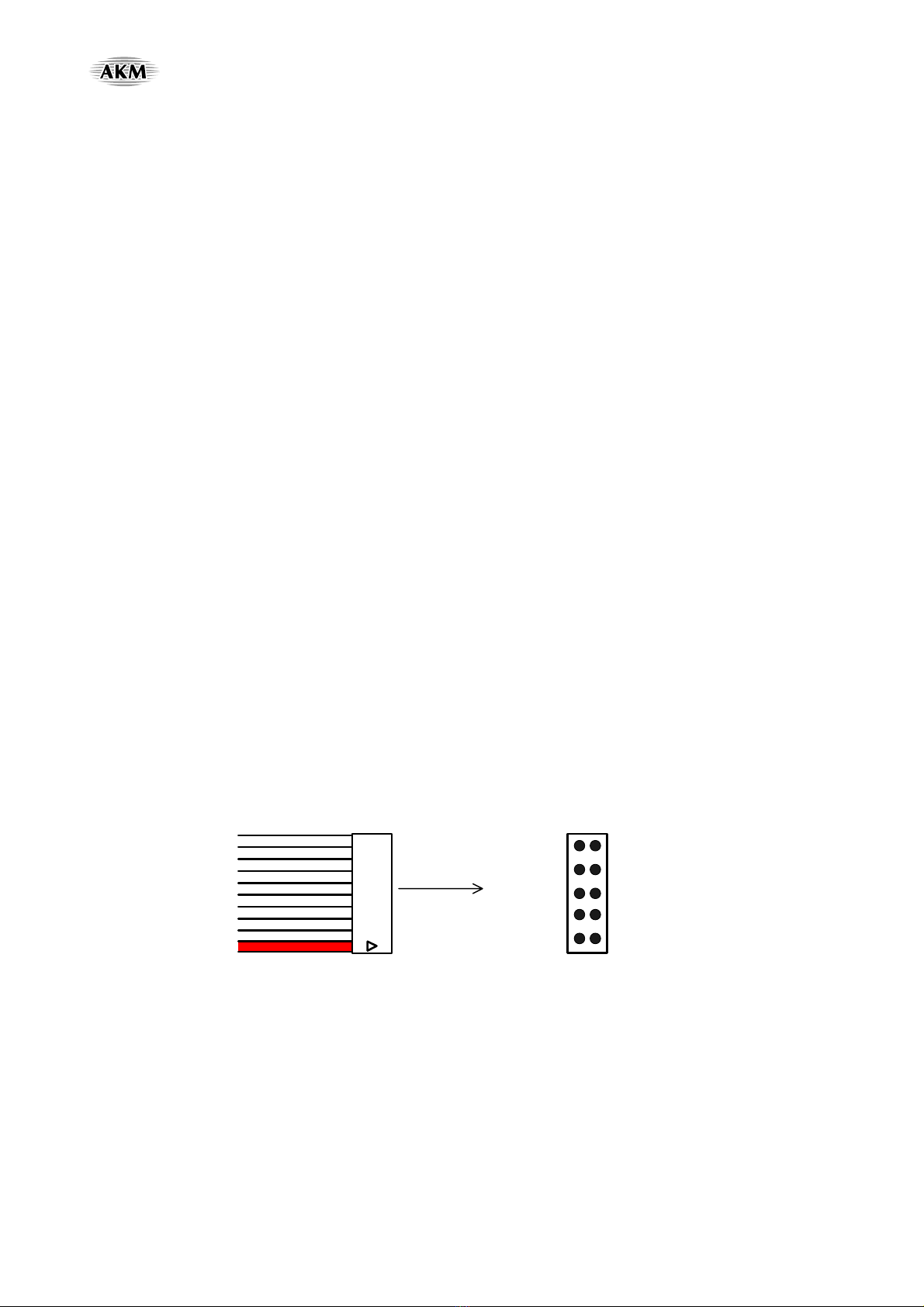

1) Set up the power supplies lines. (Note 1)

Connector

name Connector

color Voltage Used for Comment and attention Default

Setting

AVDD Orange

+4.75~+5.25

V AVDD for AK5367A,

Regulator T1. This connector must be connected.

+5V

DVDD Red +3.0~+3.6V DVDD for AK5367A This connector is used when DVDD of AK5367A is

supplied from DVDD connector without regulator T1.

In this case, JP2 should be open. (Default) +3.3V

CVDD Red +3.0~+3.6V CVDD for AK5367A This connector is used when CVDD of AK5367A is

supplied from CVDD connector without regulator T1.

In this case, JP3 should be open. (Default) +3.3V

D3V Red +3.0~+3.6V

AK4104,

Logic circuit

This connector is used when power of AK4104 and

logic circuit is supplied from +3.3V connector without

regulator T1. In this case, JP4 should be open. (Default) +3.3V

AGND Black 0V Analog ground This connector must be connected. 0V

DGND Black 0V Digital ground This connector is used when DGND is supplied

separately from AGND. In this case, JP1 should be

open. (Default) 0V

Table 1. Power Supply Lines

Note 1. Each supply line should be distributed from the power supply unit.

2) Set up the evaluation mode, jumper pins and DIP switches. (See the followings.)

3) Power on.

The AK5367A and AK4104 should be reset once bringing SW1 and SW2 = “L” and return it to “H” to upon

power-up.

Evaluation Mode

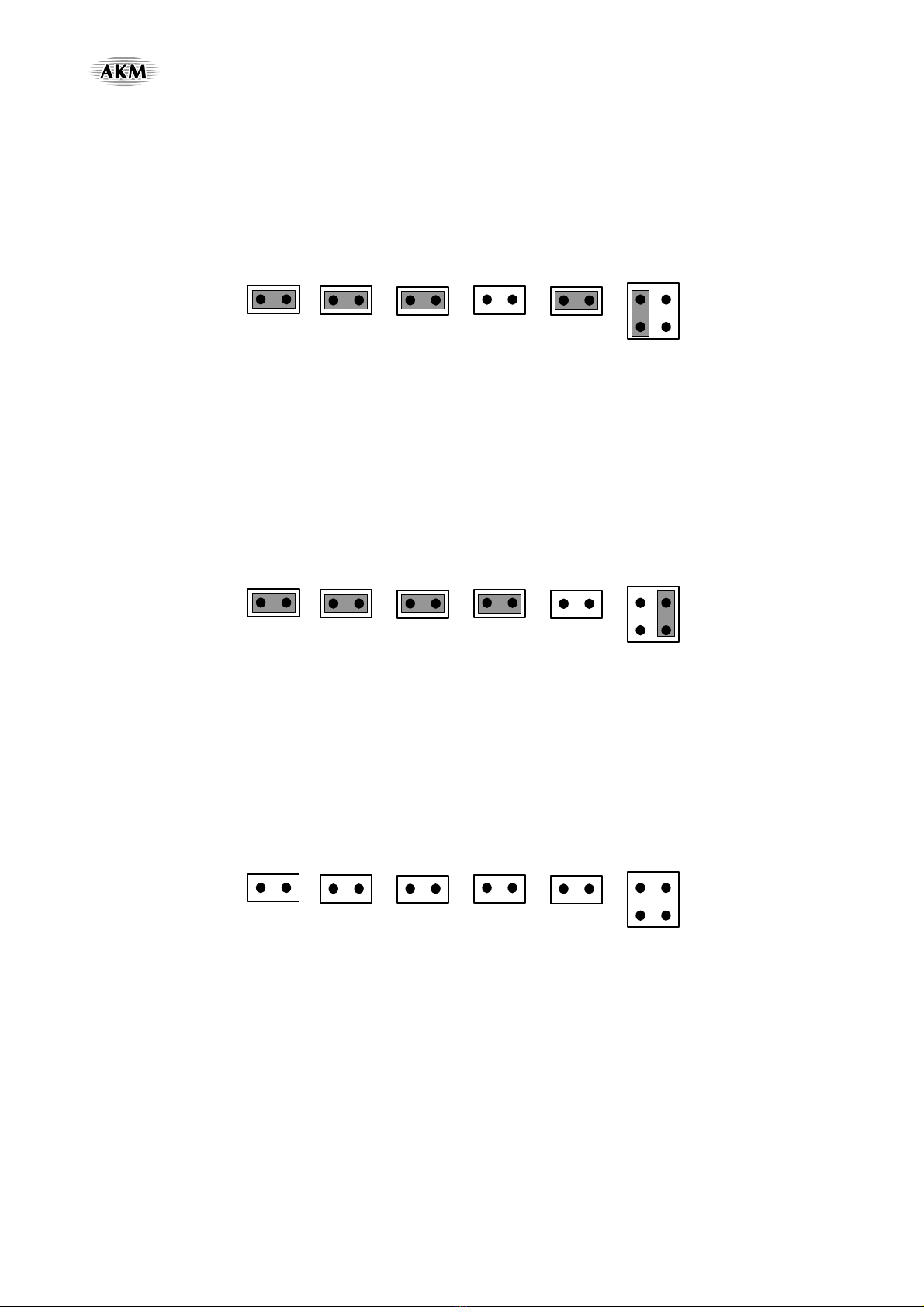

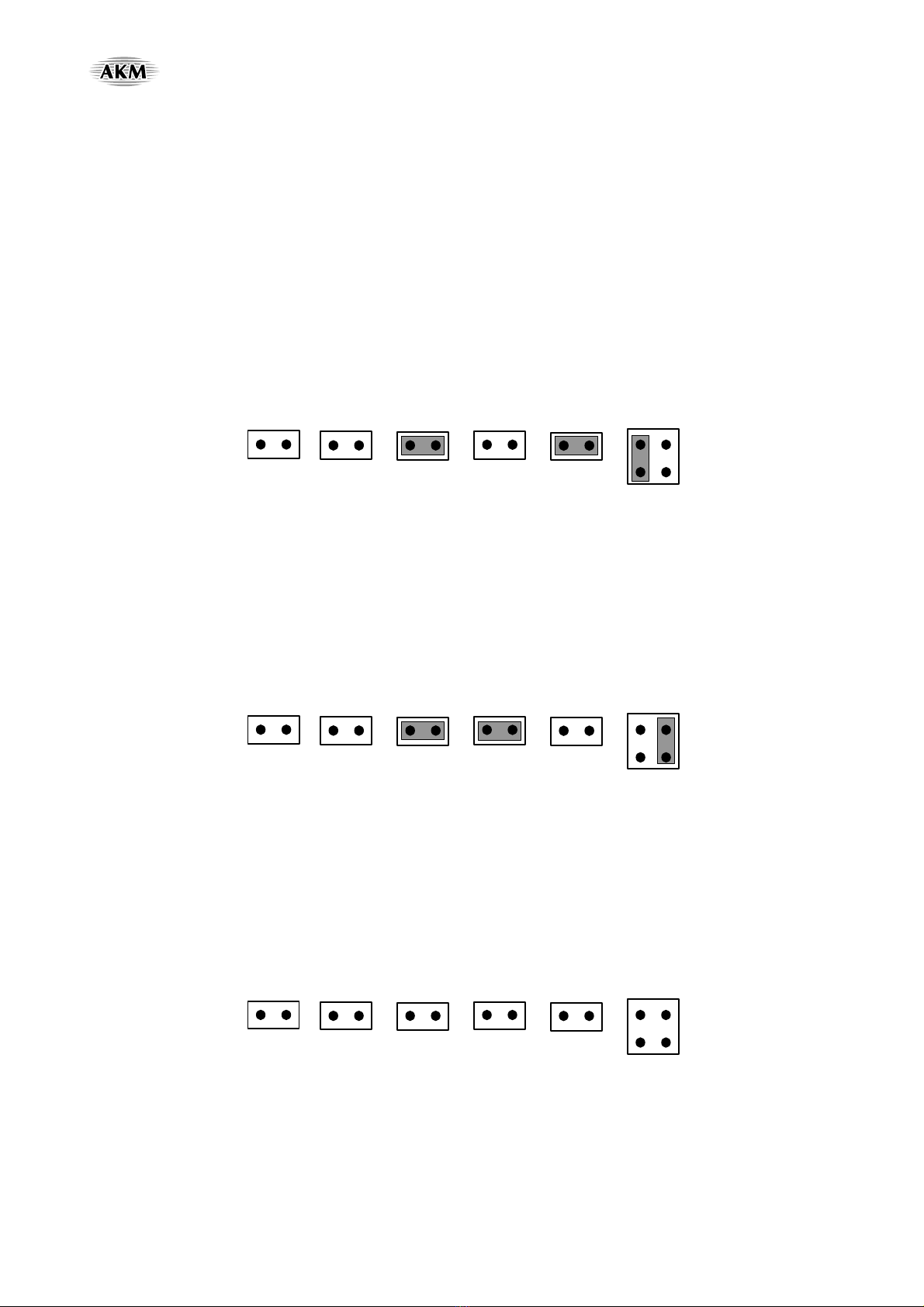

(1)Slave mode

When evaluating the AK5367A using the AK4104, the setting of the AK5367A’s audio interface format

should be the same as the AK4104’s format. When the AK4104 is used, the audio interface format is the

default setting of 16/24bit I2S compatible. Therefore, set DIF bit=”1” to agree with the AK4104’s format.

(1-1) A/D evaluation using AK4104 DIT function

PORT1 (DIT) is used. DIT generates audio bi-phase signal from received data and it is output through optical

connector (TOTX141). It is possible to connect AKEMD’s D/A converter evaluation boards on the

digital-amplifier. The clock can be generated from crystal oscillator X1 or be input from J11 (BNC) or PORT2

(ROM).