[AKD7600-A]

< KM091700> 2008/04

- 3 -

(5) AK7600VF (U10)

This device is a CODEC (2ch ADC, 6ch DAC) with a delay line memory and digital filters such as EQ. It operates

in master mode and the internal sampling rate is 44.1 kHz.

(6) PIC18F4550 (U11)

USB control chip. It is possible to set up the registers of AK7600VF and AK4114 from PC via the USB port.

(7) SW1

Push type button. It is used to initialize the PIC18F4550. When connecting the board to PC, it is required to push

down the button for initialization.

(8) Clock (X’tal1~3, BNC, U10 and internal clock of U11)

The setting of jumper pins is according to ‘Evaluation mode’ set-up.

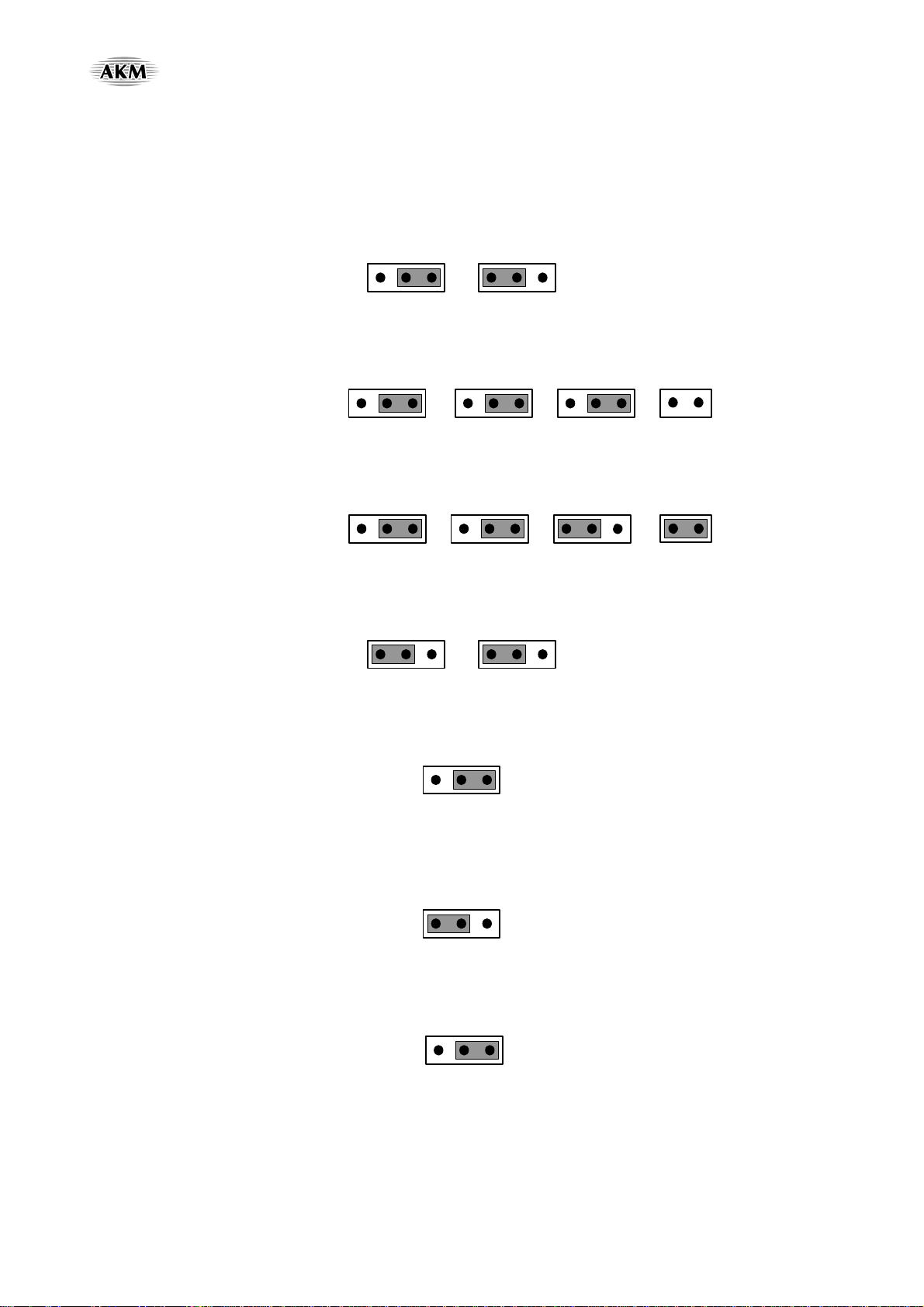

(9) Function setup

According to following tables (Table 4~Table 7)

(10) LED(DZF)

This is the sign of output for DZF pin.

(11) USB PORT(U13)

A computer can control AK7600VF and AK4114 on this board by the AK7600 control software through this USB

port.

Evaluation Board Manual

Operation sequence

1) Set up Power Supplies (The power should be separated from the source of a power supplier.)

Name of

connector Color of

connector Voltage Used for Comment and attention Default

Setting

+12V Red +12V

Regulator REG1,

Regulator REG2,

Regulator REG3,

OP-Amplifiers

Make sure to be connected by +12V power

supplier. And this connector is used when AVDD

and DVDD(5V-C) of AK7600VF are supplied

from regulator REG1.

And DVDD(3.3V), DVDD(5V) of AK7600VF are

supplied from regulator REG2 and REG3. In this

case, JP18 and JP19 should be SHORT. (Default)

When JP18 is open, the orange connector (J2)

should be supplied +5V.

+12V

-12V Blue -12V OP-Amplifier

This connector should be connected by -12V power

supplier. -12V

+5V

(J2) Orange +4.5 ~

+5.5V

AVDD and

DVDD(5V-C) of

AK7600VF,

Analog input

buffercircuit

This connector is used when AVDD and

DVDD (5V-C) of AK7600VF is power supplied

+5V without regulators. In this case, J18 should be

OPEN.

Open

AGND Black 0V Analog ground

Make sure to be connected by the ground

connection. 0V

DGND Black 0V Digital ground

This connector is used when DGND is supplied

seperatly with AGND. In this case, WIRE1 should

be open. (Default)

0V

Table 1 Power supply lines