[AKD4637-B]

<KM120603> 2018/10

- 3 -

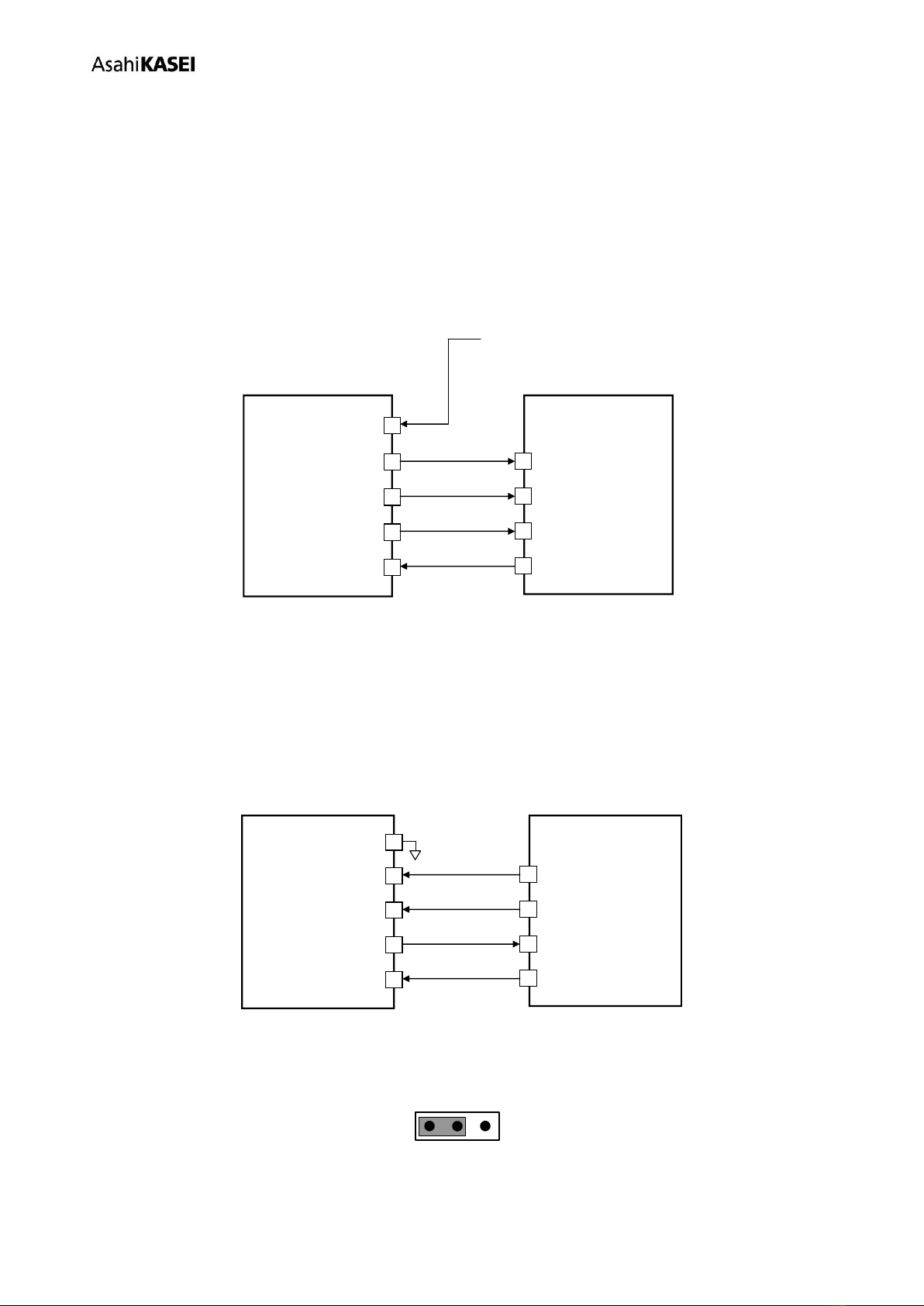

Evaluation mode

In case of using the AK4118A when evaluating the AK4637, audio interface format of both devices must be matched.

Refer to the datasheet for audio interface format of the AK4637, and Table 2 for audio interface format of the

AK4118A.

The AK4118A operates at fs of 32kHz or more. If the fs is slower than 32kHz, please use other mode.

In addition, MCLK of AK4118A supports 256fs and 512fs. When evaluating in a condition except above, please use

other mode.

Refer to the datasheet for register setting of the AK4637.

Applicable Evaluation Mode

(1) A/D Evaluation using the AK4118A (DIT).

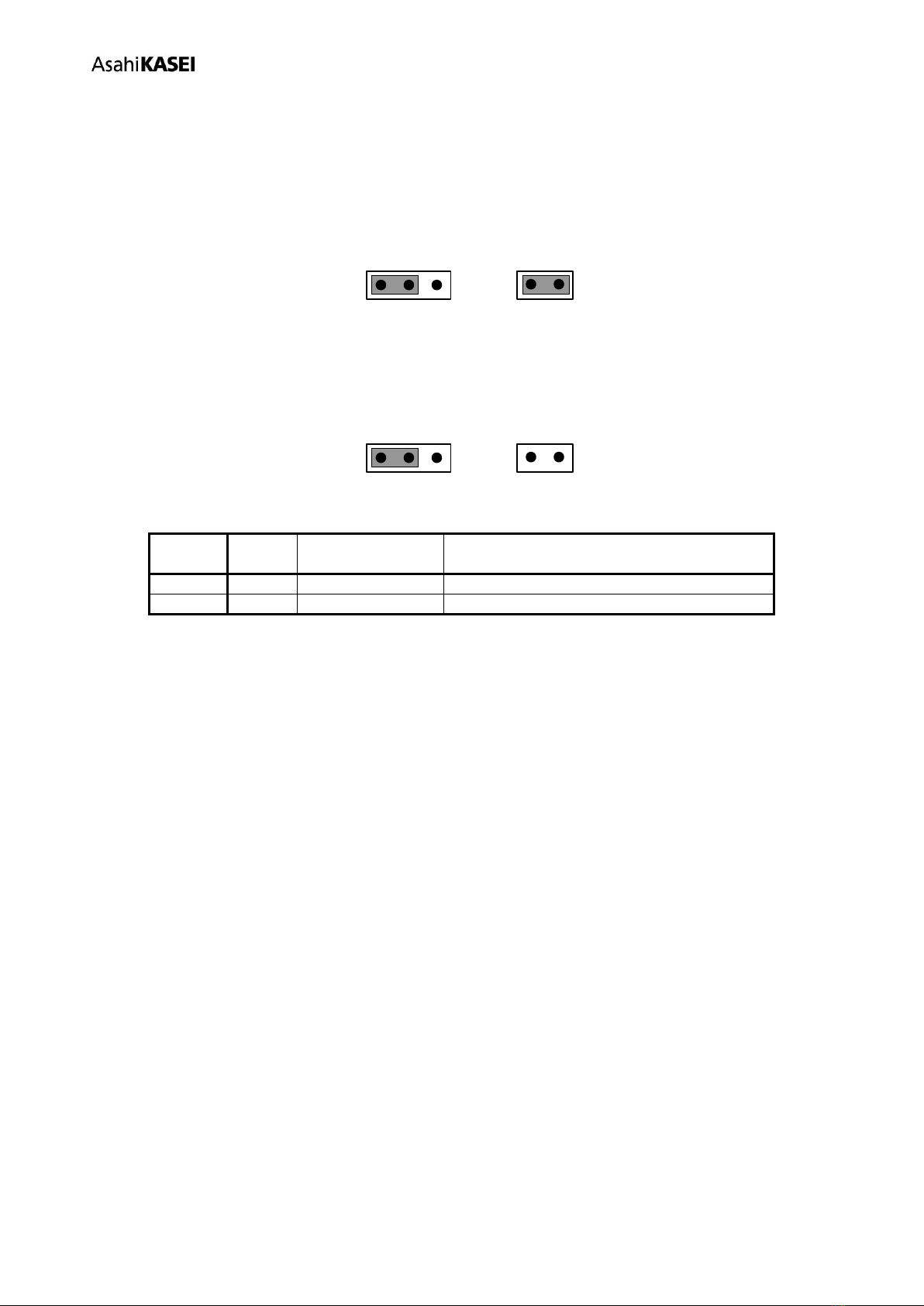

(1-1) Setting in External Slave Mode

(2) D/A Evaluation using the AK4118A (DIR). <Default>

(2-1) Setting in External Slave Mode

(3) Evaluation of A/D or D/A using the external clock.

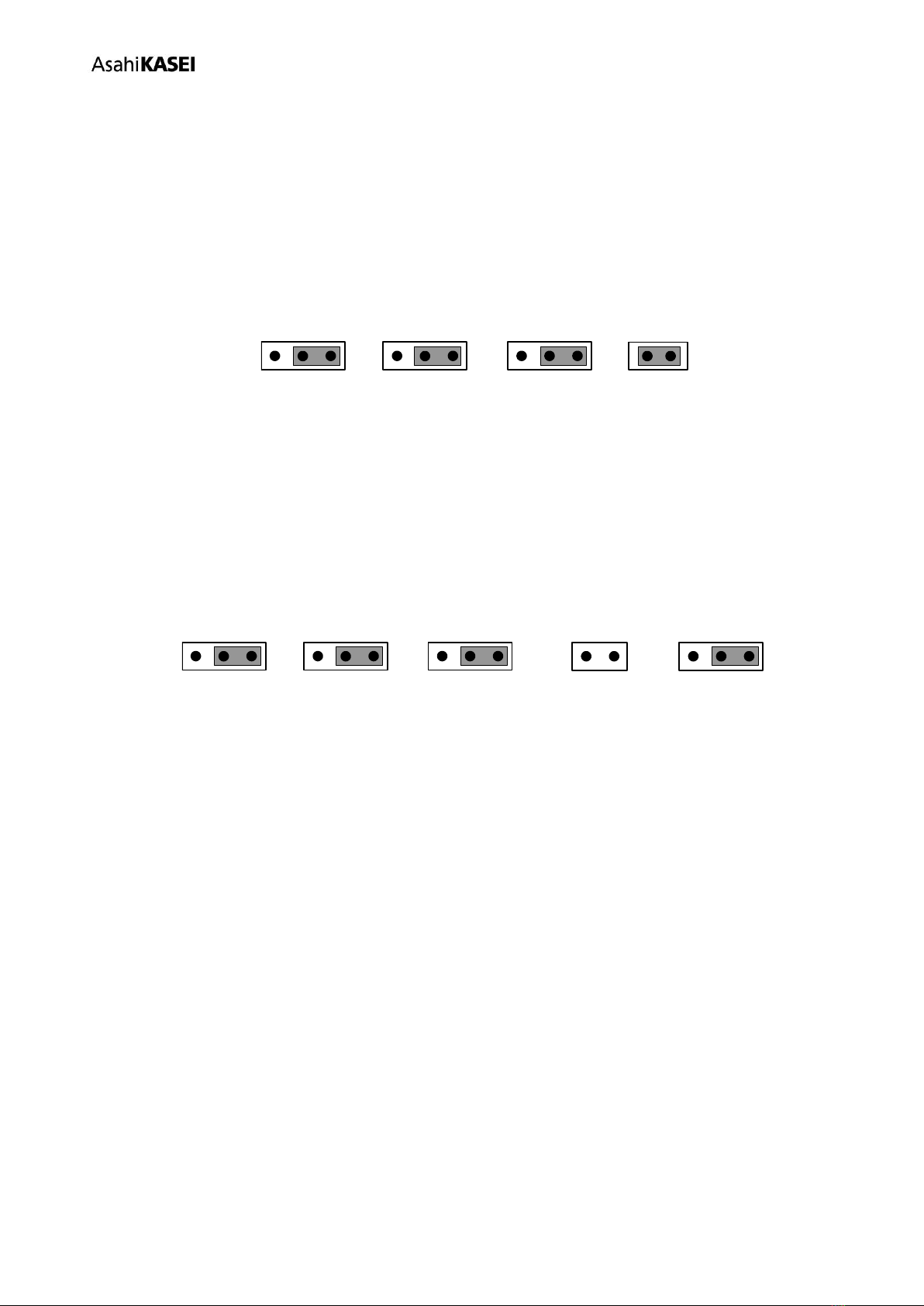

(3-1) Setting in PLL Master Mode

(3-2) Setting in PLL Slave Mode

(3-3) Setting in External Slave Mode

(4) Evaluation of Loop-back.

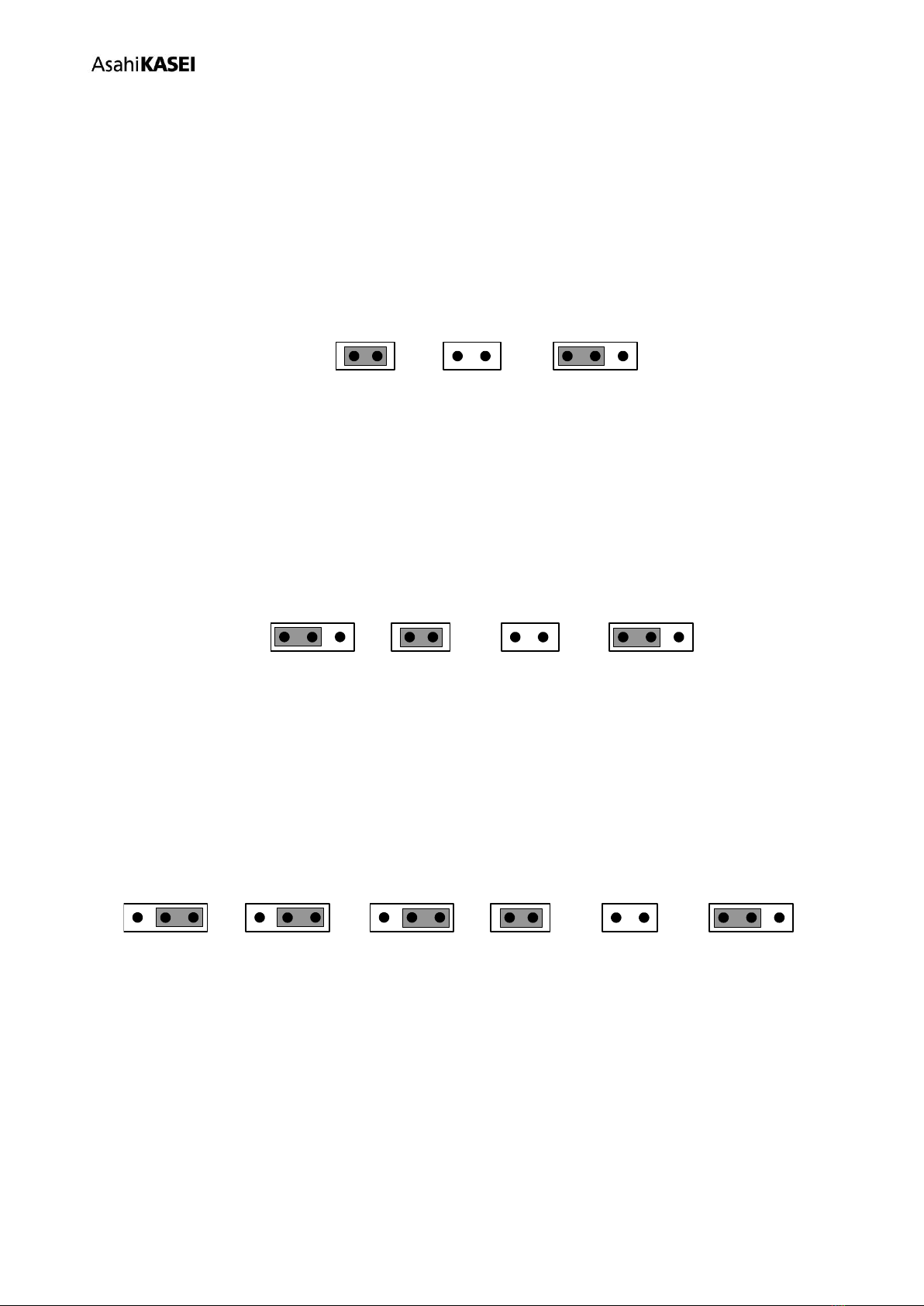

(4-1) Setting in PLL Master Mode

(4-2) Setting in PLL Slave Mode

(4-3) Setting in External Slave Mode