ASAHI KASEI [AKD4584]

<KM065802> 2009/06

- 5 -

Operation sequence

1) Set up the power supply lines.

[AVDD] (Red) = 4.75 ∼5.25V : for AVDD, DVDD, PVDD of AK4584 (typ. 5.0V)

[TVDD] (Orange) = 2.7 ∼5.25V : for TVDD of AK4584 (typ. 3.0V)

[VCC] (Red) = 5.0V : for logic (typ. 5.0V)

[VDD] (Red) = 5.0V : for logic (typ. 5.0V)

[AGND] (Black) = 0V : for analog ground

[DGND] (Black) = 0V : for logic ground

Each supply line should be distributed from the power supply unit.

2) Set up the evaluation mode, jumper pins and DIP switches. (See the followings.)

3) Power on.

The AK4584 should be reset once bringing SW1 “L” upon power-up.

Evaluation mode

(1) Slave mode

In case of AK4584 evaluation using AK4114, it is necessary to correspond to AK4584’s and AK4114’s audio

interface format. About AK4584’s audio interface format, refer to AK4584’s datasheet. About AK4114’s audio

interface format, see Table2.

(1-1)A/D evaluation using DIT function of AK4584

(1-2)A/D evaluation using DIT function of AK4114

(1-3)D/A evaluation using DIR function of AK4114

(1-4)All interfacing signal (MCLK, BICK, LRCK) are fed from the external circuit

(1-1) A/D evaluation using DIT function of AK4584

Using J5 (EXT), PORT4 (DIT) and J6 (TX). Nothing should be connected to J7 (RX), PORT1 (DIR), PORT5

(DIR) and PORT6 (ROM). Remove the X’tal (X1). The bi-phase data is output from TX3. JP6 (EXT) should be

open.

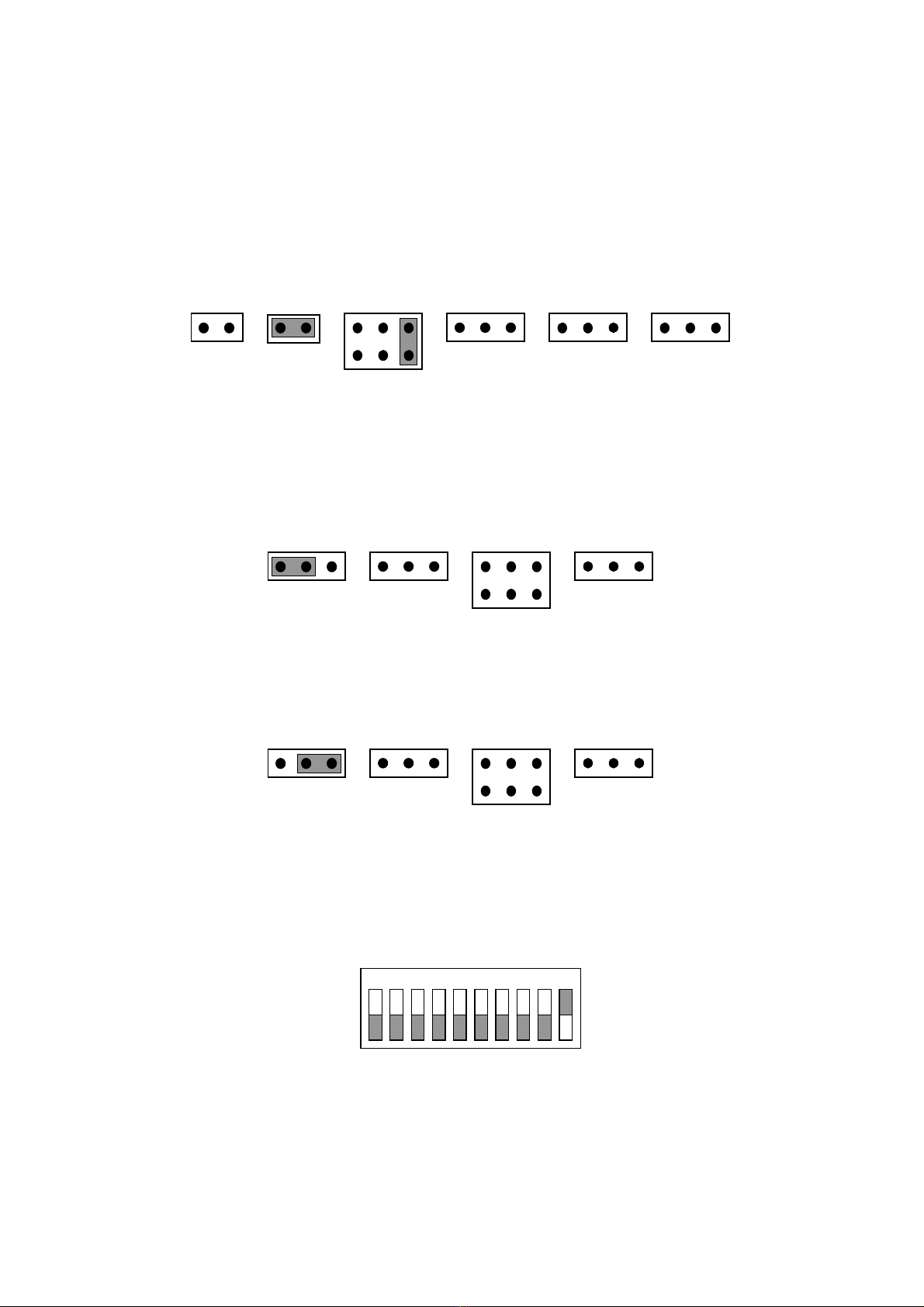

JP10

MCLK

JP3

XTI JP14

LRCK

JP6

EXT JP11

BICK

EX

DIR

DIR

EXT

ADC

JP15

SDTI

ADCDIREX

DIR