ZYNQ FPGA Development Board AC7Z035B User Manual

Amazon Store: https://www.amazon.com/alinx

Sales Email: rachel.zhou@aithtech.com

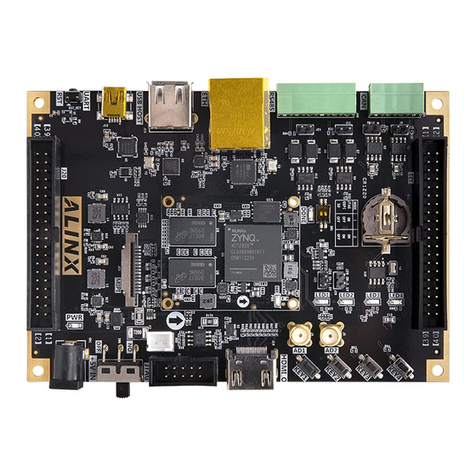

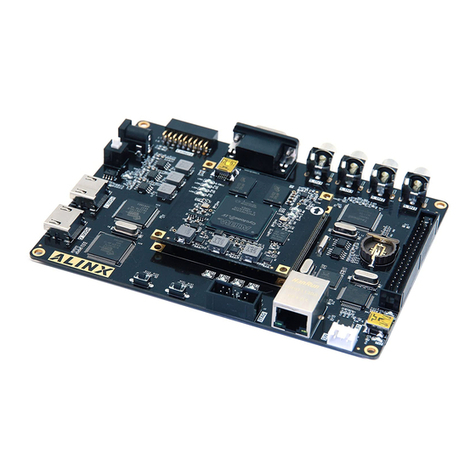

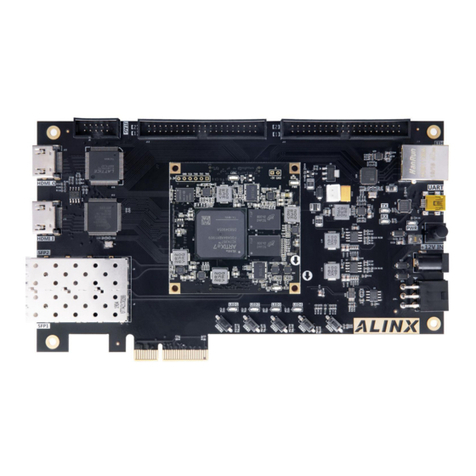

Part 1: AC7Z035B Core Board Introduction

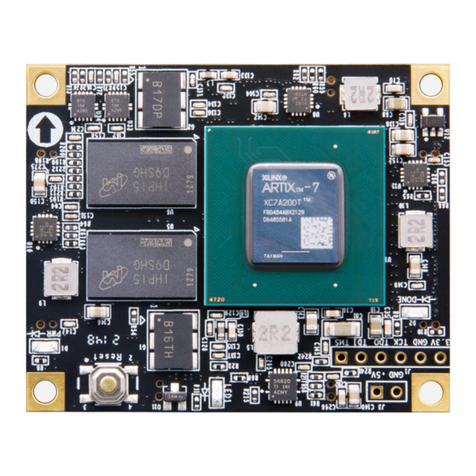

AC7Z035B (core board model, the same below) FPGA core board, ZYNQ

chip is based on XC7Z035-2FFG676 of XILINX company ZYNQ7000 series.

The ZYNQ chip's PS system integrates two ARM CortexTM-A9 processors,

AMBA® interconnects, internal memory, external memory interfaces and

peripherals. The FPGA of the ZYNQ chip contains a wealth of programmable

logic cells, DSP and internal RAM.

The core board uses four Micron 512MB DDR3 chips

MT41J256M16HA-125 for a total capacity of 4GB. Two DDR3s are mounted on

the PS and PL sides, respectively, which form a 32-bit bus width. The DDR3

SDRAM on the PS side can run at up to 533MHz (data rate 1066Mbps), and

the DDR3 SDRAM on the PL side can run at speeds up to 800MHz (data rate

1600Mbps). In addition, two 256MBit QSPI FLASH and 8GB eMMC FLASH

chips are integrated on the core board to boot the storage configuration and

system files.

In order to connect with the carrier board, the four board-to-board

connectors of the core board expand the USB interface, the Gigabit Ethernet

interface, the SD card interface and other remaining IO ports of the PS side;

and also extend the 8-pair high-speed transceiver GTX interface of the ZYNQ,

almost all IO ports (144) on the PL side. The level of IO of BANK12 and

BANK13 can be modified by replacing the LDO chip on the core board to meet

the requirements of different level interfaces of users. For users who need a lot

of IO, this core board will be a good choice. Moreover, the IO connection part,

the routing between the ZYNQ chip and the interface is equal length and

differential processing, and the core board size is only 80*60 (mm), which is

very suitable for secondary development.