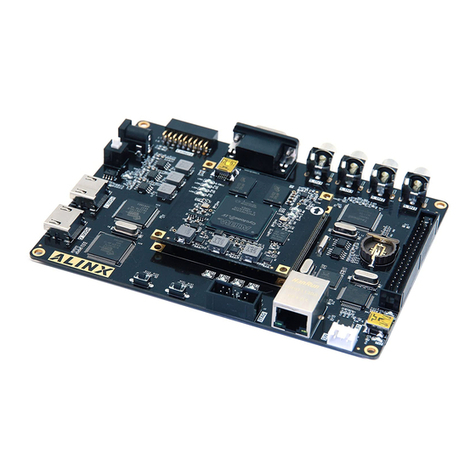

FPGA Development Board AX301 User Manual

Amazon Store: https://www.amazon.com/alinx

Table of Contents

Version Record.......................................................................................... 2

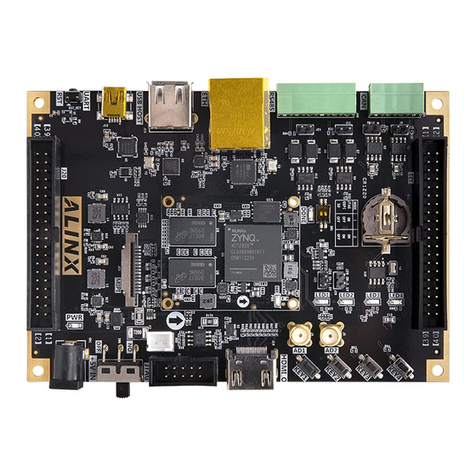

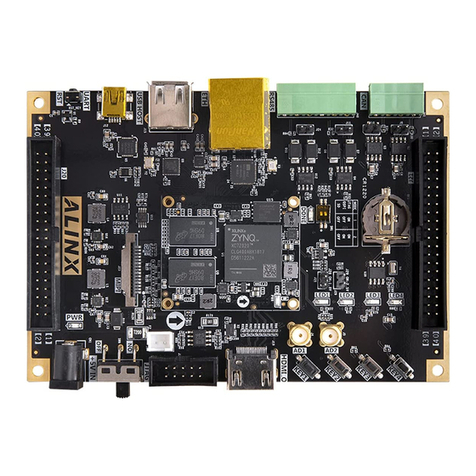

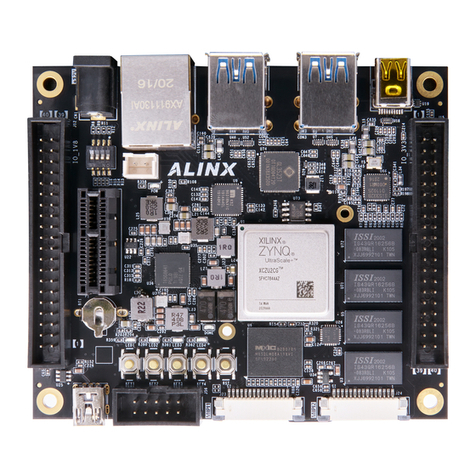

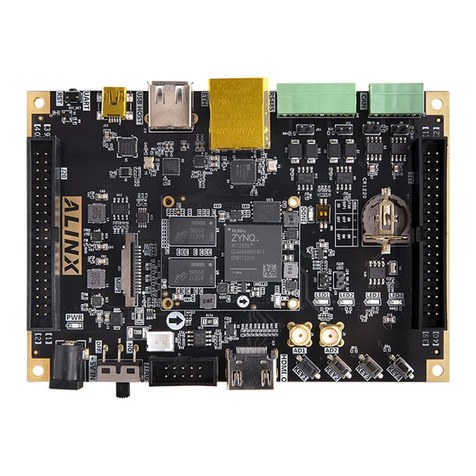

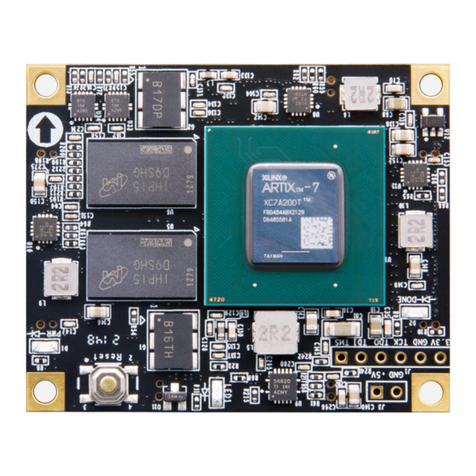

Part 1: FPGA Development Board Introduction..........................................5

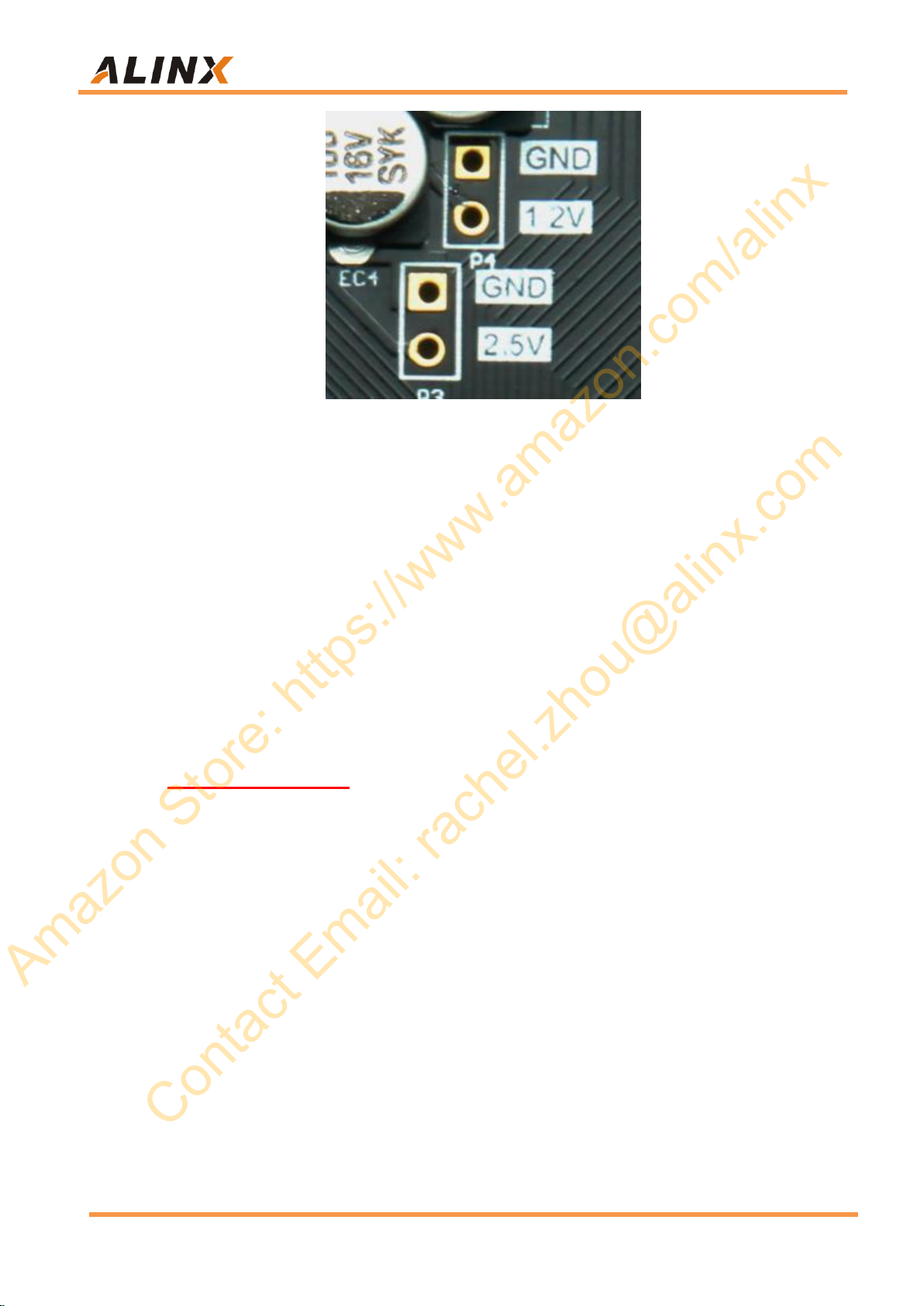

Part 2: Power Supply..................................................................................7

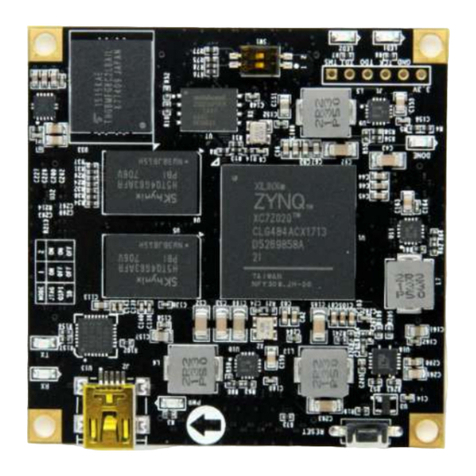

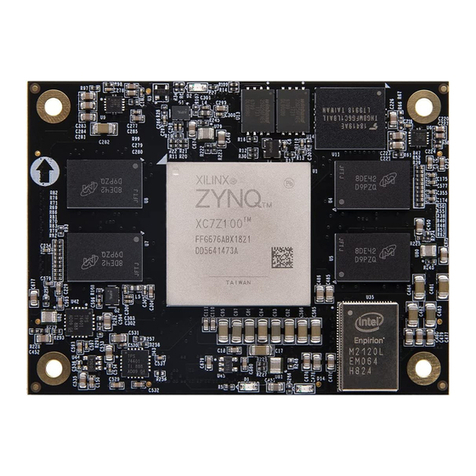

Part 3: FPGA ..............................................................................................8

Part 3.1: JTAG Interface......................................................................9

Part 3.2: FPGA power and GND pins................................................10

Part 4: 50M Active Crystal ........................................................................12

Part 5: SPI Flash ......................................................................................13

Part 6: SDRAM.........................................................................................14

Part 7: EEPROM 24LC04.........................................................................17

Part 8: Real-time clock DS1302 ...............................................................18

Part 9: USB to Serial Port.........................................................................19

Part 10: VGA Interface..............................................................................21

Part 11: SD Card Slot ...............................................................................24

Part 12: LEDs ...........................................................................................26

Part 13: User Keys ...................................................................................27

Part 14: Camera Module interface............................................................28

Part 15: Digital Tube.................................................................................29

Part 16: Buzzer.........................................................................................32

Part 17: Expansion Ports..........................................................................33

Amazon Store: https://www.amazon.com/alinx