Alinx AX7035 User manual

Other Alinx Motherboard manuals

Alinx

Alinx AX7A200 User manual

Alinx

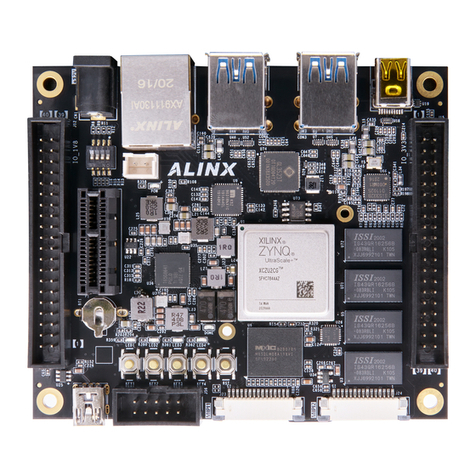

Alinx Zynq UltraScale+MPSoC User manual

Alinx

Alinx ZYNQ UltraScale+ User manual

Alinx

Alinx AXKU041 User manual

Alinx

Alinx AC7010C User manual

Alinx

Alinx ZYNQ7000 FPGA User manual

Alinx

Alinx ZYNQ UltraScale+ User manual

Alinx

Alinx AXU2CGB-E User manual

Alinx

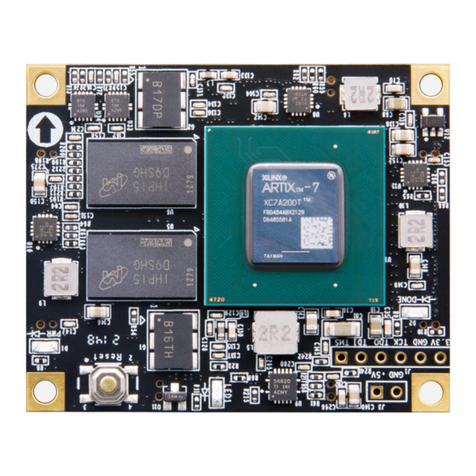

Alinx ARTIX-7FPGA User manual

Alinx

Alinx AC7200 User manual

Alinx

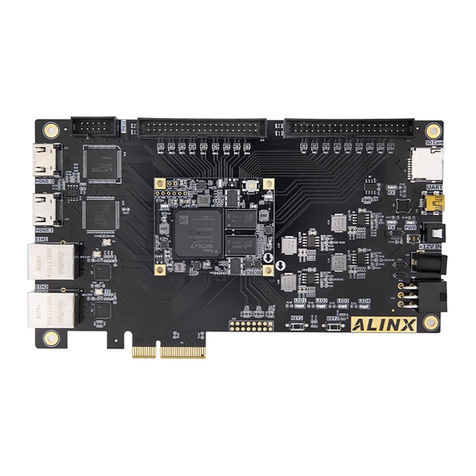

Alinx KINTEX UltraScale FPGA AXKU042 User manual

Alinx

Alinx AC7021B User manual

Alinx

Alinx ARTIX-7 FPGA User manual

Alinx

Alinx AV4075 User manual

Alinx

Alinx ACU3EG User manual

Alinx

Alinx ZYNQ7000 FPGA User manual

Alinx

Alinx AC7021 User manual

Alinx

Alinx ZYNQ UltraScale+ AXU9EGB User manual

Alinx

Alinx AX7202 User manual

Alinx

Alinx AC7015 User manual