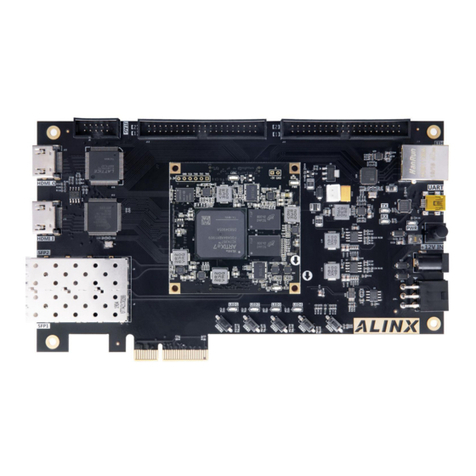

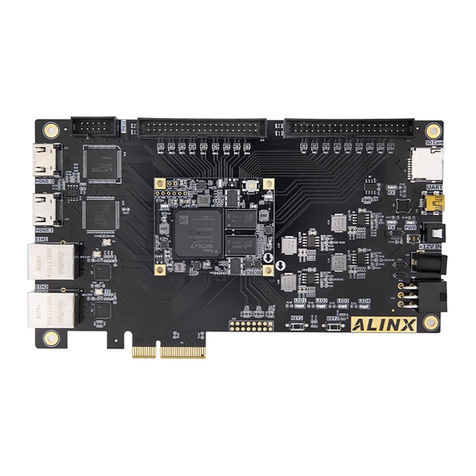

The two-channel high-speed transceiver of THE GTH transceiver of FPGA is

connected to the transmitting and receiving of two optical modules to realize the

two-channel high-speed optical communication interface. Each channel of optical

fiber data communication receives and sends up to 16.3Gb/s

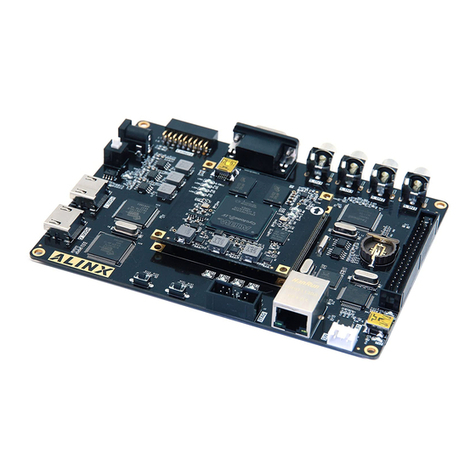

USB Uart interface

1 Uart to USB interface, used for communication with computer, convenient user

debugging. Serial port chip adopts USB-UAR chip of Silicon Labs CP2102GM, USB

interface adopts MINI USB interface.

Ethernet interface

One 10/100m /1000M Ethernet RJ45 port, used for Ethernet data exchange with

computers or other network devices. The network interface chip adopts Micrel

KSZ9031 industrial grade GPHY chip.

FMC Interface

Three standard FMC expansions, including two LPC expansions and one HPC

expansions. XILINX or our black gold can be connected to various FMC modules

(HDMI input/output module, binocular camera module, high-speed AD module and

so on.

Micro SD

1 Micro SD card holder, used for FPGA to read and write SD card data and

storage

SMA

2 channels SMA external interface, pin connection common clock signal, used

for external input and output signals.

Temperature and humidity sensor EEPROM

The onboard TEMPERATURE and humidity sensor chip LM75 is used to detect

the ambient temperature and humidity of the board.

An ONBOARD EEPROM is used to communicate with IIC bus and store some

customized information.

JTAG

A 10-pin 2.54mm standard JTAG port is used for downloading and debugging of

FPGA programs. Users can debug and download FPGA through XILINX downloader.

CLK

A 200Mhz differential crystal oscillator provides a stable clock source for FPGA