Table of Contents

Version Record .............................................................................................2

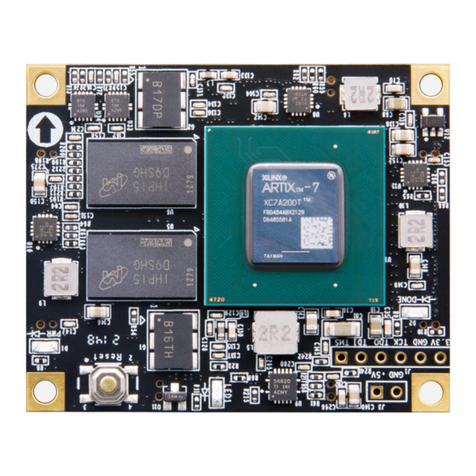

Part 1: FPGA Development Board Introduction .......................................... 6

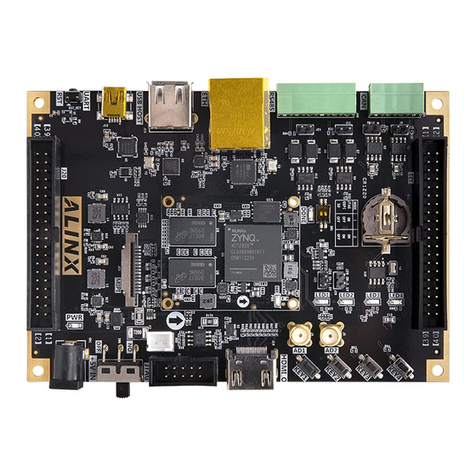

Part 2: ACU2CG core board ...................................................................... 10

Part 2.1: ACU2CG core board Introduction ....................................... 10

Part 2.2: ZYNQ Chip ...........................................................................11

Part 2.3: DDR4 DRAM ........................................................................13

Part 2.4: QSPI Flash ...........................................................................18

Part 2.5: eMMC Flash .........................................................................19

Part 2.6: Clock configuration .............................................................. 21

Part 2.7: LED ...................................................................................... 23

Part 2.8: Power Supply .......................................................................24

Part 2.9: ACU2CG Core Board Form Factor ..................................... 25

Part 2.10: Board to Board Connectors pin assignment .....................25

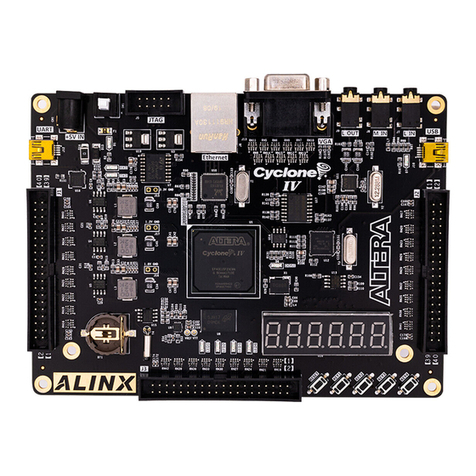

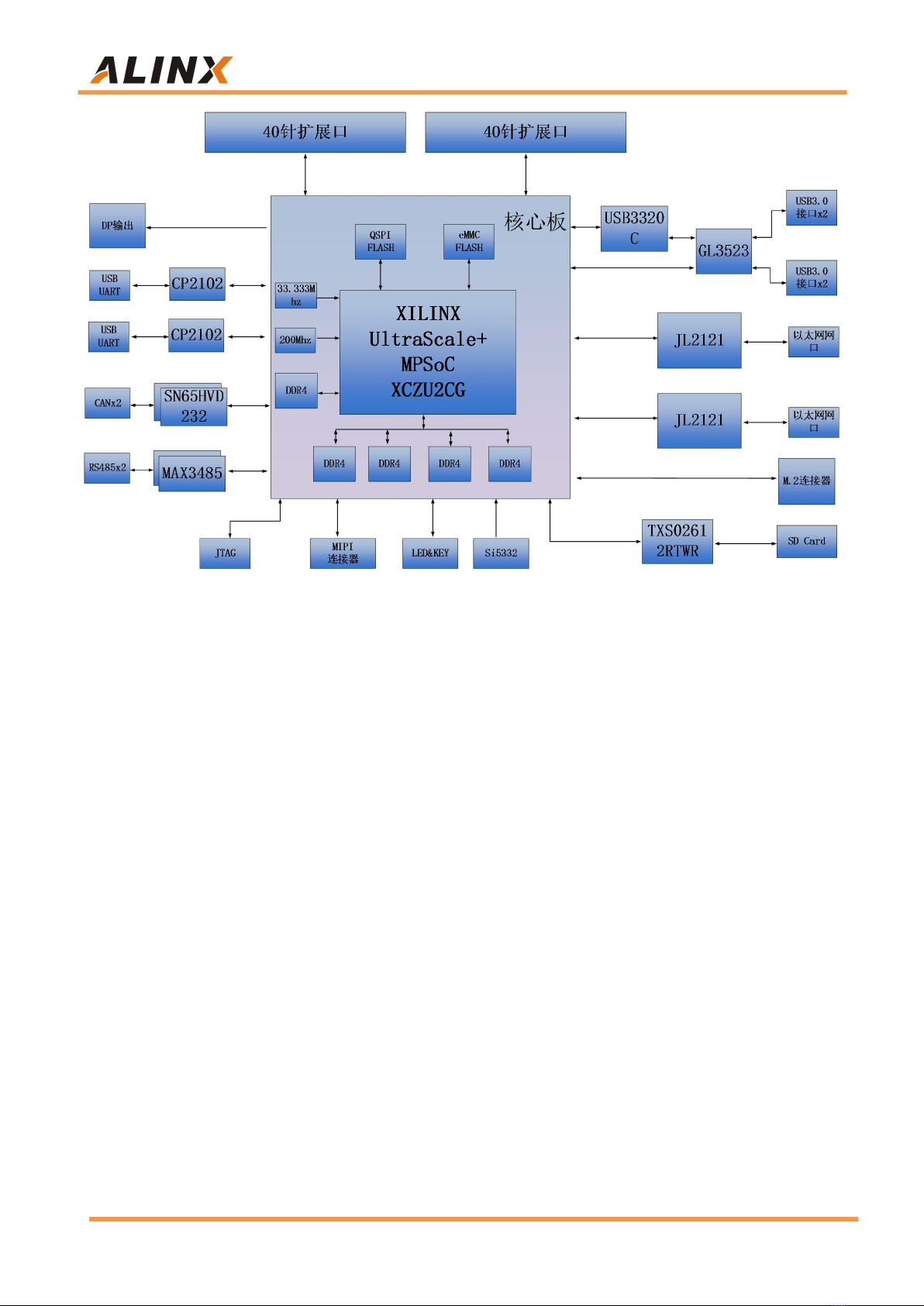

Part 3: Carrier Board ..................................................................................35

Part 3.1: Carrier Board Introduction ................................................... 35

Part 3.2: M.2 Interface ........................................................................36

Part 3.3: DP Interface ......................................................................... 37

Part 3.4: USB3.0 interface ..................................................................39

Part 3.5: Gigabit Ethernet Interface ................................................... 40

Part 3.6: USB to Serial Port ................................................................42

Part 3.7: SD Card Slot Interface .........................................................43

Part 3.8: Expansion Header ............................................................... 44

Part 3.9: CAN communication interface .............................................46

Part 3.10: 485 communication interface ............................................ 47

Part 3.11: MIPI camera interface ........................................................48

Part 3.12: JTAG Debug Port ...............................................................49

Part 3.13: Real-time clock .................................................................. 50