3 / 52

Cyclone IV FPGA Development Board AX515 User Manual

Table of Contents

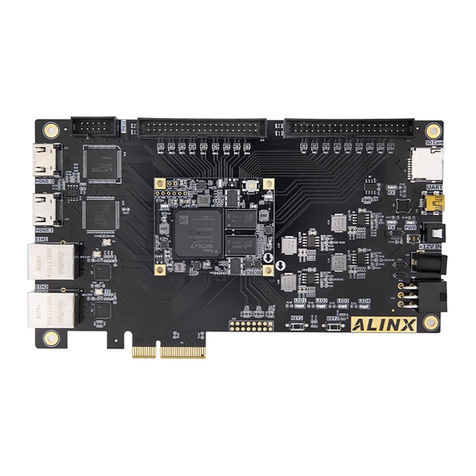

Part 1: FPGA Development Board Introduction.......................................... 5

Part 2: Structure Diagram........................................................................... 8

Part 3: Power.............................................................................................. 9

Part 4: FPGA Chip.....................................................................................11

Part 4.1: FPGA resources ..............................................12

Part 4.2: JTAG Interface.................................................12

Part 4.3: FPGA Power Supply........................................13

Part 5: 50Mhz Clock ................................................................................. 14

Part 6: SPI Flash Configuration chip ........................................................ 15

Part 7: QSPI Flash.................................................................................... 17

Part 8: DDR2 DRAM................................................................................. 19

Part 9: EEPROM 24LC04......................................................................... 23

Part 10:Real-Time Clock........................................................................... 24

Part 11: Gigabit Ethernet Interface ........................................................... 26

Part 12: USB to Serial Port....................................................................... 29

Part 13: VGA Port..................................................................................... 31

Part 14: USB 2.0 interface........................................................................ 33

Part 15: Audio Interface............................................................................ 36

Part 16: SD Card Slot............................................................................... 37

Part 17: Expansion Header ...................................................................... 39

Part 17.1: Expansion header J1.....................................40

Part 17.2: Expansion header J2.....................................42

Part 17.3: Expansion header J3.....................................46

Part 18: LED............................................................................................. 47

Part 19: Buttons........................................................................................ 48