Table of Contents

Version Record .............................................................................................2

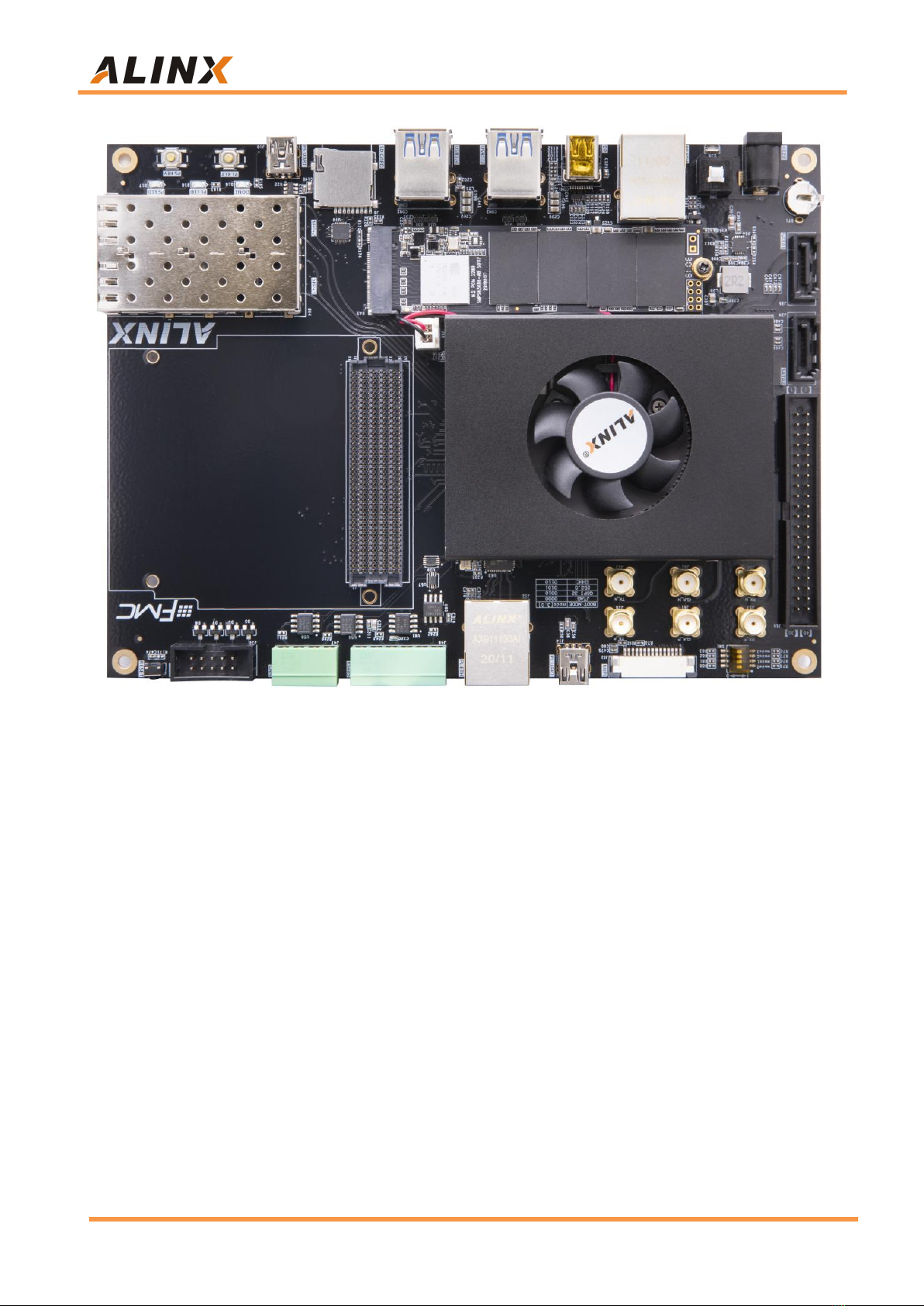

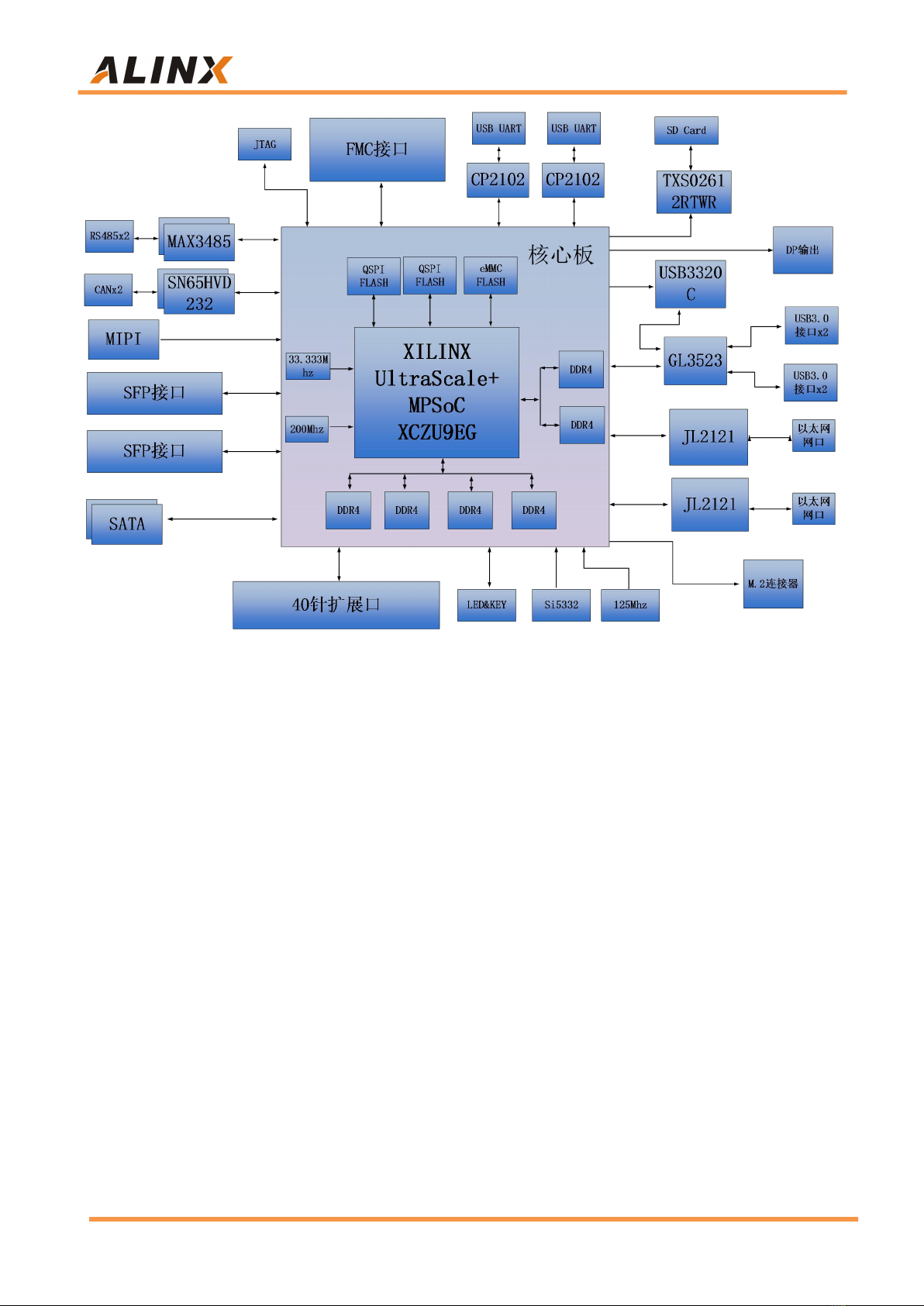

Part 1: FPGA Development Board Introduction .......................................... 7

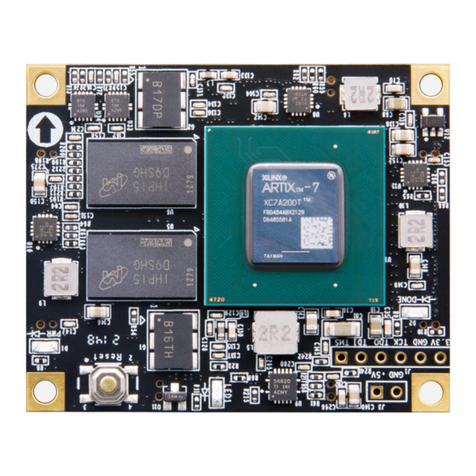

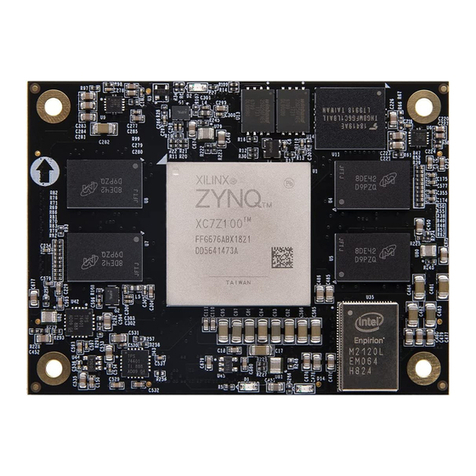

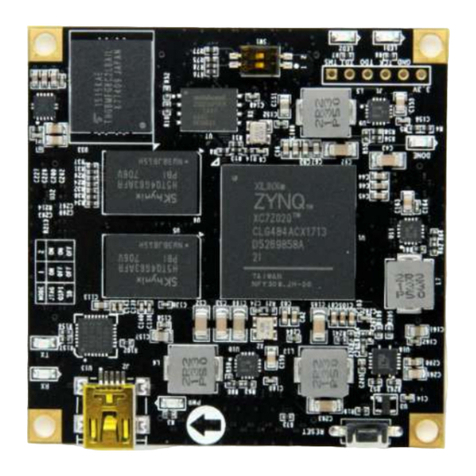

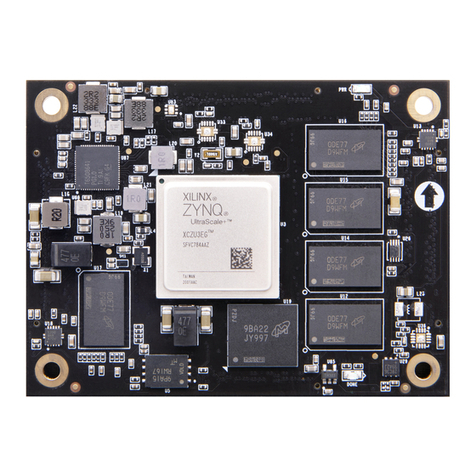

Part 2: ACU9EG Core Board ..................................................................... 12

Part 2.1: ACU9EG Core Board Introduction ...................................... 12

Part 2.2: ZYNQ Chip ...........................................................................13

Part 2.3: DDR4 DRAM ........................................................................15

Part 2.4: QSPI Flash ...........................................................................22

Part 2.5: eMMC Flash .........................................................................24

Part 2.6: Clock configuration .............................................................. 25

Part 2.7: Power Supply .......................................................................28

Part 2.8: ACU9EG Core Board Size Dimension ................................ 30

Part 2.9: Board to Board Connectors pin assignment ....................... 30

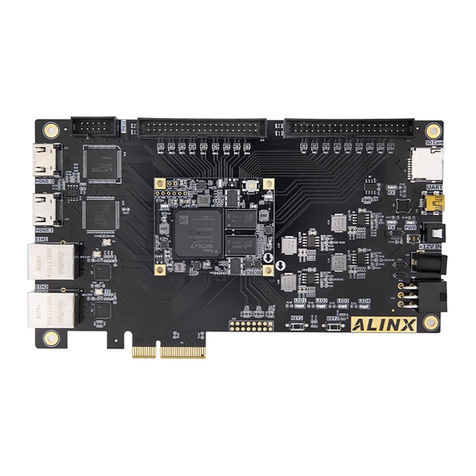

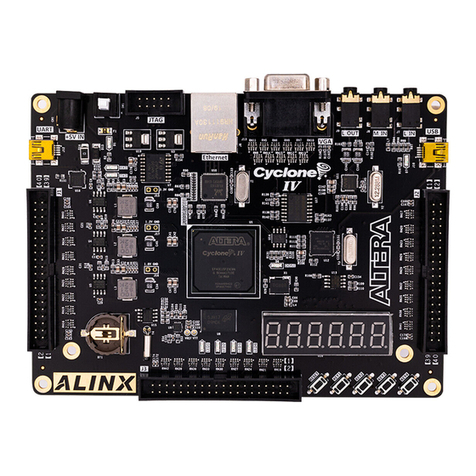

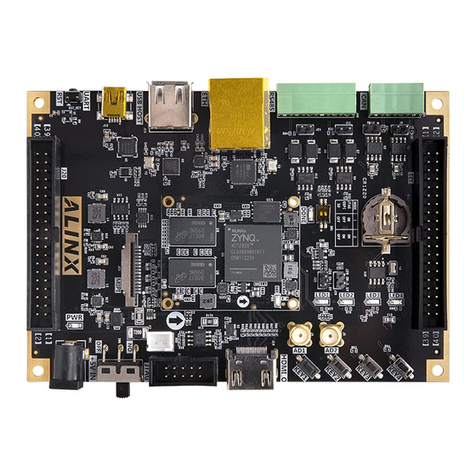

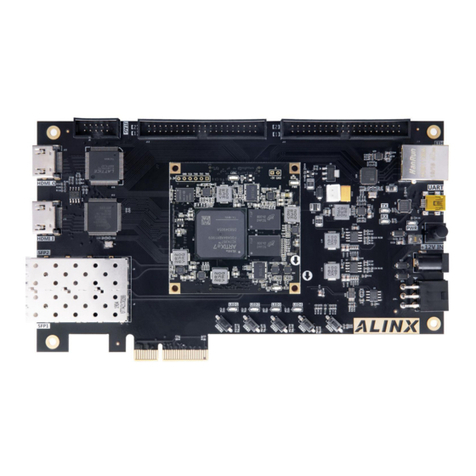

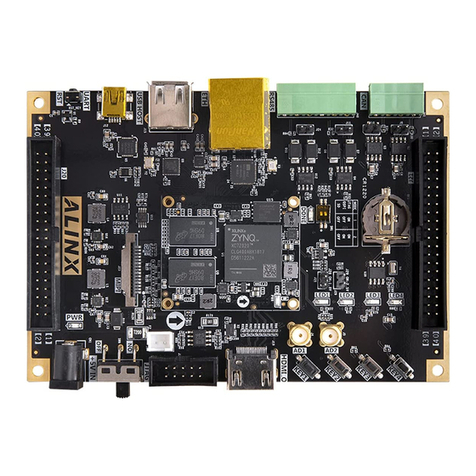

Part 3: Carrier Board ..................................................................................39

Part 3.1: Carrier Board Introduction ................................................... 39

Part 3.2: M.2 Interface ........................................................................39

Part 3.3: DP Interface ......................................................................... 40

Part 3.4: USB3.0 Interface ................................................................. 42

Part 3.5: Gigabit Ethernet Interface ................................................... 43

Part 3.6: USB to Serial Port ................................................................46

Part 3.7: SD Card Slot Interface .........................................................47

Part 3.8: SFP Interface ....................................................................... 48

Part 3.9: CAN Communication Interface ............................................50

Part 3.10: 485 Communication Interface ........................................... 50

Part 3.11: MIPI Camera Interface .......................................................51

Part 3.12: FMC Interface .................................................................... 53

Part 3.13: 40-Pin Expansion Headers ................................................58

Part 3.14: JTAG Debug Port ...............................................................59