Http://www.heijin.org

4 / 50

Contents

Overview............................................................................................................................5

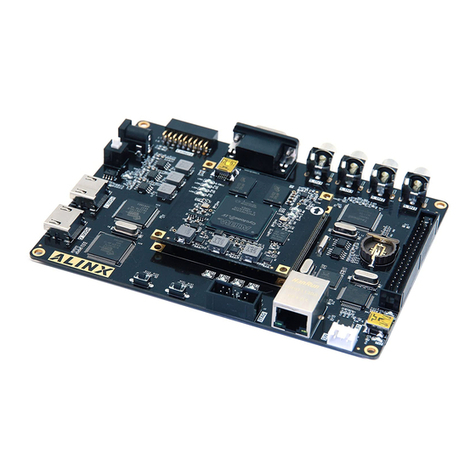

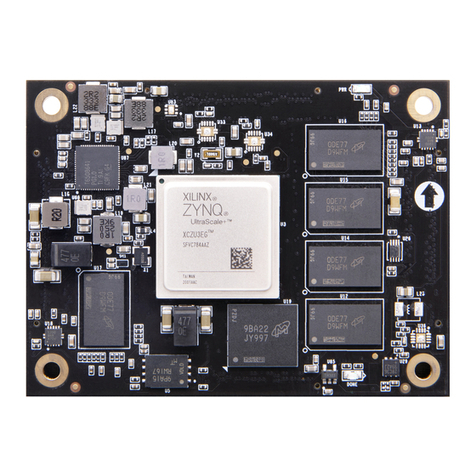

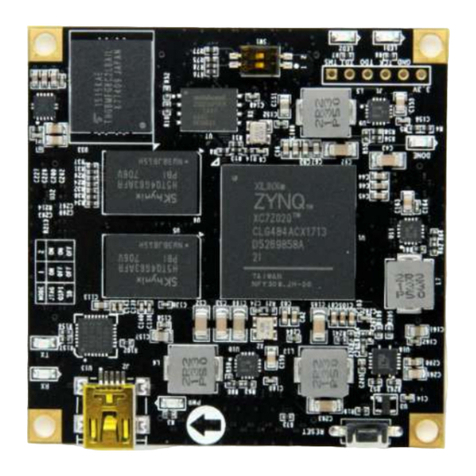

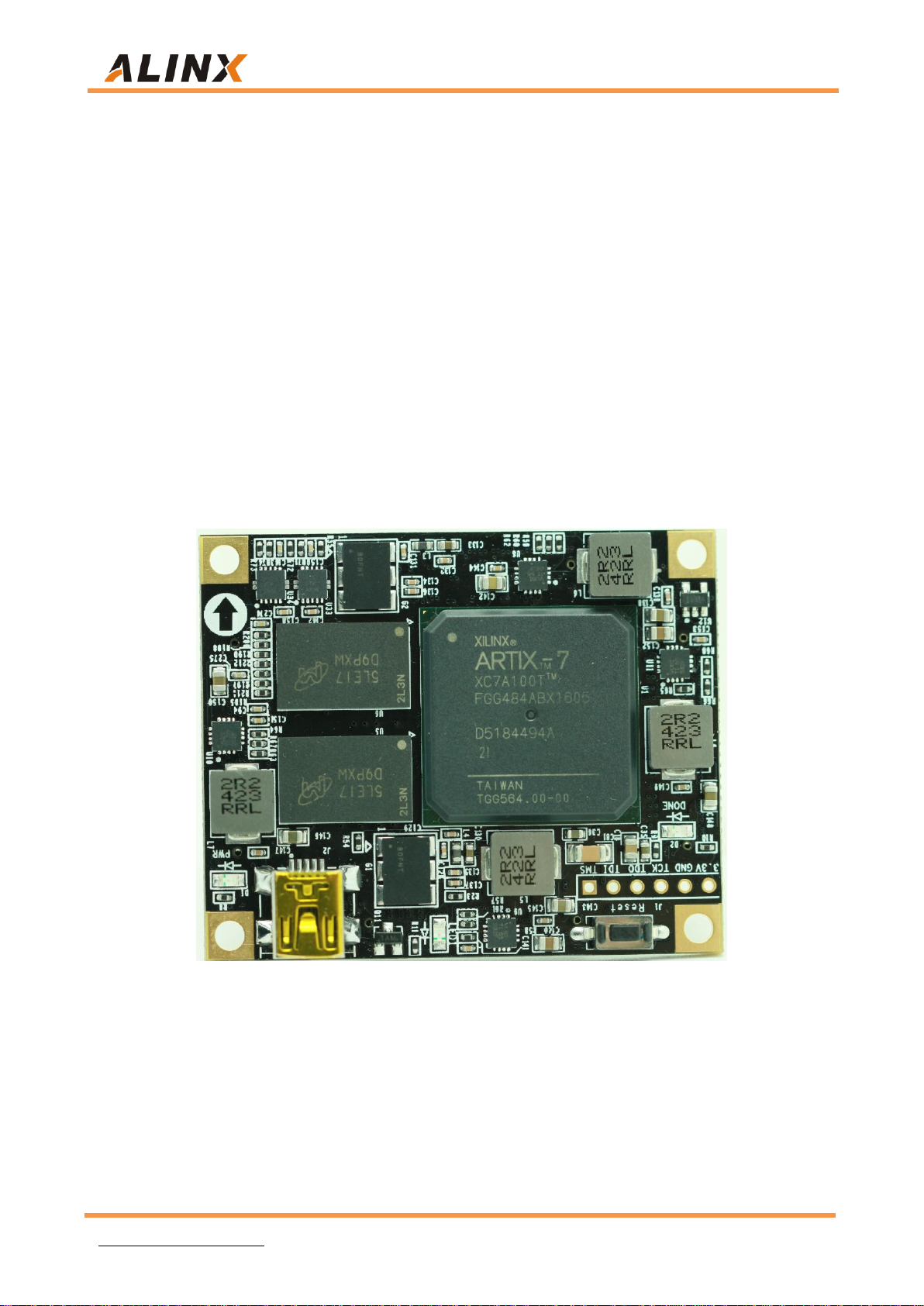

FPGA Core Board ..............................................................................................................8

1. Overview................................................................................................................... 8

2. FPGA........................................................................................................................ 9

3. Differential Crystal Oscillator ................................................................................ 11

4. DDR3...................................................................................................................... 12

5. QSPI Flash.............................................................................................................. 16

6. LED light ................................................................................................................ 17

7. Reset Button............................................................................................................ 18

8. JTAG Interface........................................................................................................ 19

9. Power Input............................................................................................................. 19

10. Board-to-Board Connector ..................................................................................... 20

11. Power ...................................................................................................................... 27

12. Mechanical.............................................................................................................. 30

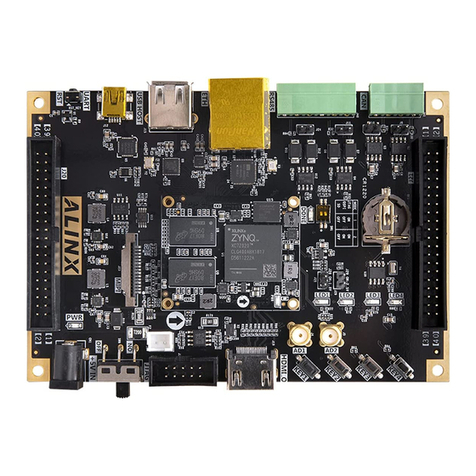

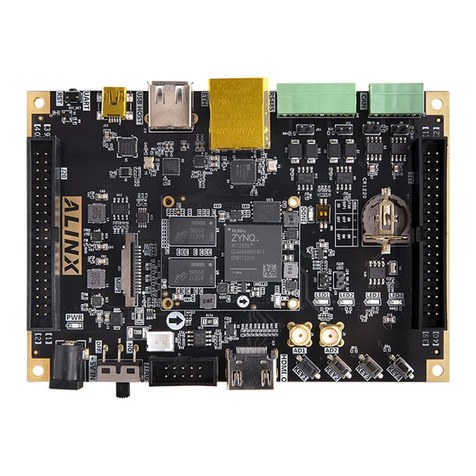

Expansion Board.............................................................................................................. 31

1. Preview ................................................................................................................... 31

2. Gigabit Ethernet...................................................................................................... 31

3. PCIe x4 Connector.................................................................................................. 33

4. HDMI Input Connector........................................................................................... 35

5. HDMI Input Connector........................................................................................... 37

6. SD socket................................................................................................................ 38

7. USB Serial Port....................................................................................................... 39

8. EEPROM 24LC04.................................................................................................. 41

9. GPIO Expansion Headers....................................................................................... 42

10. JTAG Connector ..................................................................................................... 45

11. XADC Connector(Not install by default)......................................................... 46

12. Buttons.................................................................................................................... 47

13. LED......................................................................................................................... 48

14. Power Supply.......................................................................................................... 49