ADA-VPX3-7V1 User Manual

V2.1 - 6th anuary 2016

Table Of Contents

1 Introduction ...................................................................................................................................... 1

1.1 Key Features ................................................................................................................................. 1

1.2 References & Specifications .......................................................................................................... 2

2 Installation ........................................................................................................................................ 2

2.1 Software Installation ...................................................................................................................... 2

2.2 Hardware Installation ..................................................................................................................... 2

2.2.1 Handling Instructions ................................................................................................................. 2

2.2.2 Cooling Requirements ............................................................................................................... 2

3 Functional Description .................................................................................................................... 4

.1 Overview ........................................................................................................................................ 4

.1.1 Switch Definitions ...................................................................................................................... 5

.1.2 LED Definitions .......................................................................................................................... 6

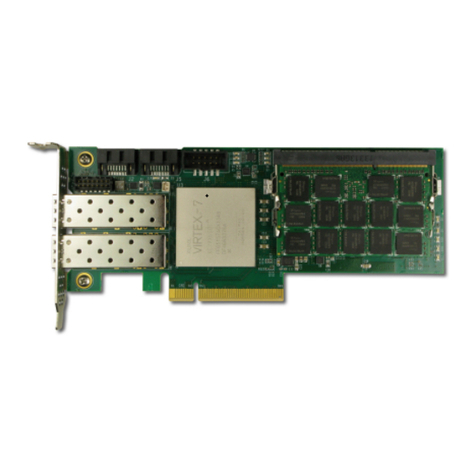

.2 VPX P0 Interface ........................................................................................................................... 7

.2.1 MVMRO ..................................................................................................................................... 7

.2.2 SYSRESET# .............................................................................................................................. 7

.2. AUXCLK ..................................................................................................................................... 7

. JTAG Interface ............................................................................................................................... 8

. .1 On-board Interface ..................................................................................................................... 8

. .2 VPX Interface ............................................................................................................................. 8

. . JTAG Voltages ........................................................................................................................... 8

.4 Clocks ............................................................................................................................................ 9

.4.1 200MHz Reference Clock (REFCLK200M) ............................................................................... 9

.4.2 PCIe Reference Clock 0 (PCIEREFCLK0) .............................................................................. 10

.4. PCIe Reference Clock 1 (PCIEREFCLK1) .............................................................................. 10

.4.4 AUXCLK ................................................................................................................................... 11

.4.5 Programmable Clocks (LCLK, PROGCLK 0- ) ........................................................................ 11

.4.6 Module-Carrier Global Clock (GCLK_M2C) ............................................................................. 11

.4.7 Module-Carrier MGT Clock (MGTCLK_M2C) .......................................................................... 11

.4.8 XRM LVDS Clock (XRM_LVDS_CLK) ..................................................................................... 12

.5 Flash Memory .............................................................................................................................. 1

.6 Configuration ............................................................................................................................... 14

.6.1 Power-Up Sequence ................................................................................................................ 14

.6.2 Bridge-Less Mode .................................................................................................................... 14

.7 Health Monitoring ......................................................................................................................... 15

.7.1 Automatic Temperature Monitoring .......................................................................................... 16

.7.2 Microcontroller Status LEDs .................................................................................................... 16

.8 Local Bus ..................................................................................................................................... 17

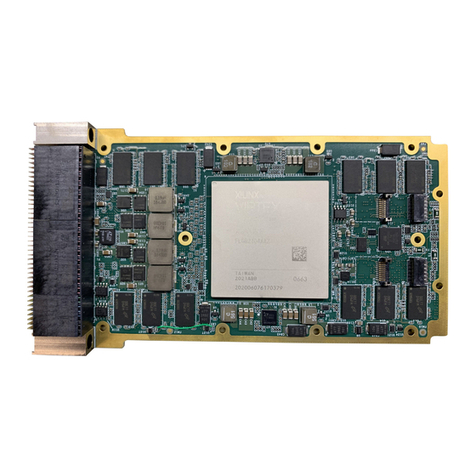

.9 Target FPGA ................................................................................................................................ 17

.9.1 I/O Bank Voltages .................................................................................................................... 17

.9.2 Target MGT Links .................................................................................................................... 17

.10 Memory Interfaces ....................................................................................................................... 18

.11 XRM Interface and Front-Panel I/O ............................................................................................. 20

.11.1 XRM Connector, CN1 .............................................................................................................. 20

.11.2 XRM Connector CN2 ............................................................................................................... 20

.11. XRM I/F - GPIO ....................................................................................................................... 20

.11.4 XRM I/F - High-speed Serial Links .......................................................................................... 21

Appendix A VPX Backplane Pinouts ................................................................................................................ 23

Appendix B Front (XRM) Connector Pinouts ................................................................................................... 24