3-Feb-2015

Table of Contents

1INTRODUCTION.................................................................................................................................. 2

2FUNCTIONAL DESCRIPTION............................................................................................................ 3

2.1 ALL PROGRAMMABLE SOC ............................................................................................................. 3

2.2 MEMORY......................................................................................................................................... 3

2.2.1 DDR3L.................................................................................................................................... 3

2.2.2 Quad-SPI Flash...................................................................................................................... 4

2.2.3 eMMC (Multi-Media Controller)............................................................................................ 5

2.3 USB 2.0 OTG.................................................................................................................................. 6

2.4 10/100/1000 ETHERNET PHY ......................................................................................................... 7

2.5 USER I/O......................................................................................................................................... 9

2.5.1 Available PS MIO User Pins.................................................................................................. 9

2.5.2 Available PL IO User Pins ..................................................................................................... 9

2.6 CLOCK SOURCE..............................................................................................................................10

2.7 RESET SOURCES .............................................................................................................................10

2.7.1 Zynq Power

‐

on Reset (PS_POR_B).......................................................................................10

2.7.2 PROGRAM_B, DONE, PUDC_B, INIT_B Pins....................................................................10

2.7.3 Processor Subsystem Reset....................................................................................................10

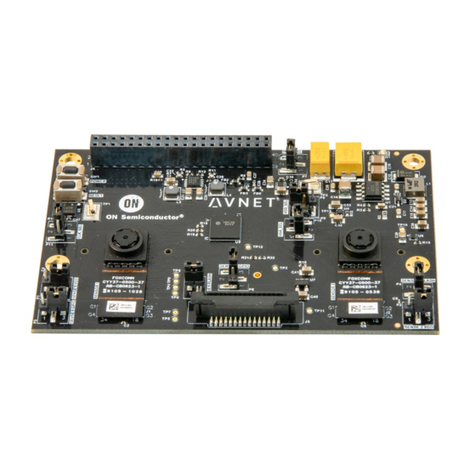

2.8 EXPANSION HEADERS ....................................................................................................................11

2.8.1 Micro Headers.......................................................................................................................11

2.9 CONFIGURATION MODES................................................................................................................16

2.9.1 JTAG Connections.................................................................................................................17

2.10 POWER SUPPLIES............................................................................................................................18

2.10.1 Voltage Rails and Sources.....................................................................................................18

2.10.2 Voltage Regulators ................................................................................................................19

2.10.3 Power Supply Sequencing......................................................................................................20

2.10.4 PCB Bypass / Decoupling Strategy .......................................................................................22

2.10.5 Power Good LED ..................................................................................................................22

2.10.6 Power Estimation ..................................................................................................................22

2.10.7 XADC Power Configuration..................................................................................................22

2.10.8 Battery Backup - Device Secure Boot Encryption Key..........................................................23

2.10.9 Cooling Fan...........................................................................................................................23

3ZYNQ-7000 AP SOC I/O BANK ALLOCATION...............................................................................24

3.1 PS MIO ALLOCATION ....................................................................................................................24

3.2 ZYNQ-7000 AP SOCBANK VOLTAGES ..........................................................................................25

4MECHANICAL ....................................................................................................................................26

5REVISION HISTORY ..........................................................................................................................27