Enclustra Mercury+ SA2 User manual

Mercury+ SA2 SoC Module

User Manual

Purpose

The purpose of this document is to present the characteristics of Mercury+ SA2 SoC module to the user,

and to provide the user with a comprehensive guide to understanding and using the Mercury+ SA2 SoC

module.

Summary

This document first gives an overview of the Mercury+ SA2 SoC module followed by a detailed description

of its features and configuration options. In addition, references to other useful documents are included.

Product Information Code Name

Product ME-SA2 Mercury+ SA2 SoC Module

Document Information Reference Version Date

Reference / Version / Date D-0000-408-002 07 19.08.2019

Approval Information Name Position Date

Written by DIUN Design Engineer 11.09.2015

Verified by GLAC Design Expert 15.09.2015

Approved by DIUN Manager, BU SP 19.08.2019

Enclustra GmbH – Räffelstrasse 28 – CH-8045 Zürich – Switzerland

Phone +41 43 343 39 43 – www.enclustra.com

Copyright Reminder

Copyright 2019 by Enclustra GmbH, Switzerland. All rights are reserved.

Unauthorized duplication of this document, in whole or in part, by any means is prohibited without the prior

written permission of Enclustra GmbH, Switzerland.

Although Enclustra GmbH believes that the information included in this publication is correct as of the date

of publication, Enclustra GmbH reserves the right to make changes at any time without notice.

All information in this document is strictly confidential and may only be published by Enclustra GmbH,

Switzerland.

All referenced trademarks are the property of their respective owners.

Document History

Version Date Author Comment

07 19.08.2019 DIUN Added information on revision 2 modules, voltage monitoring, power

supplies, heat sink, Linux how-to guide, JTAG interface, other style

updates

06 21.08.2018 DIUN Minor corrections and style updates

05 04.05.2017 DIUN Updated EEPROM map, block diagram and footprint information

04 27.12.2016 DIUN Added tool support information and updated USB 2.0 information

03 13.09.2016 DIUN Minor updates and corrections

02 02.06.2016 DIUN Several corrections

01 21.09.2015 DIUN Version 01

D-0000-408-002 2 / 53 Version 07, 19.08.2019

Table of Contents

1 Overview 6

1.1 General ................................................... 6

1.1.1 Introduction ................................................ 6

1.1.2 Warranty .................................................. 6

1.1.3 RoHS .................................................... 6

1.1.4 DisposalandWEEE ............................................ 6

1.1.5 Safety Recommendations and Warnings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

1.1.6 ElectrostaticDischarge .......................................... 7

1.1.7 Electromagnetic Compatibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

1.2 Features................................................... 7

1.3 Deliverables ................................................ 7

1.4 Accessories................................................. 8

1.4.1 ReferenceDesign ............................................. 8

1.4.2 EnclustraBuildEnvironment ....................................... 8

1.4.3 Mercury+PE1BaseBoard ........................................ 8

1.5 IntelToolSupport............................................. 9

2 Module Description 10

2.1 BlockDiagram............................................... 10

2.2 Module Configuration and Product Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.3 Article Numbers and Article Codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

2.4 TopandBottomViews .......................................... 13

2.4.1 TopView .................................................. 13

2.4.2 BottomView................................................ 13

2.5 Top and Bottom Assembly Drawings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14

2.5.1 TopAssemblyDrawing .......................................... 14

2.5.2 BottomAssemblyDrawing........................................ 14

2.6 ModuleFootprint ............................................. 15

2.7 MechanicalData.............................................. 15

2.8 ModuleConnector ............................................ 16

2.9 UserI/O................................................... 17

2.9.1 Pinout.................................................... 17

2.9.2 I/OPinExceptions............................................. 18

2.9.3 DifferentialI/Os .............................................. 19

2.9.4 I/OBanks.................................................. 19

2.9.5 VCC_IOUsage ............................................... 21

2.9.6 SignalTerminations ............................................ 22

2.9.7 HPSI/OPins ................................................ 22

2.10 Multi-Gigabit Transceiver (MGT) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2.11 Power.................................................... 24

2.11.1 PowerGenerationOverview....................................... 24

2.11.2 PowerEnable/PowerGood........................................ 25

2.11.3 VoltageSupplyInputs........................................... 25

2.11.4 VoltageSupplyOutputs ......................................... 26

2.11.5 PowerConsumption............................................ 26

2.11.6 HeatDissipation.............................................. 26

2.11.7 VoltageMonitoring ............................................ 27

2.12 ClockGeneration ............................................. 27

2.13 Reset .................................................... 28

2.14 LEDs..................................................... 28

2.15 DDR3LSDRAM............................................... 28

2.15.1 DDR3LSDRAMType ........................................... 29

2.15.2 SignalDescription............................................. 29

2.15.3 Termination................................................. 29

D-0000-408-002 3 / 53 Version 07, 19.08.2019

2.15.4 Parameters................................................. 29

2.16 QSPIFlash ................................................. 30

2.16.1 QSPIFlashType .............................................. 31

2.16.2 SignalDescription............................................. 31

2.16.3 QSPIFlashCorruptionRisk........................................ 31

2.17 SDCard................................................... 31

2.17.1 SignalDescription............................................. 32

2.18 eMMCFlash ................................................ 32

2.18.1 eMMCFlashType ............................................. 32

2.18.2 SignalDescription............................................. 32

2.19 GigabitEthernet.............................................. 33

2.19.1 EthernetPHYType............................................. 33

2.19.2 SignalDescription............................................. 33

2.19.3 ExternalConnectivity ........................................... 33

2.19.4 MDIOAddress............................................... 33

2.19.5 PHYConfiguration............................................. 33

2.20 DualFastEthernet............................................. 34

2.20.1 EthernetPHYType............................................. 34

2.20.2 SignalDescription............................................. 34

2.20.3 ExternalConnectivity ........................................... 35

2.20.4 MDIOAddress............................................... 35

2.20.5 PHYConfiguration............................................. 35

2.21 CypressFX3USB3.0Controller ..................................... 35

2.21.1 CypressFX3Type ............................................. 35

2.21.2 CypressFX3Pinout ............................................ 36

2.21.3 FunctionalDescription .......................................... 36

2.22 USB2.0 ................................................... 36

2.22.1 USBPHYType ............................................... 37

2.22.2 SignalDescription............................................. 37

2.23 Real-TimeClock(RTC)........................................... 37

2.23.1 RTCType .................................................. 37

2.24 SecureEEPROM .............................................. 37

2.24.1 EEPROMType ............................................... 37

3 Device Configuration 39

3.1 ConfigurationSignals........................................... 39

3.2 ModuleConnectorCDetection ..................................... 40

3.3 BootMode................................................. 40

3.4 JTAG..................................................... 41

3.4.1 JTAGonModuleConnector ....................................... 42

3.4.2 HPSJTAGConnector ........................................... 42

3.4.3 ExternalConnectivity ........................................... 43

3.5 PassiveSerialConfiguration ....................................... 44

3.6 eMMCBootMode............................................. 44

3.7 QSPIBootMode.............................................. 44

3.8 SDCardBootMode............................................ 44

3.9 eMMCFlashProgramming........................................ 44

3.10 QSPI Flash Programming via JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

3.11 QSPI Flash Programming from an External SPI Master . . . . . . . . . . . . . . . . . . . . . . . . 44

3.12 Enclustra Module Configuration Tool . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

4 I2C Communication 46

4.1 Overview .................................................. 46

4.2 SignalDescription............................................. 46

4.3 I2CAddressMap ............................................. 46

4.4 SecureEEPROM .............................................. 47

D-0000-408-002 4 / 53 Version 07, 19.08.2019

4.4.1 MemoryMap ............................................... 47

5 Operating Conditions 49

5.1 AbsoluteMaximumRatings ....................................... 49

5.2 Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 49

6 Ordering and Support 50

6.1 Ordering .................................................. 50

6.2 Support................................................... 50

D-0000-408-002 5 / 53 Version 07, 19.08.2019

1 Overview

1.1 General

1.1.1 Introduction

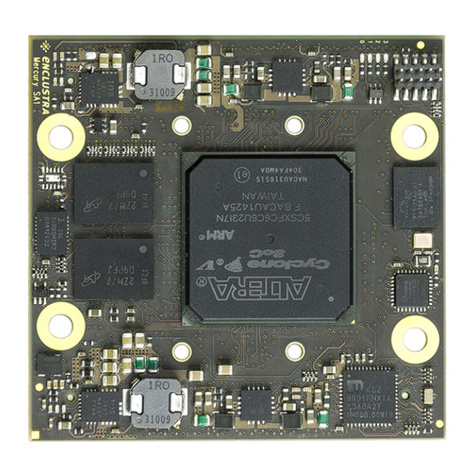

The Mercury+ SA2 SoC module combines the Altera Cyclone® V ARM® processor-based SoC (System-

on-Chip) device with fast DDR3L SDRAM, USB 3.0 controller and PHY, USB 2.0 PHY, PCIe® Gen1/Gen2 ×4,

Gigabit Ethernet and dual Fast Ethernet interfaces, multi-gigabit transceivers, high-speed LVDS I/O, and is

available in industrial temperature range, forming a complete and powerful embedded processing system.

The use of the Mercury+ SA2 SoC module, in contrast to building a custom SoC hardware, significantly

simplifies system design and thus shortens time to market and decreases the development effort of your

product.

Together with Mercury+ base boards, the Mercury+ SA2 SoC module allows the user to quickly build a

system prototype and start with application development.

The Enclustra Build Environment [14] is available for the Mercury+ SA2 SoC module. This build system allows

the user to quickly set up and run Linux on any Enclustra SoC module. It allows the user to choose the desired

target, and download all the required binaries, such as bitstream and preloader. It downloads and compiles

all required software, such as U-Boot, Linux, and BusyBox based root file system.

1.1.2 Warranty

Please refer to the General Business Conditions, available on the Enclustra website [1].

1.1.3 RoHS

The Mercury+ SA2 SoC module is designed and produced according to the Restriction of Hazardous Sub-

stances (RoHS) Directive (2011/65/EC).

1.1.4 Disposal and WEEE

The Mercury+ SA2 SoC module must be properly disposed of at the end of its life.

The Waste Electrical and Electronic Equipment (WEEE) Directive (2002/96/EC) is not applicable for the Mer-

cury+ SA2 SoC module.

1.1.5 Safety Recommendations and Warnings

Mercury+ modules are not designed to be “ready for operation” for the end-user. These can only be used

in combination with suitable base boards. Proper configuration of the hardware before usage is required.

Ensure that the power supply is disconnected from the board before inserting or removing the Mercury+

SA2 SoC module, connecting interfaces, replacing batteries, or connecting jumpers.

Touching the capacitors of the DC-DC converters can lead to voltage peaks and permanent damage; over-

voltage on power or signal lines can also cause permanent damage to the module.

D-0000-408-002 6 / 53 Version 07, 19.08.2019

Warning!

It is possible to mount the Mercury+ SA2 SoC module the wrong way round on the base board - always

check that the mounting holes on the base board are aligned with the mounting holes of the Mercury+

SA2 SoC module.

The base board and module may be damaged if the module is mounted the wrong way round and

powered up.

1.1.6 Electrostatic Discharge

Electronic boards are sensitive to electrostatic discharge (ESD). Please ensure that the product is handled

with care and only in an ESD-protected environment.

1.1.7 Electromagnetic Compatibility

The Mercury+ SA2 SoC module is a Class A product and is not intended for use in domestic environments.

The product may cause electromagnetic interference, for which appropriate measures must be taken.

1.2 Features

•Altera Cyclone V SOC 5CSTFD6D5F31I7N

•ARM dual-core Cortex A9

•Altera Cyclone V 28 nm FPGA fabric

•294 user I/Os up to 3.3 V

•18 ARM peripheral I/Os (SPI, SDIO, CAN, I2C, UART)

•202 FPGA I/Os (single-ended or differential)

•32 FPGA I/Os (single-ended or differential) shared with USB 3.0

•42 MGT signals (clock and data)

•9 MGTs @ 6.144 Gbit/sec and 3 reference input clock differential pairs

•PCIe Gen2 ×4 (Altera PCIe hardened IP block)

•2 GB DDR3L SDRAM

•64 MB quad SPI flash

•16 GB eMMC flash (starting with revision 2)

•Gigabit Ethernet

•Dual Fast Ethernet

•Cypress EZ-USB FX3 USB 3.0 device controller

•USB 2.0 host/device

•Real-time clock

•CAN, UART, SPI, I2C, SDIO/MMC

•5 to 15 V supply voltage

1.3 Deliverables

•Mercury+ SA2 SoC module

•Mercury+ SA2 SoC module documentation, available via download:

•Mercury+ SA2 SoC Module User Manual (this document)

•Mercury+ SA2 SoC Module Reference Design [2]

•Mercury+ SA2 SoC Module IO Net Length Excel Sheet [3]

•Mercury+ SA2 SoC Module FPGA Pinout Excel Sheet [4]

•Mercury+ SA2 SoC Module User Schematics (PDF) [5]

•Mercury+ SA2 SoC Module Known Issues and Changes [6]

D-0000-408-002 7 / 53 Version 07, 19.08.2019

•Mercury+ SA2 SoC Module Footprint (Altium, Eagle, Orcad and PADS) [7]

•Mercury+ SA2 SoC Module 3D Model (PDF) [8]

•Mercury+ SA2 SoC Module STEP 3D Model [9]

•Module Pin Connection Guidelines [10]

•Mercury Master Pinout [11]

•Enclustra Modules Heat Sink Application Note [17]

•Enclustra Build Environment [14] (Linux build environment; refer to Section 1.4.2 for details)

•Enclustra Build Environment How-To Guide [15]

1.4 Accessories

1.4.1 Reference Design

The Mercury+ SA2 SoC module reference design features an example configuration for the Cyclone V SoC

device, together with an example top level HDL file for the user logic.

A number of software applications are available for the reference design, that show how to initialize the

peripheral controllers and how to access the external devices. Pre-compiled binaries are included in the

archive, so that the user can easily check that the hardware is functional.

The reference design can be downloaded from the Enclustra download page [2].

1.4.2 Enclustra Build Environment

The Enclustra Build Environment (EBE) [14] enables the user to quickly set up and run Linux on any Enclustra

SoC module or system board. It allows the user to choose the desired target, and download all the required

binaries, such as bitstream and preloader/bootloader. It downloads and compiles all required software, such

as U-Boot, Linux, and BusyBox based root file system.

The Enclustra Build Environment features a graphical user interface (GUI) and a command line interface (CLI)

that facilitates the automatic build flow.

The Enclustra Build Environment How-To Guide [15] describes in more detail how to use the EBE to customize

the provided software for the user application. The document provides information on the configuration

options for U-boot, Linux kernel and Buildroot, debugging possibilities for Linux applications, customization

of device trees and integration of existing or new kernel drivers.

1.4.3 Mercury+ PE1 Base Board

•168-pin Hirose FX10 module connectors (PE1-200: 2 connectors; PE1-300/400: 3 connectors)

•System controller

•Power control

•System monitor (PE1-300/400)

•Current sense (PE1-300/400)

•Low-jitter clock generator (PE1-300/400)

•Accelerometer/magnetometer/temperature sensor (PE1-300/400)

•microSD card holder

•User EEPROM

•eMMC managed NAND flash (PE1-300/400)

•PCIe ×4 interface

•USB 3.0 device connector

•USB 2.0 host connector (PE1-200: 1 connector; PE1-300/400: 4 connectors)

•Micro USB 2.0 device (UART, SPI, I2C, JTAG) connector

•2×RJ45 Gigabit Ethernet connectors

•mPCIe/mSATA card holder (USB only) (PE1-300/400)

•SIM card holder (optional, PE1-300/400 only)

D-0000-408-002 8 / 53 Version 07, 19.08.2019

•SMA clock and data in/out (optional, PE1-300/400 only)

•1×FMC LPC connector (PE1-200)

•1×FMC HPC connector (PE1-300)

•2×FMC LPC connector (PE1-400)

•2×40-pin Anios pin header

•3×12-pin Pmod™ pin header

•5 to 15 V DC supply voltage

•USB bus power (with restrictions)

Please note that the available features depend on the equipped Mercury module type and on the selected

base board variant.

1.5 Intel Tool Support

The SoC devices equipped on the Mercury+ SA2 SoC module are supported by the Quartus Prime Lite

Edition (or Quartus II Web Edition, for older software versions), which is available free of charge. Please

contact Intel for further information.

D-0000-408-002 9 / 53 Version 07, 19.08.2019

2 Module Description

2.1 Block Diagram

Figure 1: Hardware Block Diagram

The main component of the Mercury+ SA2 SoC module is the Intel Cyclone V SoC device. Most of its I/O

pins are connected to the Mercury module connectors, making up to 252 regular user I/Os available to the

user. Further, nine multi-gigabit transceivers with support for PCIe Gen2 ×4 are available on the module

connectors.

The SoC device can boot from the on-board QSPI flash or from an external SD card. For development pur-

poses, a JTAG interface is connected to Mercury module connector.

The memory subsystem is built from a 64 MB QSPI flash and 2 GB DDR3L SDRAM in the standard config-

uration. Starting with revision 2 modules, a 16 GB eMMC flash is available on the module for booting the

SoC device or for storing user data.

Further, the module is equipped with a Gigabit Ethernet PHY, two Fast Ethernet PHYs for dual Fast Ethernet

implementation and a USB 2.0 PHY, making it ideal for communication applications.

A Cypress FX3 USB 3.0 controller is fitted on the module to easily implement a communication link to a host

PC.

D-0000-408-002 10 / 53 Version 07, 19.08.2019

A real-time clock is available on the module and is connected to the global I2C bus.

On-board clock generation is based on a 50 MHz crystal oscillator.

The module’s internal supply voltages are generated from a single input supply of 5 - 15 V DC. Some of

these voltages are available on the Mercury module connectors to supply circuits on the base board.

Four LEDs are connected to the SoC pins for status signaling.

2.2 Module Configuration and Product Codes

Table 1 describes the available standard module configurations. Custom configurations are available; please

contact Enclustra for further information.

Product Code SoC DDR3L SDRAM PCI Express Temperature Range

ME-SA2-D6-7I-D11 5CSTFD6D5F31I7N 2 GB X-40 to +85◦C

Table 1: Standard Module Configurations

The product code indicates the module type and main features. Figure 2 describes the fields within the

product code.

Figure 2: Product Code Fields

Please note that for the first revision modules or early access modules, the product code may not respect

entirely this naming convention. Please contact Enclustra for details on this aspect.

2.3 Article Numbers and Article Codes

Every module is uniquely labeled, showing the article number and serial number. An example is presented

in Figure 3.

D-0000-408-002 11 / 53 Version 07, 19.08.2019

Figure 3: Module Label

The correspondence between article number and article code is shown in Table 2. The article code repre-

sents the product code, followed by the revision; the R suffix and number represent the revision number.

The revision changes and product known issues are described in the Mercury+ SA2 SoC Module Known

Issues and Changes document [6].

Article Number Article Code

EN101010 ME-SA2-D6-7I-D11-R1

EN102326 ME-SA2-D6-7I-D11-R2

Table 2: Article Numbers and Article Codes

D-0000-408-002 12 / 53 Version 07, 19.08.2019

2.5 Top and Bottom Assembly Drawings

2.5.1 Top Assembly Drawing

Figure 6: Module Top Assembly Drawing

2.5.2 Bottom Assembly Drawing

Figure 7: Module Bottom Assembly Drawing

Please note that depending on the hardware revision and configuration, the module may look slightly dif-

ferent than shown in this document.

D-0000-408-002 14 / 53 Version 07, 19.08.2019

2.6 Module Footprint

Figure 8 shows the dimensions of the module footprint on the base board.

Enclustra offers Mercury and Mercury+ modules of various geometries having widths of 56, 64, 72 or 74

mm and having different topologies for the mounting holes. If different module types shall be fixed on the

base board by screws, additional mounting holes may be required to accommodate different modules. The

footprints of the module connectors for the base board design are available for different PCB design tools

(Altium, PADS, Eagle, Orcad) [7] and include the required information on the module sizes and holes.

The maximum component height on the base board under the module is dependent on the connector type.

Please refer to the Hirose FX10 series product website for detailed connector information [12].

The three connectors are called A (J800), B (J801) and C (J900).

Figure 8: Module Footprint - Top View

Warning!

It is possible to mount the Mercury+ SA2 SoC module the wrong way round on the base board - always

check that the mounting holes on the base board are aligned with the mounting holes of the Mercury+

SA2 SoC module.

2.7 Mechanical Data

Table 3 describes the mechanical characteristics of the Mercury+ SA2 SoC module. A 3D model (PDF) and

a STEP 3D model are available [8], [9].

D-0000-408-002 15 / 53 Version 07, 19.08.2019

Symbol Value

Size 74 ×54 mm

Component height top 5.0 mm

Component height bottom 1.45 mm

Weight 29 g

Table 3: Mechanical Data

2.8 Module Connector

Three Hirose FX10 168-pin 0.5 mm pitch headers with a total of 504 pins have to be integrated on the base

board. Up to four M3 screws may be used to mechanically fasten the module to the base board. Do not

use excessive force to tighten the screws, as this could damage the module.

The pinout of the module connector is found in the Mercury Master Pinout Excel Sheet [11]. The connector

is available in different packaging options and different stacking heights. Some examples are presented in

Table 4. Please refer to the connector datasheet for more information.

Reference Type Description

Mercury module connector FX10A-168S-SV Hirose FX10, 168-pin, 0.5 mm pitch

Base board connector FX10A-168P-SV(71) Hirose FX10, 168-pin, 0.5 mm pitch, 4 mm stacking

height

Base board connector FX10A-168P-SV1(71) Hirose FX10, 168-pin, 0.5 mm pitch, 5 mm stacking

height

Table 4: Module Connector Types

Figure 9 indicates the pin numbering for the Mercury module connectors from the top view of the base

board. The connector pins are numbered as follows:

•Connector A: from J800-1 to J800-168

•Connector B: from J801-1 to J801-168

•Connector C: from J900-1 to J900-168

Figure 9: Pin Numbering for the Module Connector

D-0000-408-002 16 / 53 Version 07, 19.08.2019

Warning!

Do not use excessive force to latch a Mercury module into the Mercury connectors on the base board,

as this could damage the module and the base board; always make sure that the module is correctly

oriented before mounting it into the base board.

2.9 User I/O

2.9.1 Pinout

Information on the Mercury+ SA2 SoC module pinout can be found in the Enclustra Mercury Master Pinout

[11], and in the additional document Enclustra Module Pin Connection Guidelines [10].

Warning!

Please note that the pin types on the schematics symbol of the module connector and in the Master

Pinout document are for reference only. On the Mercury+ SA2 SoC module it may be possible that

the connected pins do not have the targeted functions (such as primary clocks, differential pins, MGT

signals, etc).

The naming convention for the user I/Os is:

IO_B<BANK>_<FUNCTION>_<PIN_NAME>_<PACKAGE_PIN>_<POLARITY>

For example, IO_B4A_RX_B42_AE17_P is located on pin AE17 of I/O bank 4A, and when used in a differential

pair it is a receive pin and has positive polarity.

The naming convention for the user I/Os shared with the FX3 device is:

FX3_<FX3_FUNCTION>_B<BANK>_<_FUNCTION>_<PACKAGE_PIN>.

The clock capable pins are marked with “CLK” in the signal name. For details on their function and usage,

please refer to the Intel documentation.

Table 5 includes information related to the total number of I/Os available in each I/O bank and possible

limitations.

Please note that Cyclone V devices can only use I/O pins marked with “RX” in the signal name as differential

inputs and only pins marked with “TX” as differential outputs. The I/O pins marked with “CLK” are receive-

only differential signals and can be used as dedicated clock differential inputs. All pins can be used as

single-ended inputs or outputs.

D-0000-408-002 17 / 53 Version 07, 19.08.2019

Signal Name Signals Pairs Differential Single-ended I/O Bank

IO_B5A_RX<...> 16 8 In In/Out 5A

IO_B5A_TX<...> 16 8 Out In/Out 5A

IO_B5B_RX<...> 4 2 In In/Out 5B

IO_B5B_CLK<...> 4 2 In In/Out 5B

IO_B5B_TX<...> 8 4 Out In/Out 5B

IO_B4A_RX<...> 36 18 In In/Out 4A

IO_B4A_CLK<...> 4 2 In In/Out 4A

IO_B4A_TX<...> 40 20 Out In/Out 4A

IO_B8A_RX<...> 36 18 In In/Out 8A

IO_B8A_CLK<...> 4 2 In In/Out 8A

IO_B8A_TX<...> 34 17 Out In/Out 8A

FX3_<...> 32 16 In or Out In/Out 3B

Shared with the FX3 pins

Total 234 117 - - -

Table 5: User I/Os

Warning!

The FX3 signals must be left unconnected on the module connector C when using the USB 3.0 on the

Mercury+ SA2 SoC module.

Warning!

When using the signals on FPGA bank 3B as regular FPGA I/Os, the FX3 must be kept by driving the

FX3_RESET#_LS signal (pin AK2) low.

2.9.2 I/O Pin Exceptions

The I/O pin exceptions are pins with special functions or restrictions (for example, when used in combination

with certain Mercury boards they may have a specific role).

Table 6 lists the I/O pin exceptions on the Mercury+ SA2 SoC module.

D-0000-408-002 18 / 53 Version 07, 19.08.2019

I/O Name Module Connector Pin Description

HPS_GPIO59_MISO A-104 Connected via a 47 kΩresistor to

IO_B5A_RX_R6_PERST#_W22_N pin (A-36) for PCIe

PERST# connection implementation

HPS_GPIO57_CLK A-98 Can optionally be connected via a 47 kΩresistor to

IO_B5A_TX_R3_CVP_AH29_N pin (A-21) for Configura-

tion via Protocol (CVP) implementation (CVP pin can

be connected to PCIe WAKE# pin)

Table 6: I/O Pin Exceptions

When the Mercury+ SA2 SoC module is used in combination with a Mercury+ PE1 base board as a PCIe

device, the PERST# signal coming from the PCIe edge connector on the module connector pin A-104

(HPS_GPIO59_MISO) is driven further to IO_B5A_RX_R6_PERST#_W22_N.

Because the PCIe block inside the FPGA logic side requires this reset signal, the PERST# signal is connected

to the FPGA pin IO_B5A_RX_R6_PERST#_W22_N via a 47 kΩresistor. In situations in which a custom board is

used or PCIe functionality is not required, this FPGA pin can be used in the same manner as a regular I/O pin.

The connection of the CVP pin to the PCIe WAKE# pin on the Mercury+ PE1 base board is made in a similar

manner - note that the connection is not available in the standard configuration, as not all PCIe cards support

the wake function. Details on the CVP implementation can be found in the Altera CVP documentation [23]

and details on the WAKE# pin are available in the PCIe specification.

2.9.3 Differential I/Os

When using differential pairs, a differential impedance of 100 Ωmust be matched on the base board, and

the two nets of a differential pair must have the same length.

The information regarding the length of the signal lines from the SoC device to the module connector is

available in Mercury+ SA2 SoC Module IO Net Length Excel Sheet [3]. This enables the user to match the

total length of the differential pairs on the base board if required by the application.

Please note that Cyclone V devices can only use I/O pins marked with “RX” in the signal name as differential

inputs and only pins marked with “TX” as differential outputs. All pins can be used as single-ended inputs

or outputs.

Warning!

Check Mercury+ SA2 SoC module pinout with Quartus before producing your own base board hard-

ware, to make sure that all pins are used according to the correct direction.

2.9.4 I/O Banks

Table 7 describes the main attributes of the FPGA and Hard Processing System (HPS) I/O banks, and indicates

which peripherals are connected to each I/O bank. All I/O pins within a particular I/O bank must use the

same I/O (VCC_IO) and reference (VREF) voltages.

D-0000-408-002 19 / 53 Version 07, 19.08.2019

Bank Connectivity VCC_IO VREF

MGT Bank L0 Module connector 1.1 V -

MGT Bank L1 Module connector 1.1 V -

MGT Bank L2 Module connector 1.1 V -

Bank 3A Configuration, Fast Ethernet PHYs User selectable 0 V

VCC_CFG_HPS_B3A1

Bank 3B Module connector User selectable 0.5 ×VCC_IO_B3B_B4A

VCC_IO_B3B_B4A

Bank 4A Module connector User selectable 0.5 ×VCC_IO_B3B_B4A

VCC_IO_B3B_B4A

Bank 5A Module connector User selectable 0.5 ×VCC_IO_B5A_B5B

VCC_IO_B5A_B5B

Bank 5B Module connector User selectable 0.5 ×VCC_IO_B5A_B5B

VCC_IO_B5A_B5B

Bank 8A Module connector, LEDs User selectable 0.5 ×VCC_IO_B8A

VCC_IO_B8A

HPS Bank 6A DDR3L SDRAM 1.35 V 0.68 V

HPS Bank 6B DDR3L SDRAM 1.35 V 0.68 V

HPS Bank 7A Module connector, I2C, LEDs VCC_CFG_HPS_B3A 0 V

HPS Bank 7B Gigabit Ethernet PHY, QSPI flash VCC_CFG_HPS_B3A 0 V

HPS Bank 7C Module connector, eMMC flash VCC_CFG_HPS_B3A 0 V

HPS Bank 7D USB PHY VCC_CFG_HPS_B3A 0 V

Table 7: I/O Banks

1On revision 1 modules, FPGA bank 3A was powered with 1.8 V instead of VCC_CFG_HPS voltage - this connection contradicted the

Mercury pinout convention and was corrected on revision 2 modules. The VCC_CFG_HPS voltage signal has been therefore renamed

to reflect the new connection: VCC_CFG_HPS_B3A.

D-0000-408-002 20 / 53 Version 07, 19.08.2019

This manual suits for next models

3

Table of contents

Other Enclustra Control Unit manuals

Enclustra

Enclustra Mercury SA1 SoC Module User manual

Enclustra

Enclustra Mercury+ KX2 User manual

Enclustra

Enclustra Mars ZX2 User manual

Enclustra

Enclustra Mercury XU5 User manual

Enclustra

Enclustra Mercury+ XU8 User manual

Enclustra

Enclustra Mercury ZX5 Series User manual

Enclustra

Enclustra Mars XU3 User manual

Enclustra

Enclustra Mercury+ XU7 User manual

Enclustra

Enclustra Mercury+ XU1 User manual

Enclustra

Enclustra Mars AX3 User manual