PMC-CPU/440

Status: released

Contents

1 Overview........................................................................................................................................... 8

1.1 Description Of The PMC CPU/440 Module...............................................................................8

1.2 Technical Data..........................................................................................................................9

1.2.1 General..............................................................................................................................9

1.2.2 CPU Core..........................................................................................................................9

1.2.3 Realtime Clock (RTC)........................................................................................................9

1.2.4 PCI Interface.................................................................................................................... 10

1.2.5 Serial Interfaces............................................................................................................... 10

1.2.6 CAN Interfaces.................................................................................................................10

1.2.7 Ethernet Interfaces...........................................................................................................11

1.2.8 USB Interface (Host or Device)........................................................................................11

2 Installation Instructions....................................................................................................................11

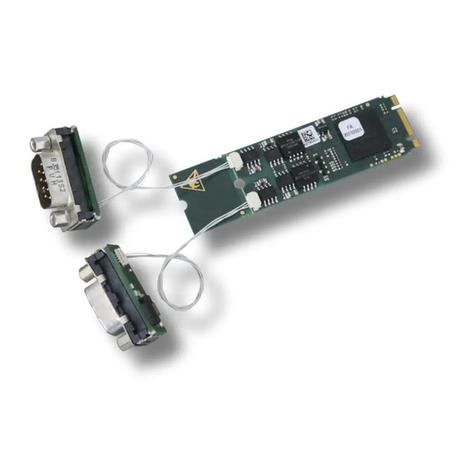

3 Front Panel..................................................................................................................................... 11

4 Top and Bottom Side......................................................................................................................12

5 JTAG Debug Interface....................................................................................................................14

5.1 JTAG Chain Description..........................................................................................................14

5.2 JTAG Connector (X5)..............................................................................................................14

6 PMC Connectors............................................................................................................................. 16

6.1 PMC P1 Connector.................................................................................................................. 16

6.2 PMC P2 Connector.................................................................................................................. 17

6.3 PMC P4 I/O Connector............................................................................................................18

6.3.1 Pinout............................................................................................................................... 18

6.3.2 Signal Description............................................................................................................19

7 Local Memory Map......................................................................................................................... 20

8 Interrupts......................................................................................................................................... 22

8.1 External Interrupt Assignment.................................................................................................22

8.2 PCI Interrupt Handling.............................................................................................................22

8.2.1 Monarch Mode.................................................................................................................22

8.2.2 Asserting PCI Interrupts In Non monarch Mode...............................................................22

8.2.3 Asserting Local Interrupts From PCI Bus.........................................................................22

9 PCI Configuration............................................................................................................................ 22

10 Bootloader.....................................................................................................................................23

10.1 License.................................................................................................................................. 23

10.2 Configuration and Console Access........................................................................................23

10.3 Default Bootloader Environment............................................................................................24

10.4 Flash Update......................................................................................................................... 25

10.5 BSP Commands....................................................................................................................26

10.5.1 irigb Get / Set IRIG B time...........................................................................................26

10.5.2 inta – Assert / Deassert PCI interrupt line on PMC440...................................................26

10.5.3 sbe – configure CPU strapping......................................................................................27

10.5.4 fifo – Control Hardware FIFO Module............................................................................27

10.5.5 loadpci – Start PCI firmware loading..............................................................................28

10.5.6 fpga command...............................................................................................................29

10.5.7 painit Command............................................................................................................. 30

10.5.8 USB............................................................................................................................... 30

10.5.9 resetout Command........................................................................................................30

10.6 Special Environment Variables..............................................................................................31

10.6.1 pcidelay Variable............................................................................................................31

10.6.2 ptm1la, ptm1ms, ptm2la and ptm2ms Variables............................................................31

10.6.3 pram Variable.................................................................................................................31

User Manual V.2027.21

Filename: PMC

CPU440_Manual_en_13.odt

Revision 1.3

2012 06 11

All rights reserved.

Copyright © esd gmbh 2012 Page

6 of 49