3.3.3 Pinout.............................................................................................................................14

3.4 Clock .................................................................................................................................14

3.4.1 Overview........................................................................................................................14

3.4.2 Clock ..............................................................................................................................14

3.4.3 Pinout.............................................................................................................................14

3.5 LED ...................................................................................................................................15

3.5.1 Overview........................................................................................................................15

3.5.2 LED Circuit.....................................................................................................................15

3.5.3 Pins Distribution.............................................................................................................15

3.6 Switches ...........................................................................................................................16

3.6.1 Overview........................................................................................................................16

3.6.2 Switch Circuit .................................................................................................................16

3.6.3 Pinout.............................................................................................................................16

3.7 Key.................................................................................................................................... 17

3.7.1 Overview........................................................................................................................17

3.7.2 Key Circuit .....................................................................................................................17

3.7.3 Pinout.............................................................................................................................17

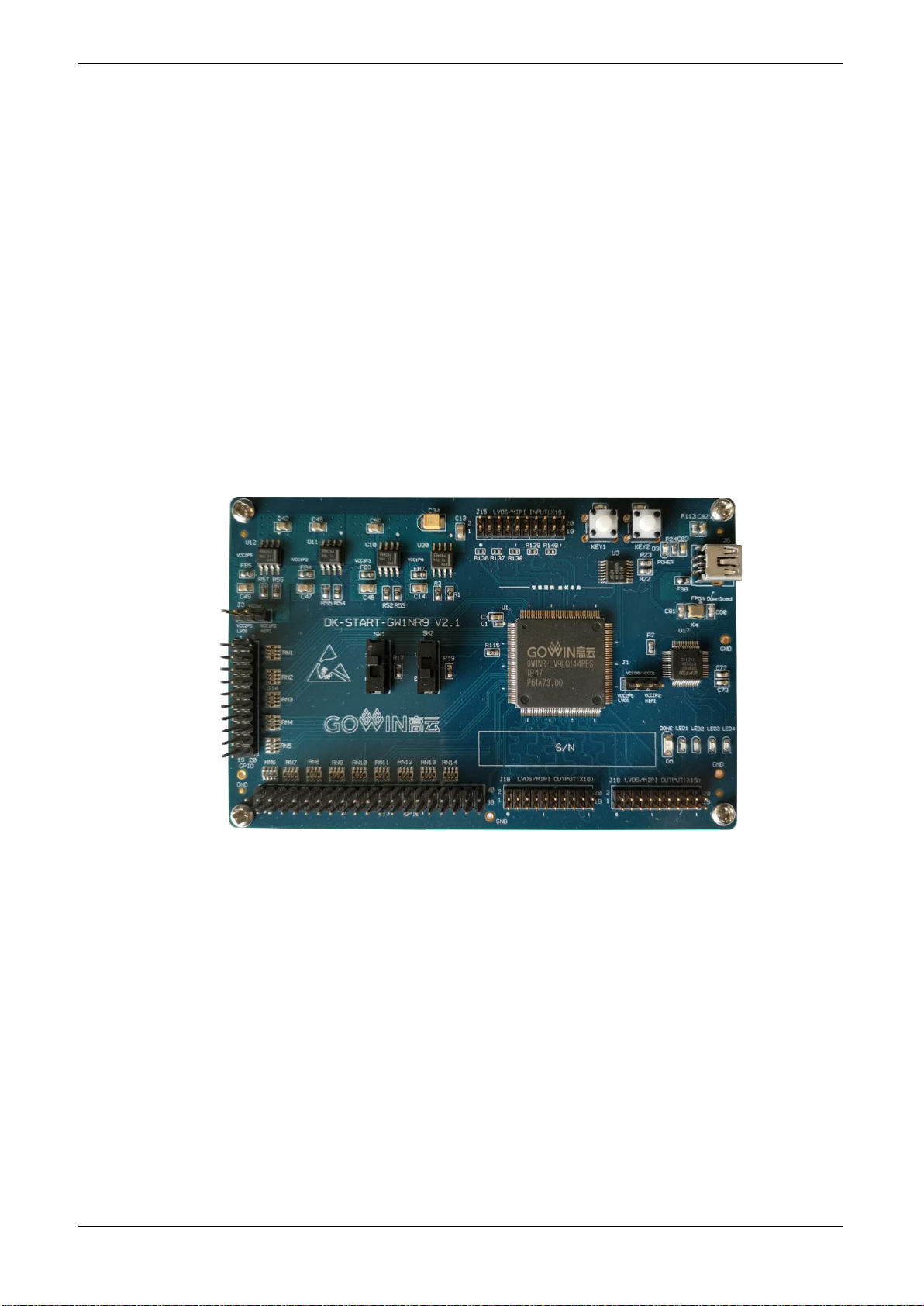

3.8 GPIO .................................................................................................................................18

3.8.1 Overview........................................................................................................................18

3.8.2 GPIO Circuit...................................................................................................................18

3.8.3 Pinout.............................................................................................................................19

3.9 MIPI/LVDS ........................................................................................................................21

3.9.1 Overview........................................................................................................................21

3.9.2 MIPI/LVDS Circuit ..........................................................................................................21

3.9.3 Pinout.............................................................................................................................22

4Considerations ............................................................................................25

5Gowin Software ...........................................................................................26

6Quick Start ...................................................................................................27