3.3.3 Pins Distribution.............................................................................................................13

3.4 Clock, Reset ..................................................................................................................... 13

3.4.1 Overview........................................................................................................................13

3.4.2 Clock, Reset ..................................................................................................................13

3.4.3 Pins Distribution.............................................................................................................14

3.5 LED...................................................................................................................................14

3.5.1 Overview........................................................................................................................14

3.5.2 LED Circuit.....................................................................................................................14

3.5.3 Pins Distribution.............................................................................................................15

3.6 Switches ........................................................................................................................... 15

3.6.1 Overview........................................................................................................................15

3.7 Key....................................................................................................................................15

3.7.1 Overview........................................................................................................................15

3.7.2 Key Circuit .....................................................................................................................15

3.7.3 Pins Distribution.............................................................................................................16

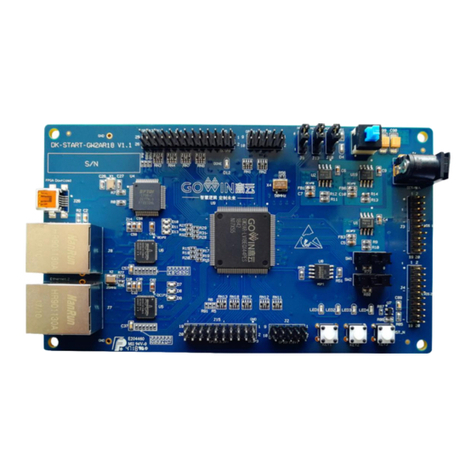

3.8 GPIO.................................................................................................................................16

3.8.1 Overview........................................................................................................................16

3.8.2 GPIO Circuit................................................................................................................... 16

3.8.3 Pins Distribution.............................................................................................................16

3.9 MIPI/LVDS ........................................................................................................................17

3.9.1 Overview........................................................................................................................17

3.9.2 MIPI/LVDS Circuit..........................................................................................................17

3.9.3 Pins Distribution.............................................................................................................18

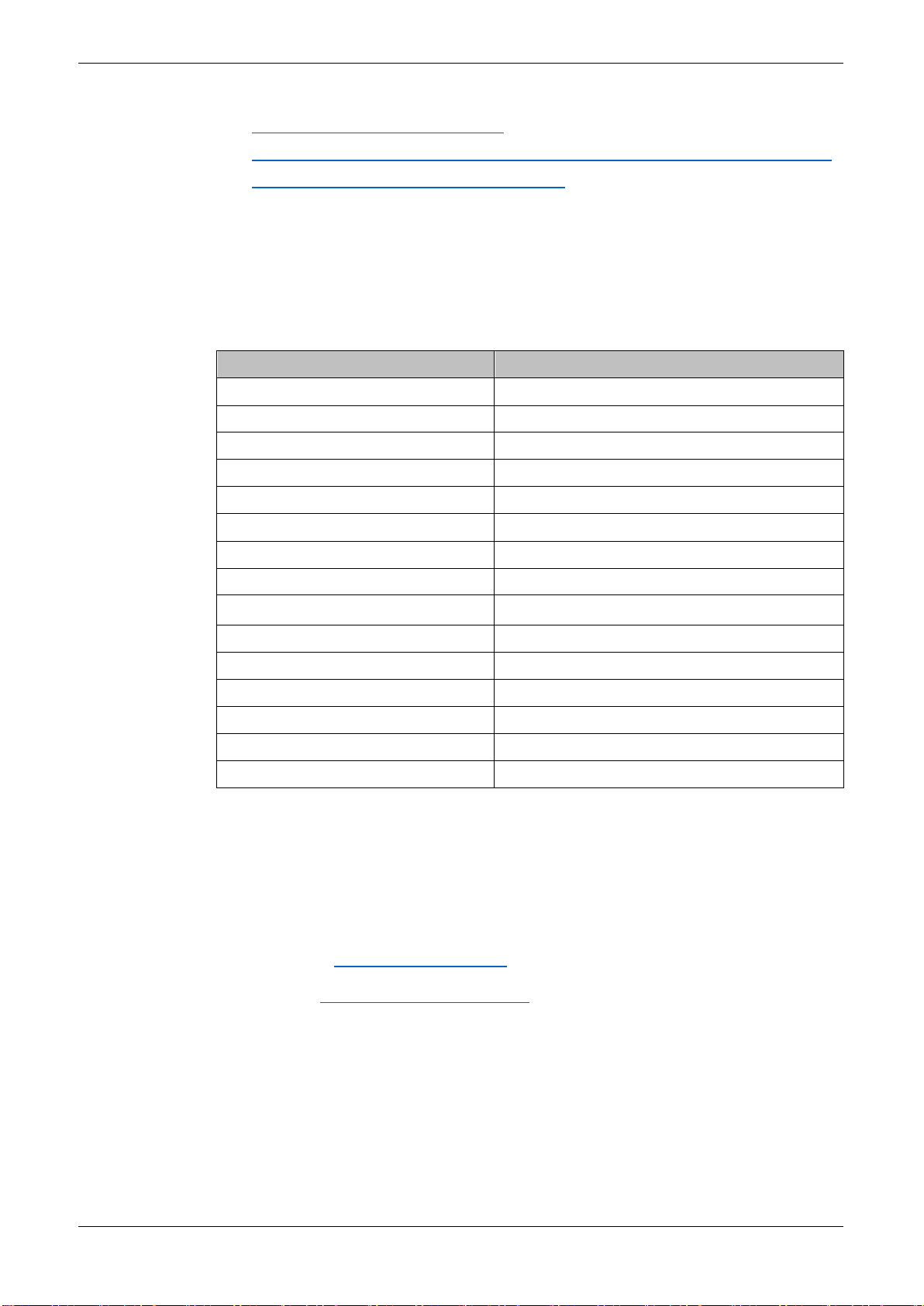

3.10 RS232.............................................................................................................................20

3.10.1 Overview......................................................................................................................20

3.10.2 RS232 Circuit...............................................................................................................20

3.10.3 Pins Distribution...........................................................................................................20

4Precautions..................................................................................................21

5Gowin Software...........................................................................................22