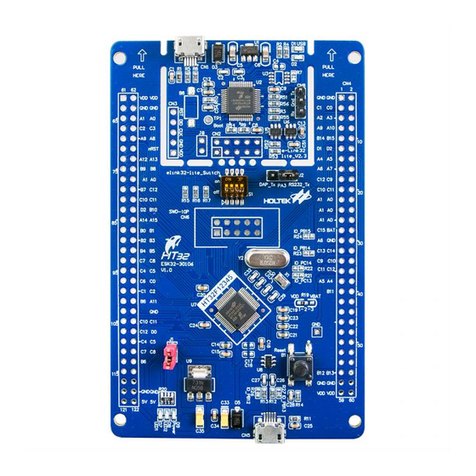

Rev. 1.10 7 of 366 November 09, 2018

32-Bit Arm®Cortex®-M0+ MCU

HT32F52220/HT32F52230

Table of Contents

Table of Contents

Quadrature Decoder ..................................................................................................................... 191

Output Stage................................................................................................................................. 193

Update Management .................................................................................................................... 197

Single Pulse Mode........................................................................................................................ 198

Asymmetric PWM Mode ............................................................................................................... 200

Trigger ADC Start.......................................................................................................................... 201

Register Map ..................................................................................................................... 201

Register Descriptions......................................................................................................... 202

Timer Counter Conguration Register – CNTCFR ....................................................................... 202

Timer Mode Conguration Register – MDCFR............................................................................. 203

Timer Trigger Conguration Register – TRCFR............................................................................ 206

Timer Counter Register – CTR ..................................................................................................... 207

Channel 0 Input Conguration Register – CH0ICFR .................................................................... 208

Channel 1 Input Conguration Register – CH1ICFR .................................................................... 209

Channel 2 Input Conguration Register – CH2ICFR .....................................................................211

Channel 3 Input Conguration Register – CH3ICFR .................................................................... 212

Channel 0 Output Conguration Register – CH0OCFR ............................................................... 214

Channel 1 Output Conguration Register – CH1OCFR ............................................................... 216

Channel 2 Output Conguration Register – CH2OCFR ............................................................... 217

Channel 3 Output Conguration Register – CH3OCFR ............................................................... 219

Channel Control Register – CHCTR............................................................................................. 221

Channel Polarity Conguration Register – CHPOLR.................................................................... 222

Timer Interrupt Control Register – DICTR .................................................................................... 223

Timer Event Generator Register – EVGR..................................................................................... 224

Timer Interrupt Status Register – INTSR...................................................................................... 225

Timer Counter Register – CNTR................................................................................................... 227

Timer Prescaler Register – PSCR ................................................................................................ 228

Timer Counter Reload Register – CRR ........................................................................................ 229

Channel 0 Capture/Compare Register – CH0CCR ...................................................................... 230

Channel 1 Capture/Compare Register – CH1CCR ...................................................................... 231

Channel 2 Capture/Compare Register – CH2CCR ...................................................................... 232

Channel 3 Capture/Compare Register – CH3CCR ...................................................................... 233

Channel 0 Asymmetric Compare Register – CH0ACR................................................................. 234

Channel 1 Asymmetric Compare Register – CH1ACR................................................................. 234

Channel 2 Asymmetric Compare Register – CH2ACR................................................................. 235

Channel 3 Asymmetric Compare Register – CH3ACR................................................................. 235

14 Basic Function Timer (BFTM).......................................................................... 236

Introduction ........................................................................................................................ 236

Features............................................................................................................................. 236

Functional Description ....................................................................................................... 237

Repetitive Mode............................................................................................................................ 237

One Shot Mode............................................................................................................................. 238

Trigger ADC Start.......................................................................................................................... 238