HTG2190

Rev. 1.20 10 July 5, 2002

forms a short jump. The destination must be within 256

locations.

When a control transfer takes place, an additional

dummy cycle is required.

Program memory -ROM

The program memory, which contains executable pro-

gram instructions, data and table information, is com-

posed of a 65536 x 16 bit format. However as the PC

(program counter) is comprised of only 13 bits, the re-

maining 3 ROM address bits are managed by dividing

the program memory into 8 banks, each bank having a

range between 0000H and 1FFFH. To move from the

present ROM bank to a different ROM bank, the higher 3

bits of the ROM address are set by the BP (Bank

Pointer), while the remaining 13 bits of the PC are set in

the usual way by executing the appropriate jump or call

instruction. As the full 16 address bits are latched during

the execution of a call or jump instruction, the correct

value of the BP must first be setup before a jump or call

is executed. When either a software or hardware inter-

rupt is received, note that no matter which ROM bank

the program is in the program will always jump to the ap-

propriate interrupt service address in Bank 0. The origi-

nal full 16 bit address will be stored on the stack and

restored when the relevant RET/RETI instruction is exe-

cuted, automatically returning the program to the origi-

nal ROM bank. This eliminates the need for

programmers to manage the BP when interrupts occur.

Certain locations in Bank 0 of program memory are re-

served for special usage:

·ROM Bank 0 (BP5~BP7=000B)

The ROM bank 0 ranges from 0000H to 1FFFH.

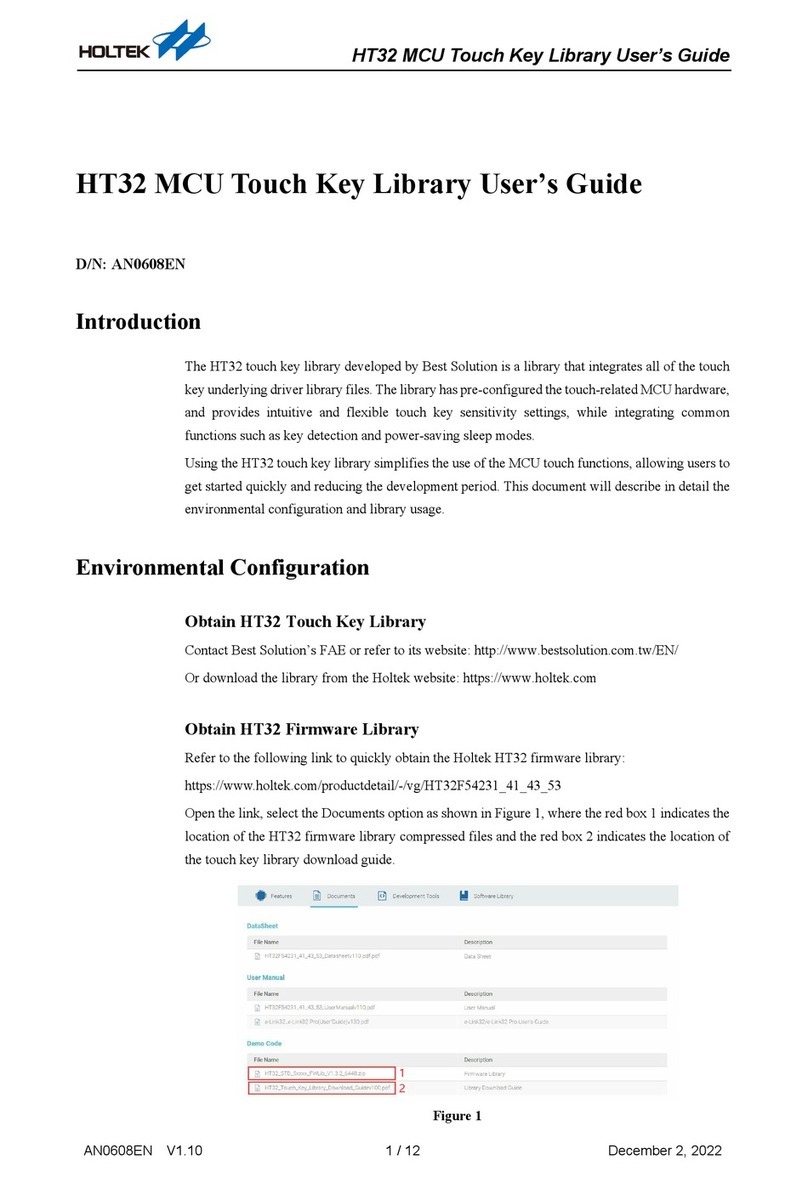

·Location 000H

This area is reserved for the initialization program. Af-

ter a chip reset, the program always begins execution

at location 000H.

·Location 004H

This area is reserved for the external interrupt or serial

input interrupt service routine. If the INT input pin is

activated, and the interrupt is enabled and the stack is

not full, the program will jump to location 004H and be-

gins execution.

·Location 008H/00CH

This area is reserved for the Timer/Event Counter 0/1 in-

terrupt service program. If a timer interrupt results from a

Timer/Event Counter 0/1 overflow, and if the interrupt is

enabled and the stack is not full, the program will jump to

location 008H/00CH and begins execution.

·Location 010H/014H

This area is reserved for the timer 2/3 interrupt service

program. If a timer interrupt resulting from a timer 2/3

overflow, and if the interrupt is enabled and the stack

is not full, the program will jump to location

010H/014H and begins execution.

·Location 018H

This area is reserved for the PWM D/A buffer empty

interrupt service program. After the system latch a D/A

code at RAM address 28H, the interrupt is enable, and

the stack is not full, the program begins execution at

location 018H.

·Location 020H

For best condition, this location is reserved as the be-

ginning when writing a program.

·ROM Bank 1~7 (BP5~BP7=001B~111)

The range of the ROM starts from n000H to

(n+1)FFFH. (n=2,4,6,8,10,12,14)

·Table location

Any location in the ROM space can be used as look up

table. The instructions TABRDC [m] (use for any

bank) and TABRDL [m] (only used for last page of pro-

gram ROM) transfers the contents of the lower-order

byte to the specified data memory, and the

higher-order byte to TBLH (08H). Only the destination

of the lower-order byte in the table is well-defined, the

0000H

0004H

0008H

D e v i c e i n i t i a l i z a t i o n p r o g r a m

E x t e r n a l o r s e r i a l i n p u t i n t e r r u p t s u b r o u t i n e

T i m e r / e v e n t c o u n t e r 0 i n t e r r u p t s u b r o u t i n e

P r o g r a m

R O M

1 6 b i t s

F F F F H

T i m e r / e v e n t c o u n t e r 1 i n t e r r u p t s u b r o u t i n e

000C H

T i m e r 2 i n t e r r u p t s u b r o u t i n e

T i m e r 3 i n t e r r u p t s u b r o u t i n e

010H

014H

D / A b u f f e r e m p t y i n t e r r u p t

018H

Program memory

Instruction Table Location

*15 *14 *13 *12 *11 *10 *9 *8 *7 *6 *5 *4 *3 *2 *1 *0

TABRDC [m] #7 #6 #5 #4 #3 #2 #1 #0 @7 @6 @5 @4 @3 @2 @1 @0

TABRDL [m] 11111111@7@6@5@4@3@2@1@0

Table location

Note: @7~@0: TBLP register bit7~bit0 *15~*0: Program ROM table address bit15~bit0

#7~#0: TBHP register bit7~bit0