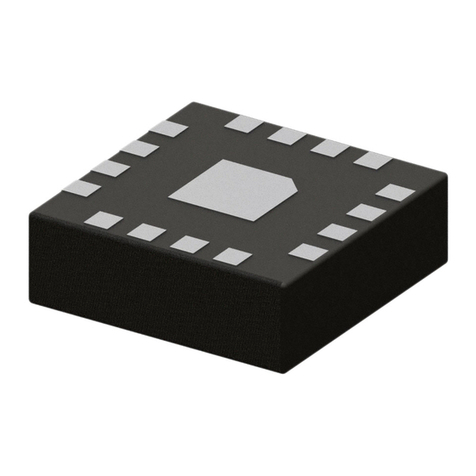

82V3911 WAN PLL

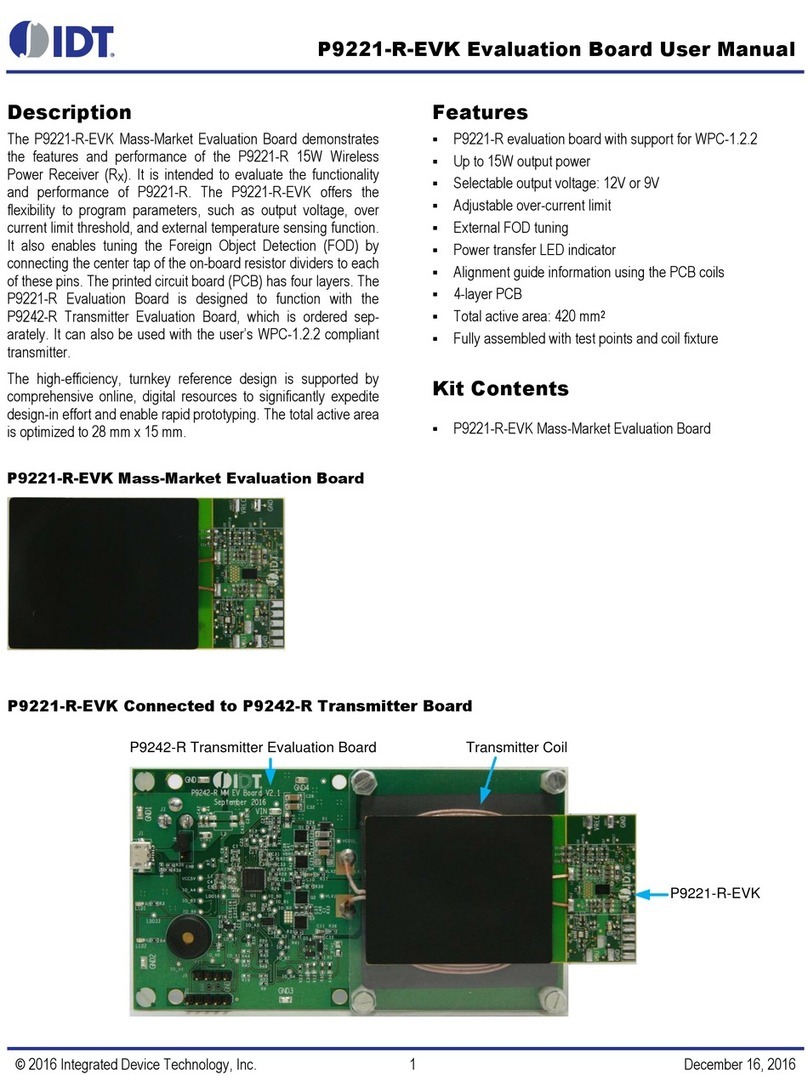

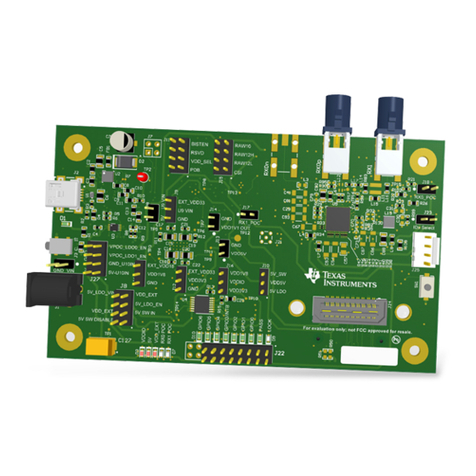

EVALUATION BOARD USER’S GUIDE 2REVISION 1 1/30/15

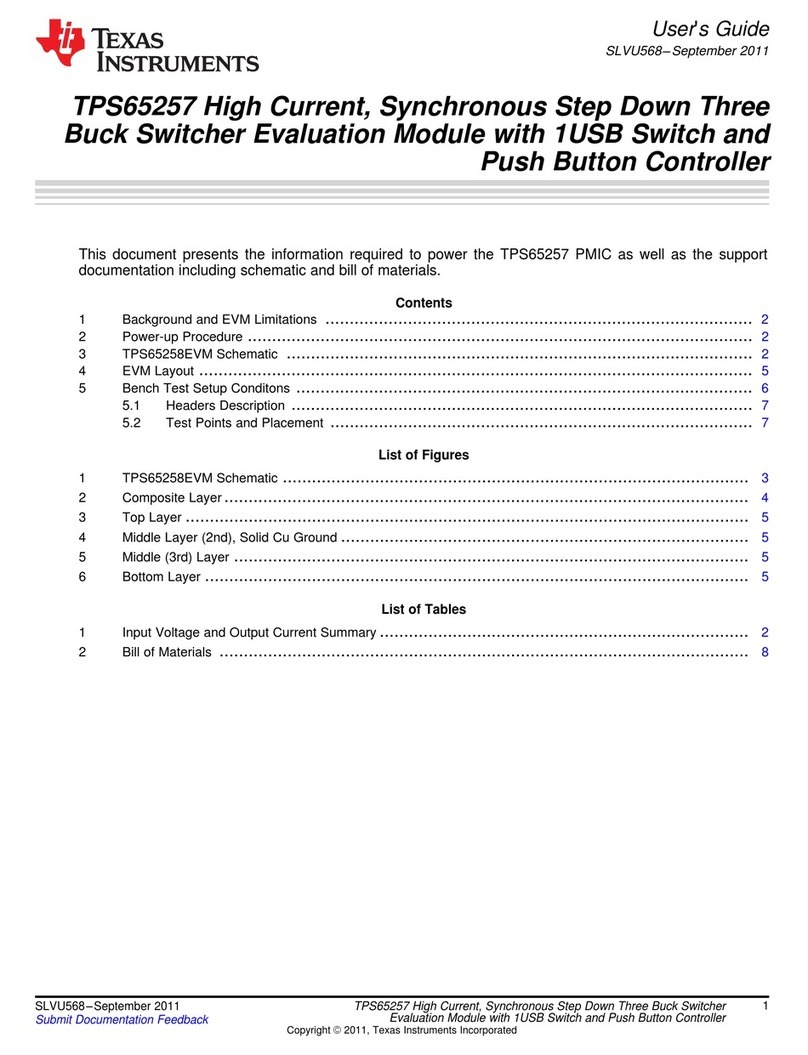

INTRODUCTION...................................................................................................................................................................... 1

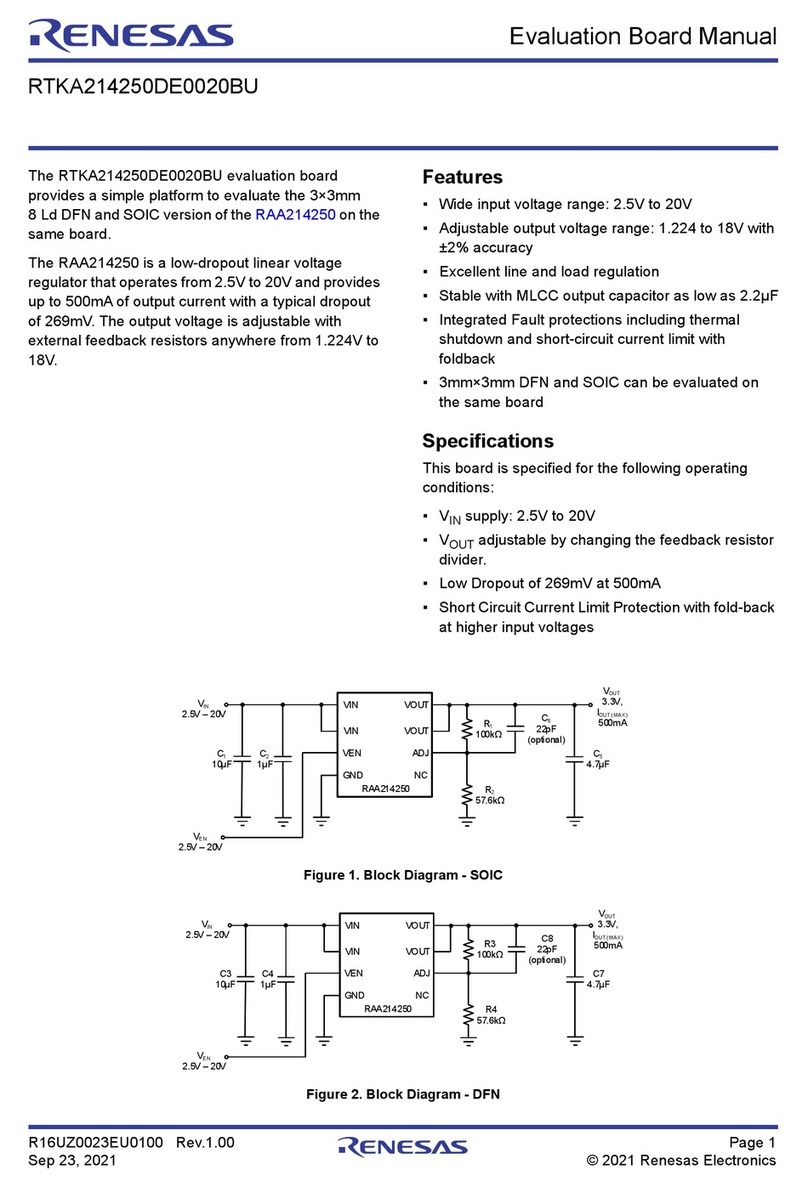

FEATURES.............................................................................................................................................................................. 1

PC REQUIREMENTS............................................................................................................................................................... 1

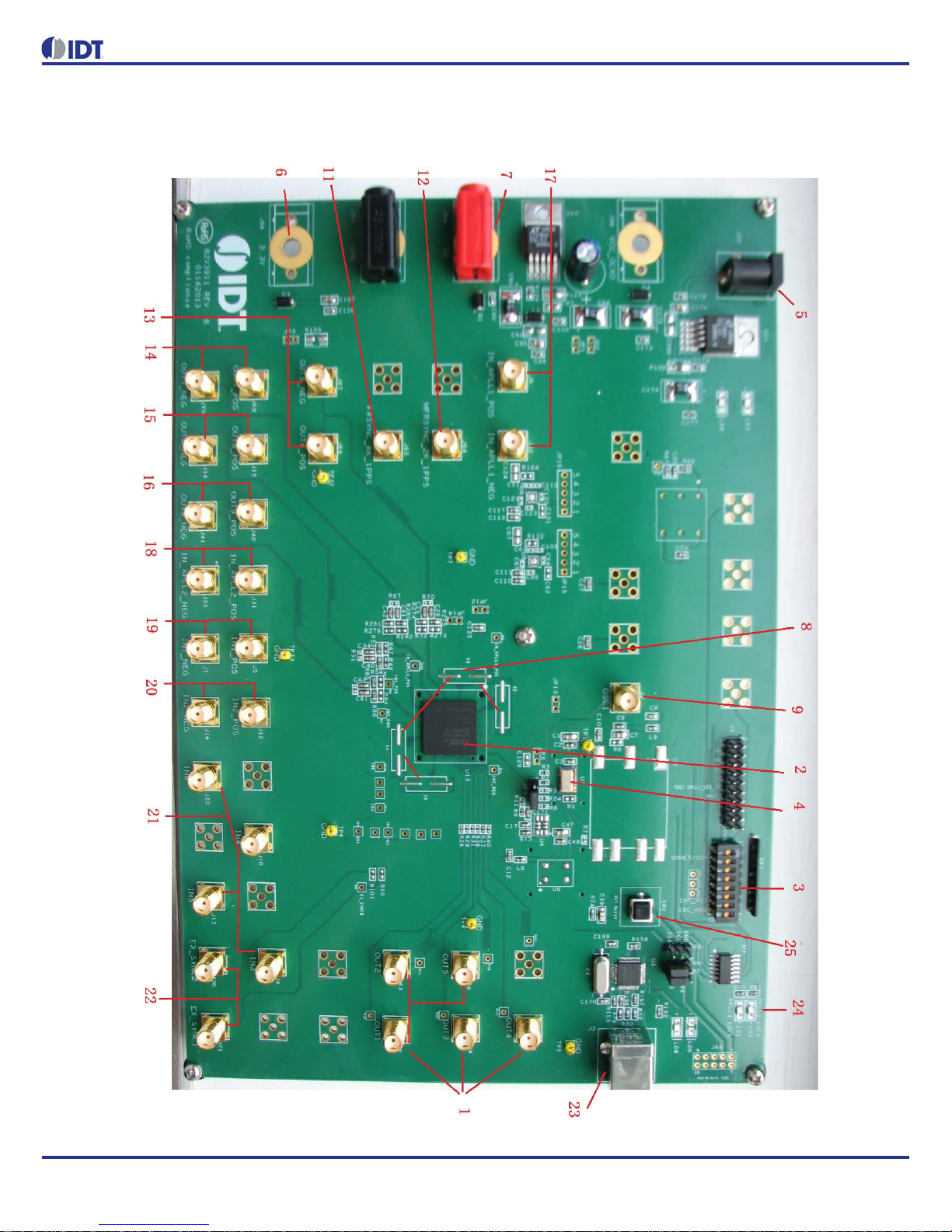

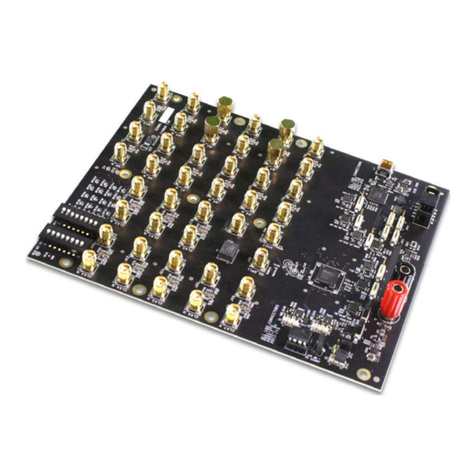

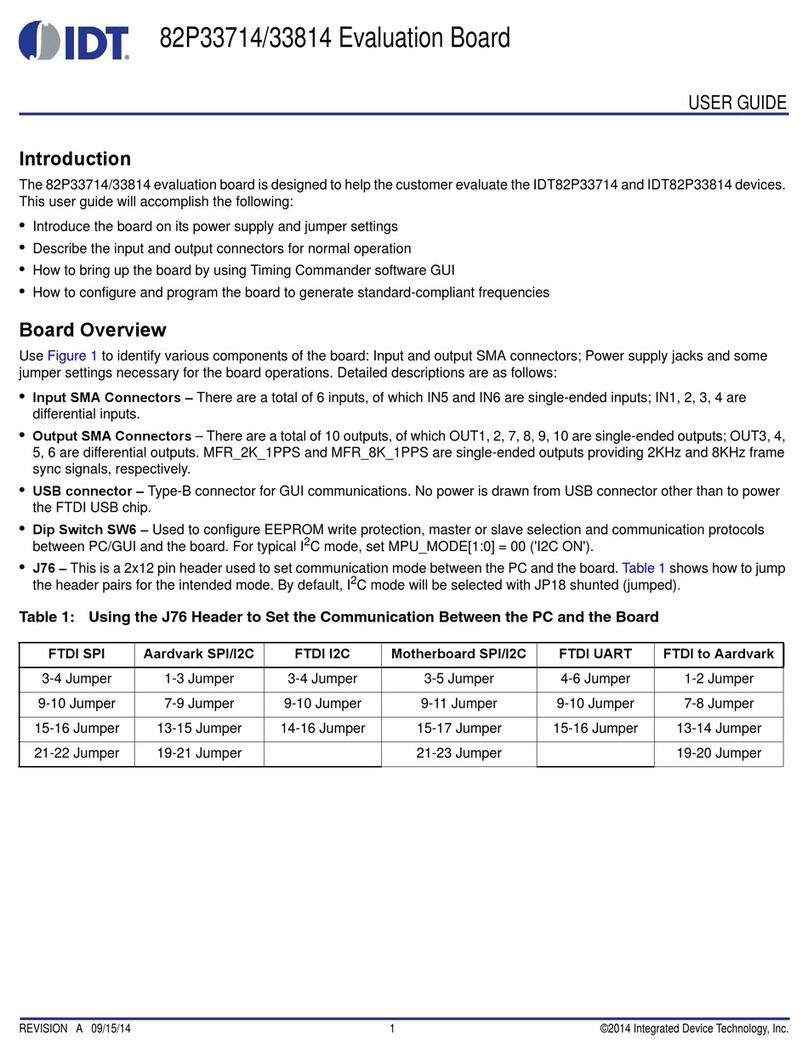

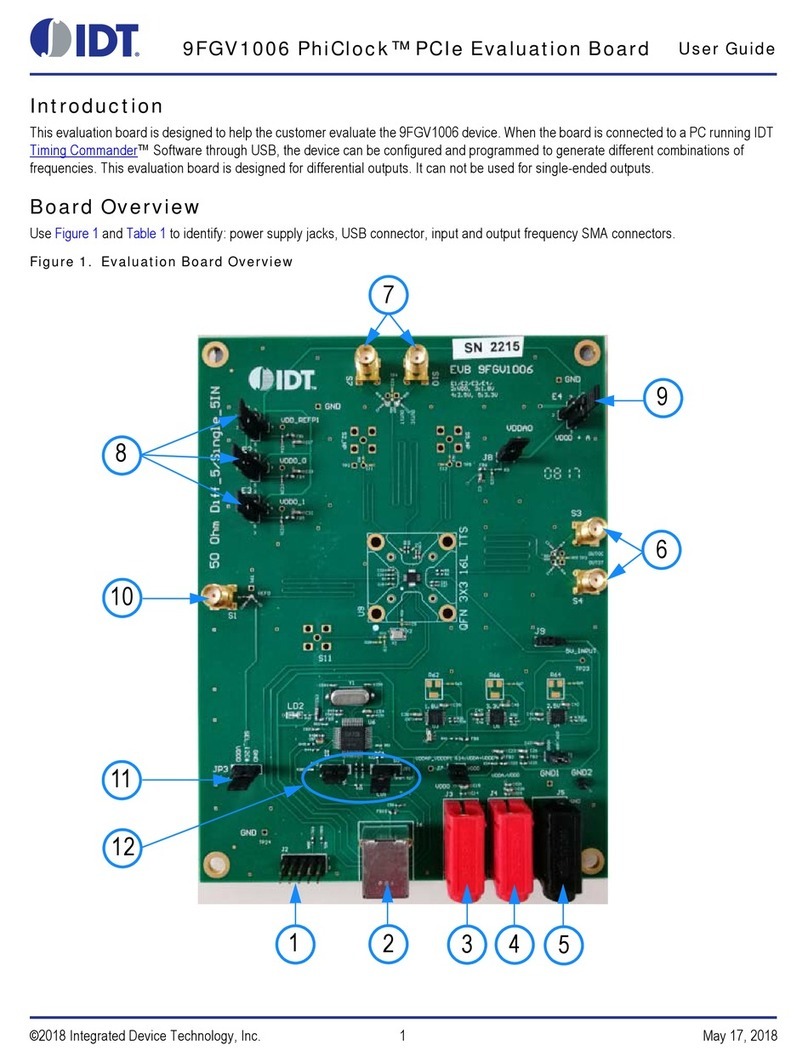

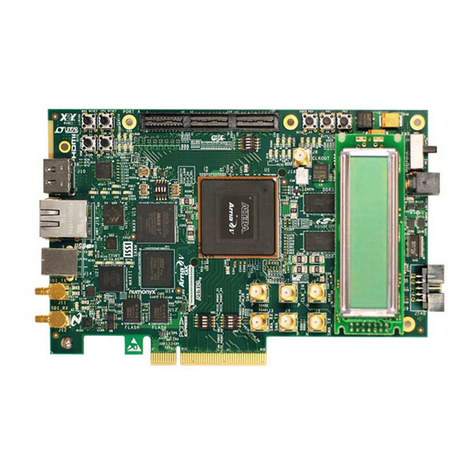

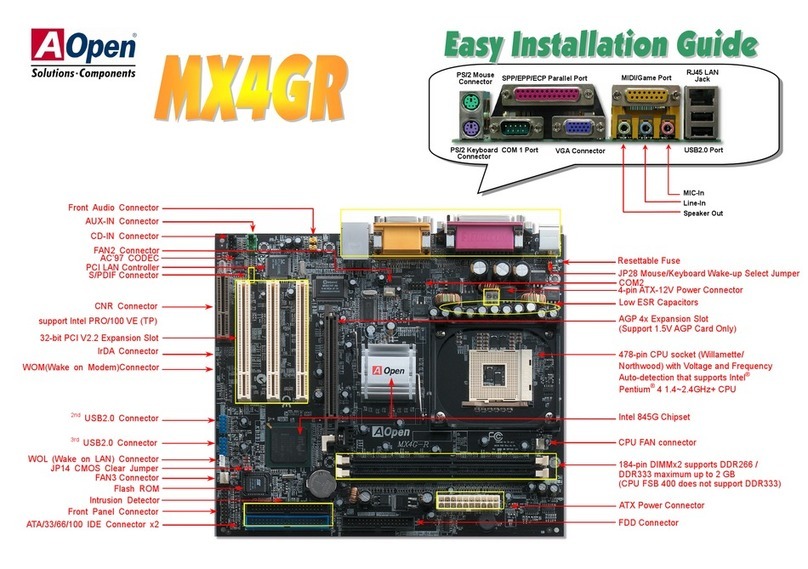

1 HARDWARE CONFIGURATION ....................................................................................................................................3

1.1 ANNOTATION FOR FIGURE-1 ..........................................................................................................................4

2 SOFTWARE CONFIGURATION .....................................................................................................................................5

2.1 INSTALLATION ..................................................................................................................................................5

2.2 GENERAL INTRODUCTION ..............................................................................................................................5

2.2.1 Overview.................................................................................................................................................5

2.2.2 Conventions used...................................................................................................................................5

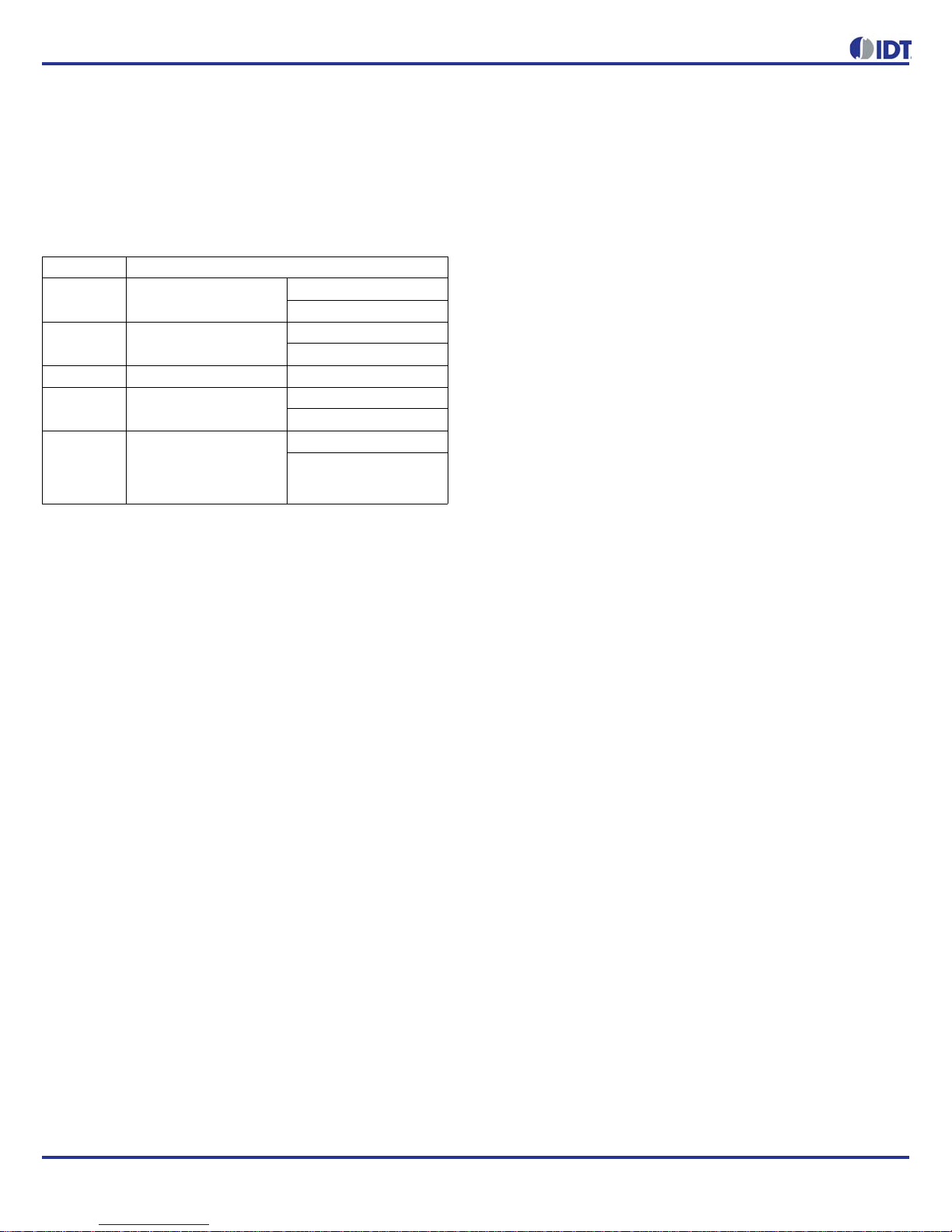

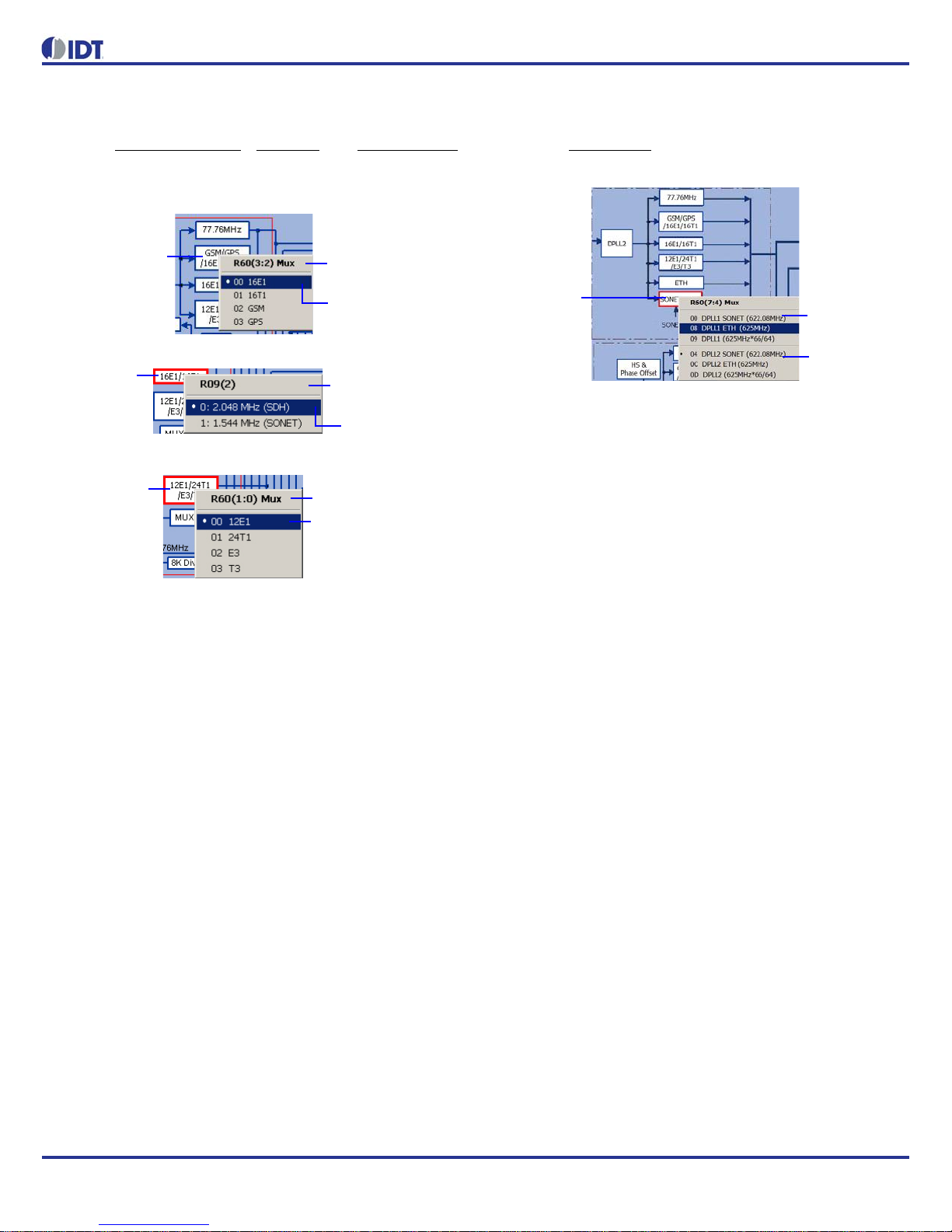

2.2.3 DPLL1/ DPLL2 Path Selection...............................................................................................................6

2.2.4 Read/Write the Configuration Data.........................................................................................................6

2.2.5 Load/Save the Configuration Data.........................................................................................................6

2.2.6 Tips for the Parameters and Buttons......................................................................................................7

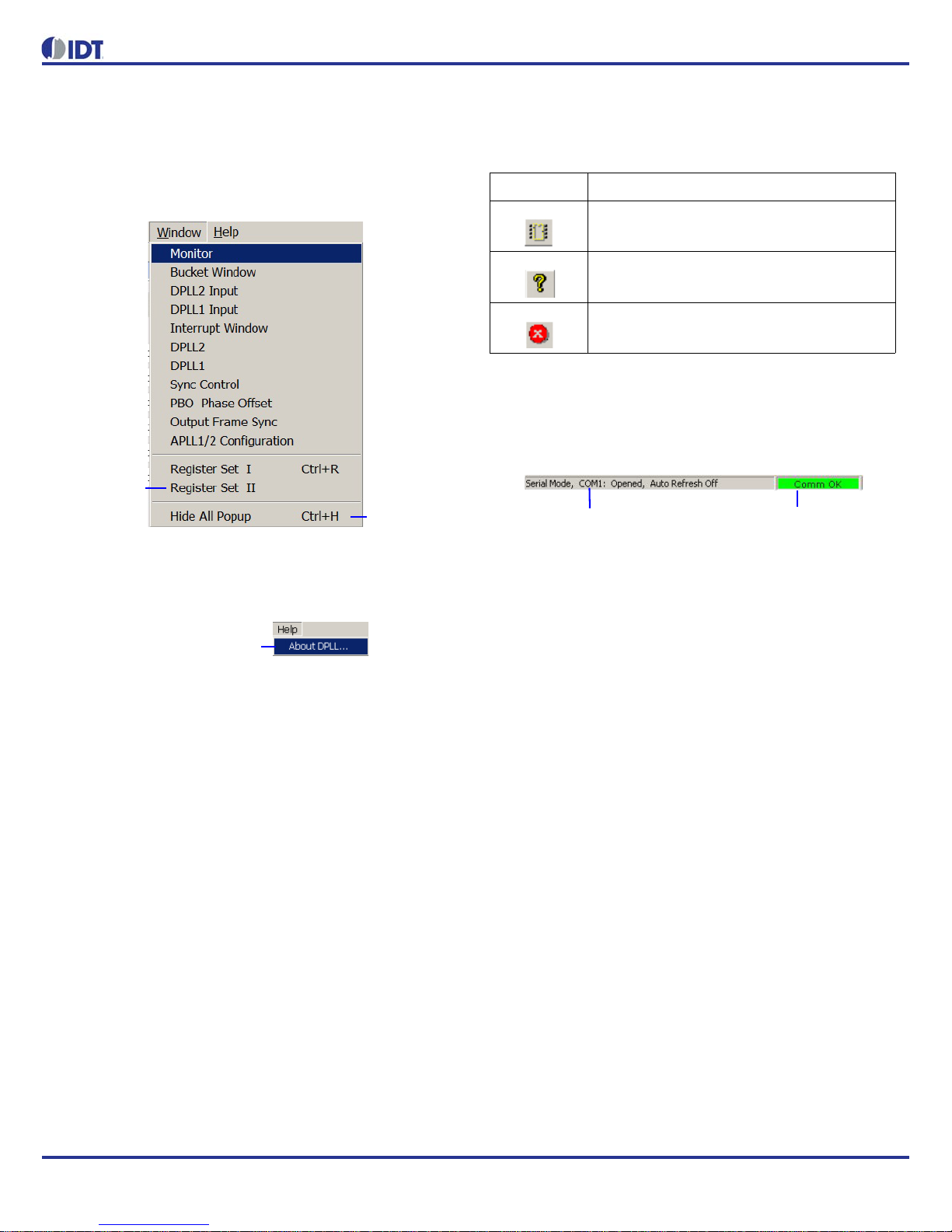

2.2.7 Menu Bar................................................................................................................................................7

2.2.8 Shortcut Icons.........................................................................................................................................8

2.2.9 Status Bar...............................................................................................................................................8

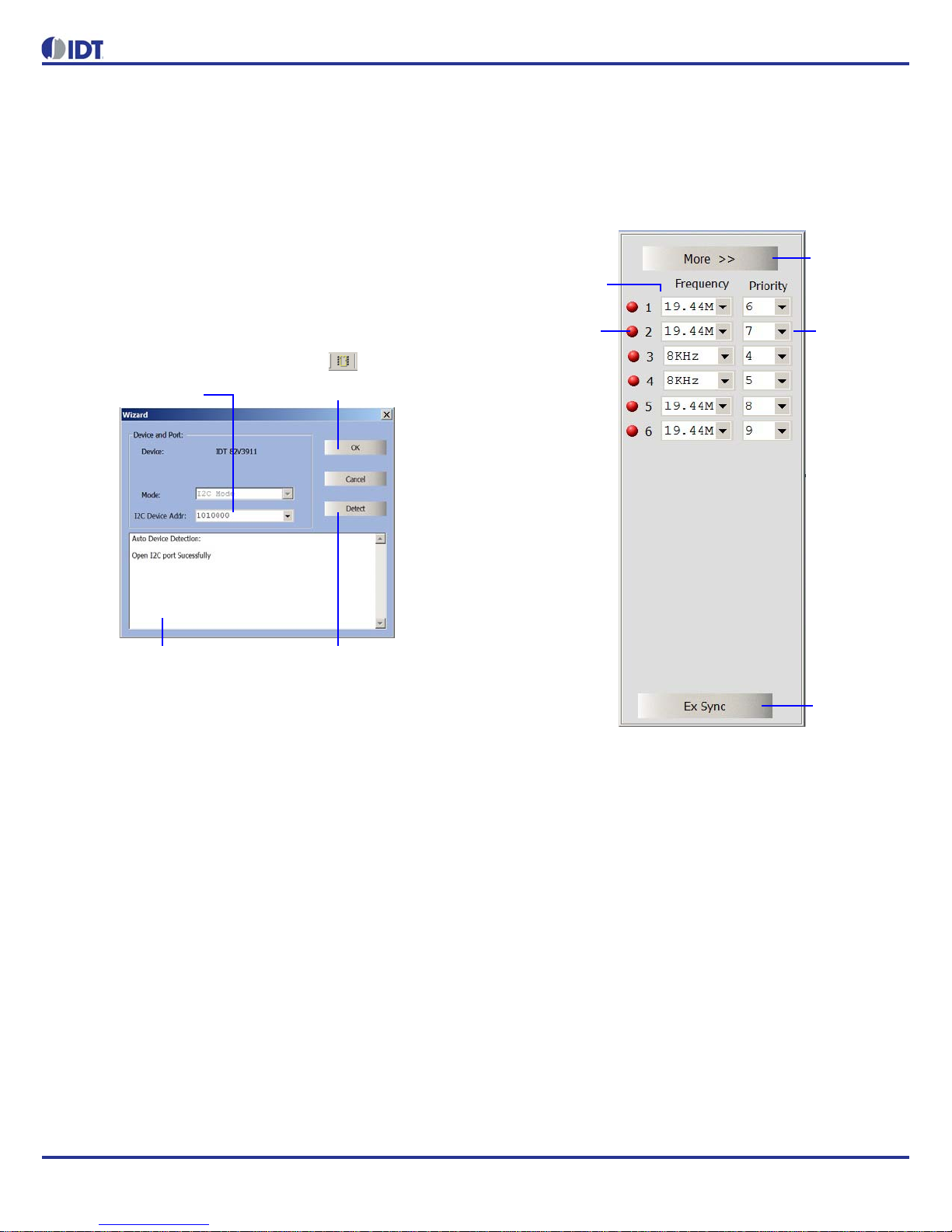

2.3 INITIALIZATION .................................................................................................................................................9

2.4 INPUT PORTS STATUS AND CONFIGURATION .............................................................................................9

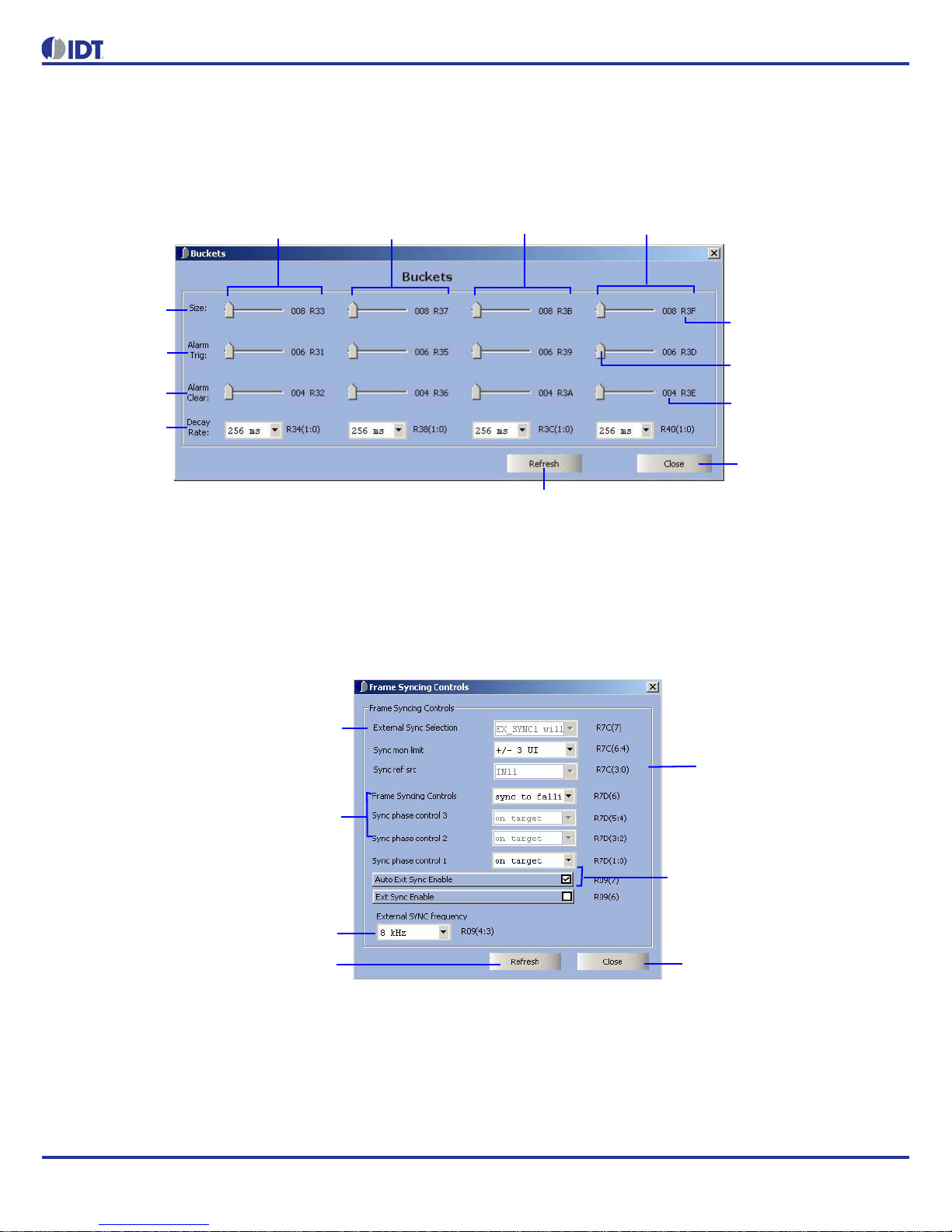

2.4.1 Leaky Bucket Configuration..................................................................................................................11

2.4.2 Frame Synchronization Control............................................................................................................11

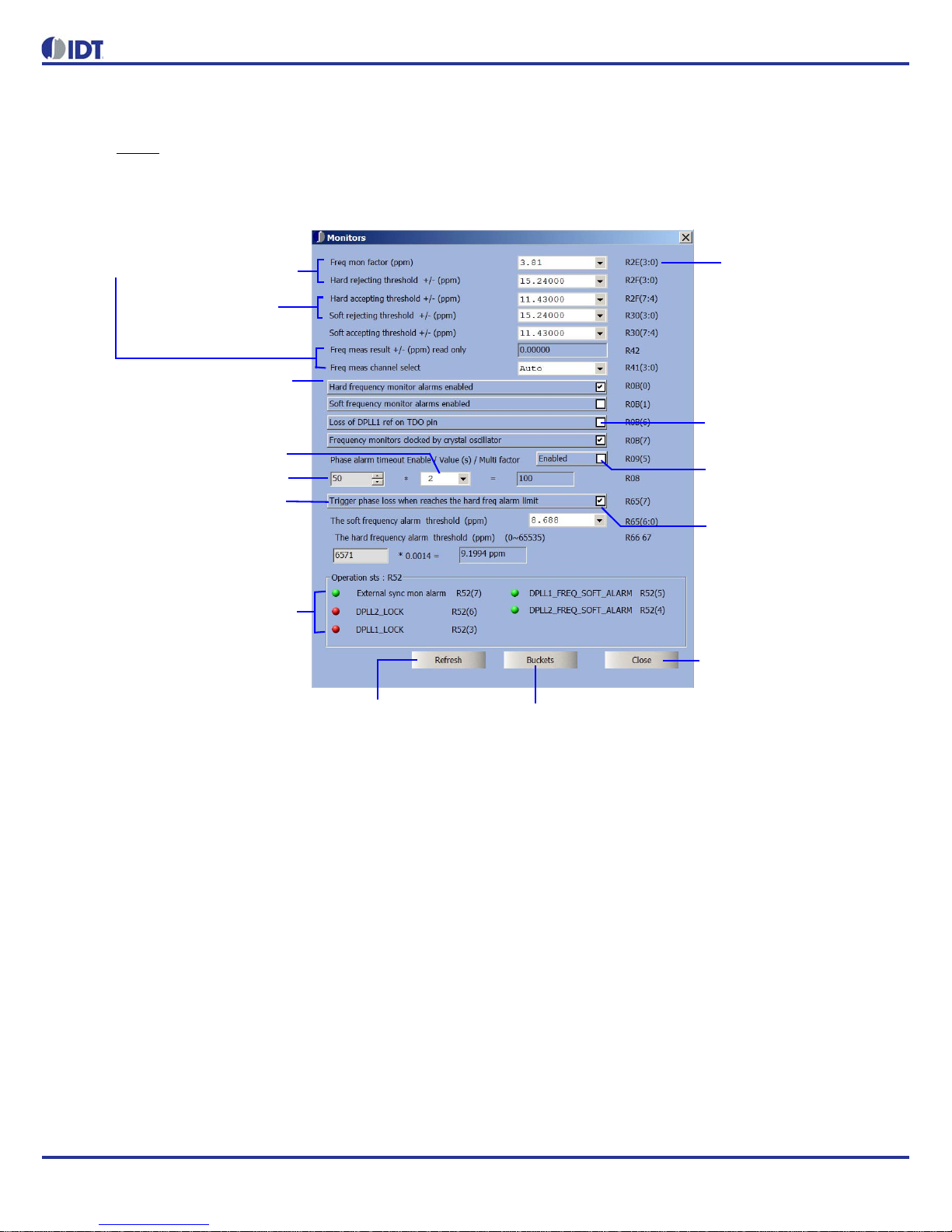

2.5 MONITOR CONFIGURATION ..........................................................................................................................12

2.6 DPLL2 PATH CONFIGURATION .....................................................................................................................13

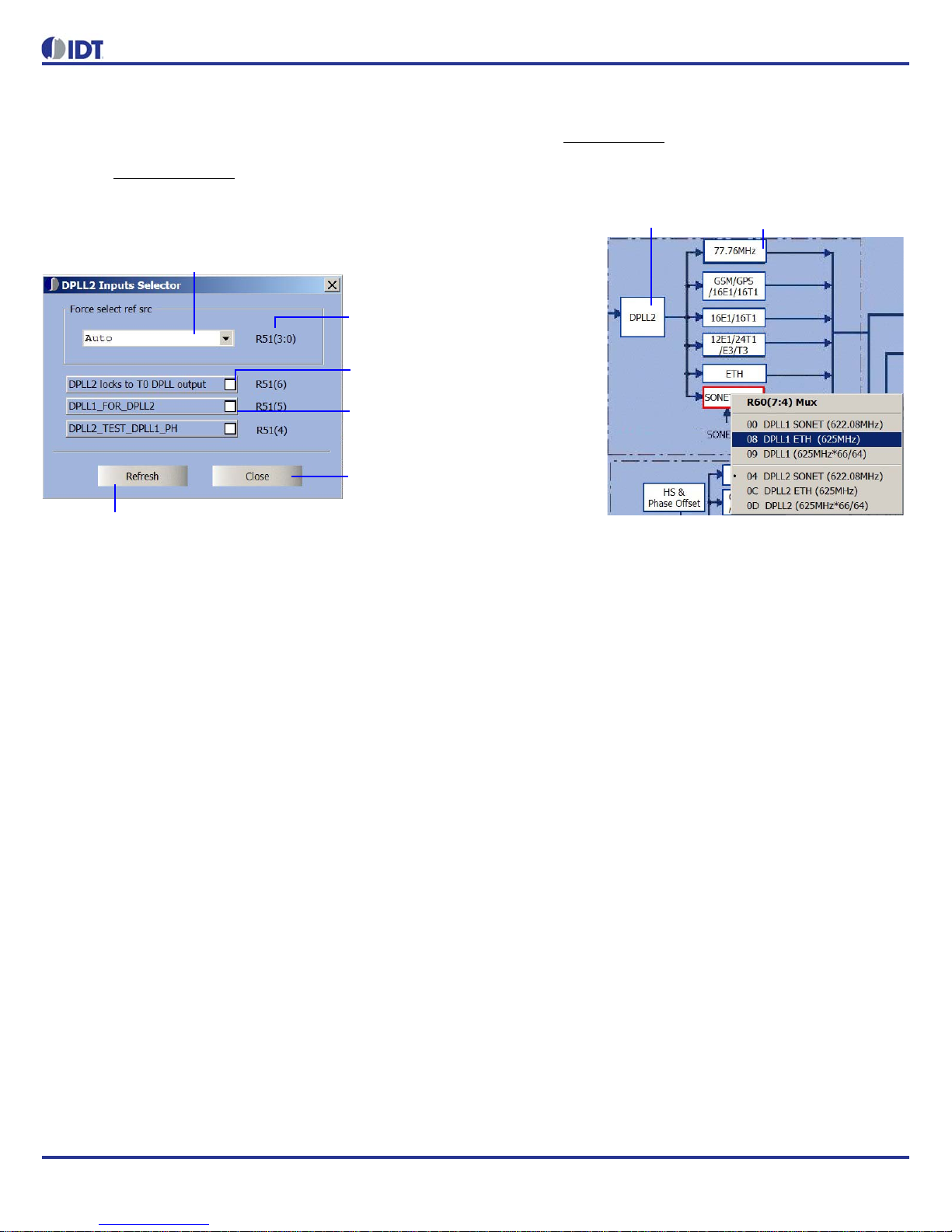

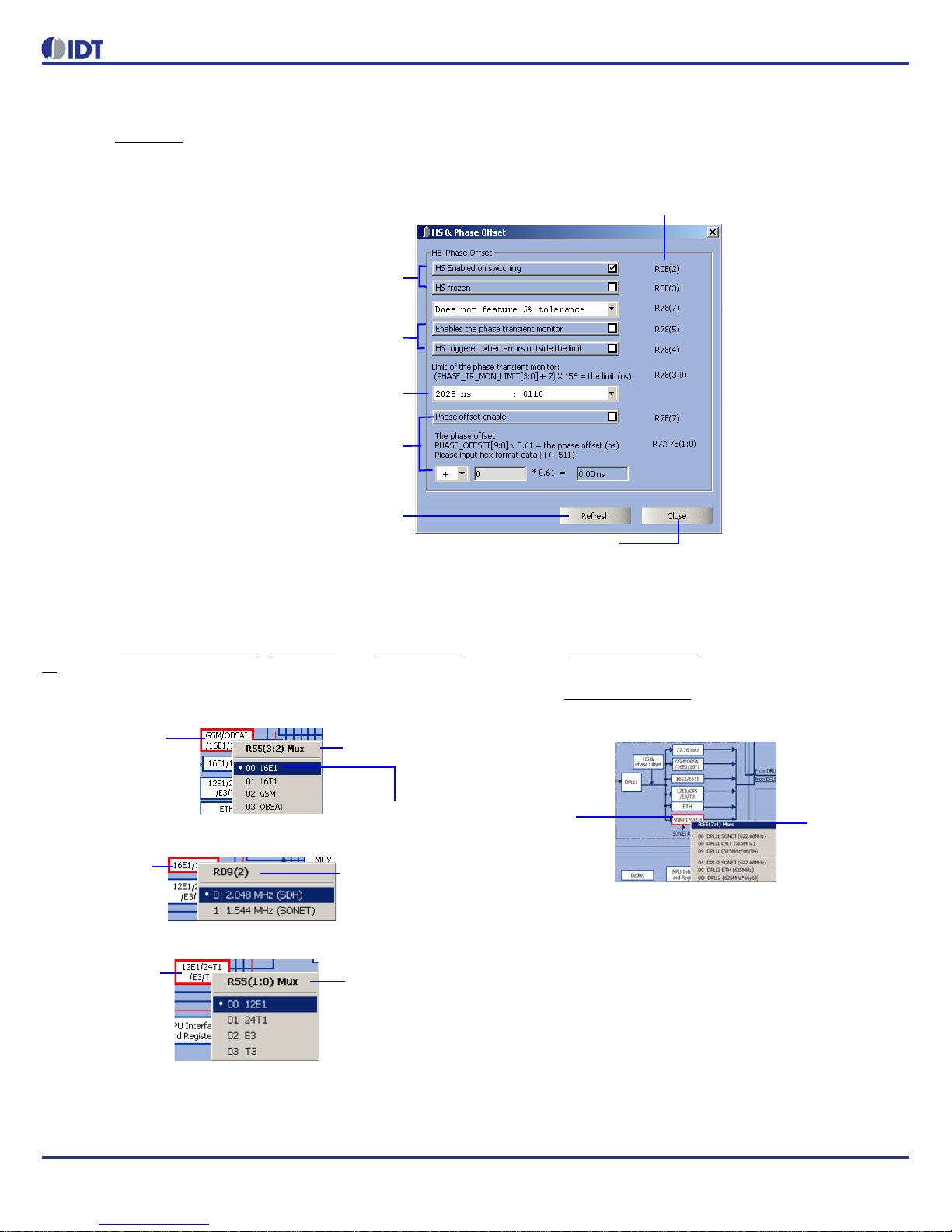

2.6.1 DPLL2 Input Selector...........................................................................................................................13

2.6.2 DPLL2 DPLL.........................................................................................................................................13

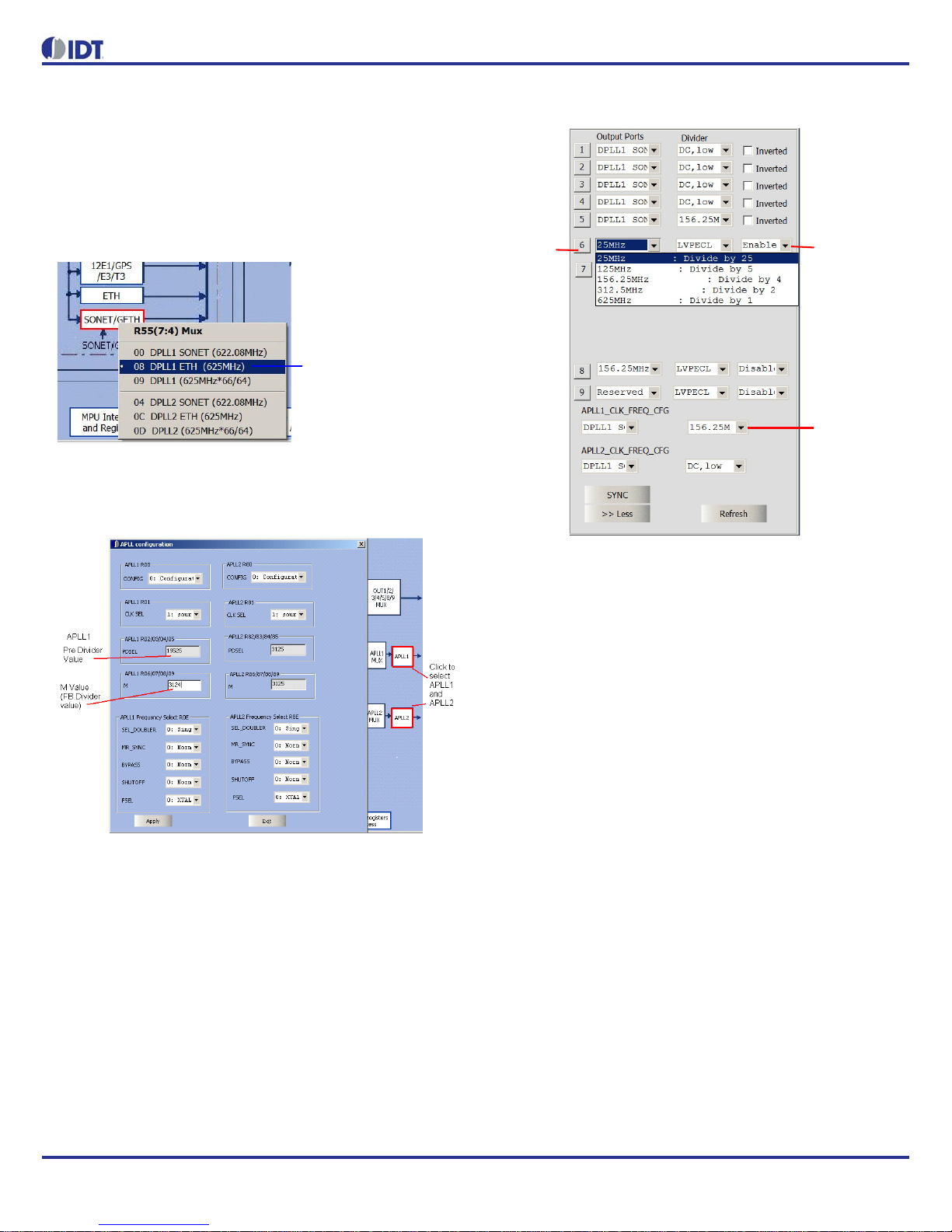

2.6.3 DPLL2 DCO Output Clock Frequency Selection..................................................................................14

2.6.4 DPLL2 SONET/GETH Configuration....................................................................................................14

2.7 DPLL1 PATH CONFIGURATION .....................................................................................................................15

2.7.1 DPLL1 Input Selector...........................................................................................................................15

2.7.2 DPLL1...................................................................................................................................................15

2.7.3 HS and Phase Offset Configuration.....................................................................................................16

2.7.4 DPLL1 DCO Output Clock Frequency Selection..................................................................................16

2.7.5 DPLL1 SONET/GETH Configuration....................................................................................................16

2.8 OUTPUT PORTS CONFIGURATION ..............................................................................................................17

2.8.1 Ethernet Clock Configuration for Output Ports.....................................................................................18

2.8.2 Frame and Multi-Frame Configuration..................................................................................................19

2.9 OTHER CONFIGURATION ..............................................................................................................................20

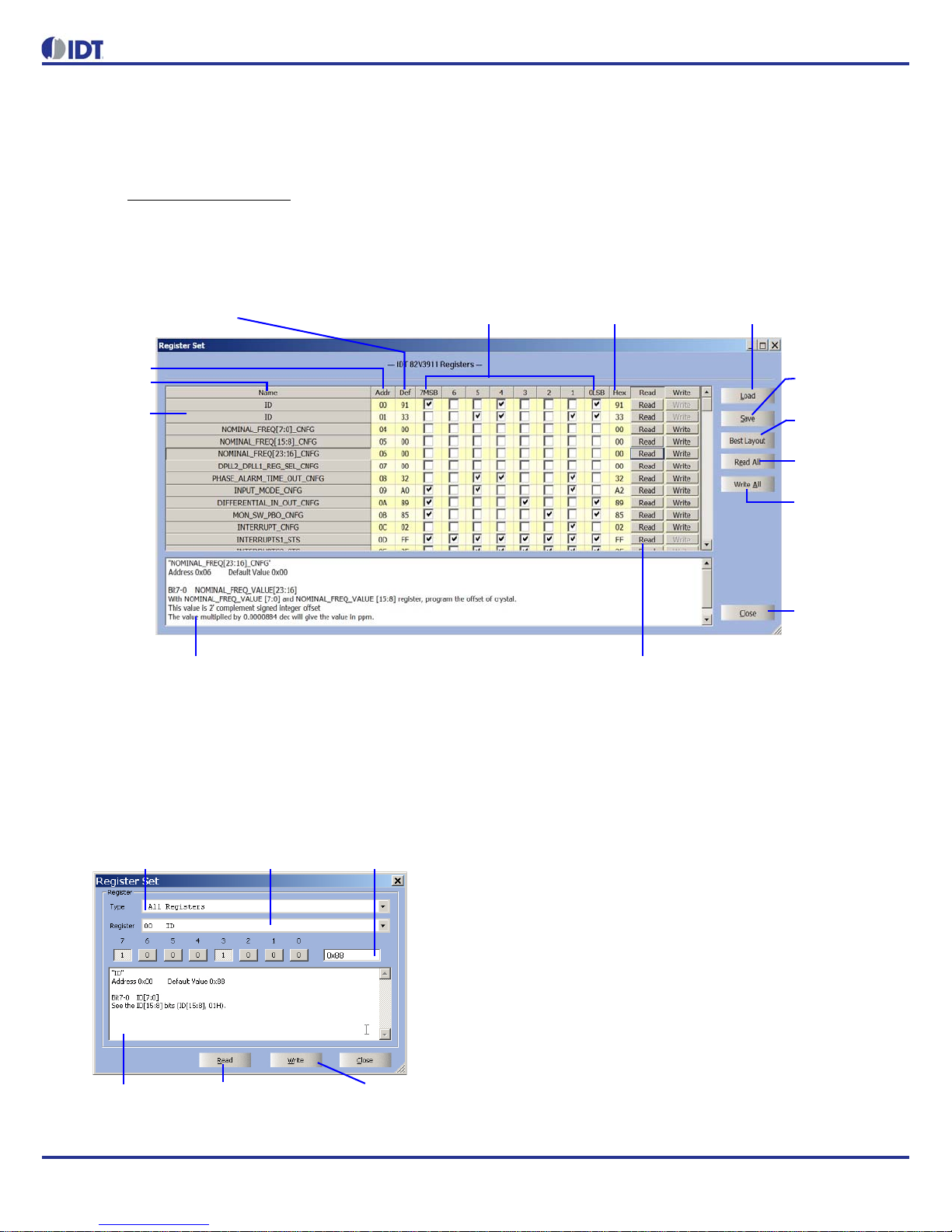

2.9.1 Registers Configuration........................................................................................................................20

2.9.2 Interrupts Configuration........................................................................................................................21

2.10 DPLL STATUS INDICATION ............................................................................................................................22

2.10.1 Current DPLL Status............................................................................................................................22

2.11 PAGE 1 REGISTERS CONFIGURATION ........................................................................................................24

3 APPENDIX: SCHEMATIC FILE ....................................................................................................................................25

TABLE OF CONTENTS