iv Intel®810A3 Chipset Design Guide

4.5 System Memory Layout Guidelines..............................................................4-5

4.5.1 System Memory Solution Space......................................................4-5

4.5.2 System Memory Routing Example...................................................4-6

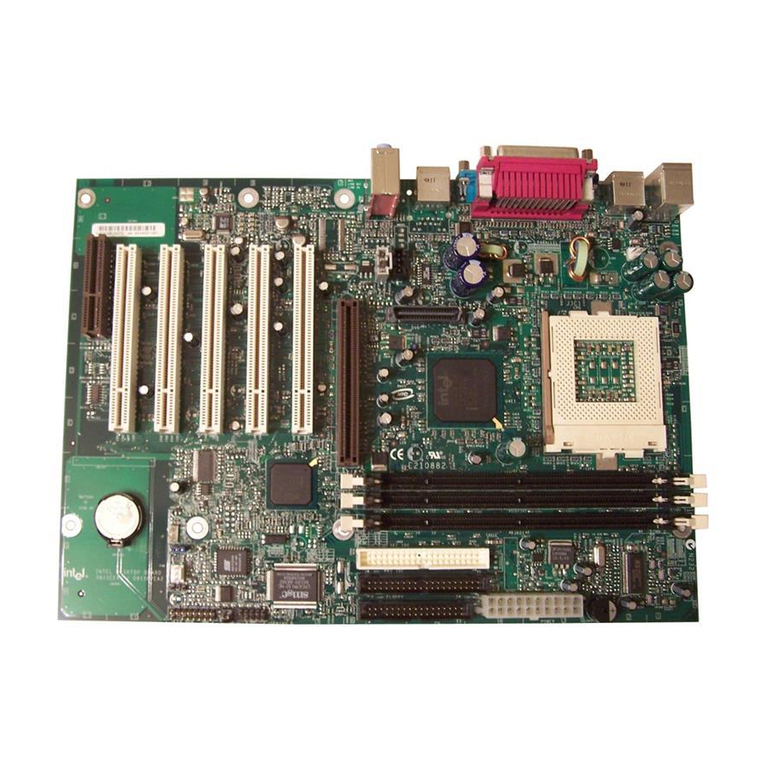

4.5.3 System Memory Connectivity ..........................................................4-7

4.6 Display Cache Interface................................................................................4-7

4.6.1 Display Cache Solution Space ........................................................4-8

4.7 Hub Interface................................................................................................4-9

4.7.1 Data Signals ..................................................................................4-10

4.7.2 Strobe Signals ...............................................................................4-10

4.7.3 HREF Generation/Distribution .......................................................4-10

4.7.4 Compensation................................................................................4-11

4.8 Ultra ATA/66 ...............................................................................................4-12

4.8.1 IDE Routing Guidelines .................................................................4-12

4.8.2 Ultra ATA/66 Detection..................................................................4-15

4.9 AC’97..........................................................................................................4-18

4.9.1 Audio/Modem Riser Card (AMR)...................................................4-18

4.9.2 AC’97 Routing................................................................................4-19

4.9.3 Motherboard Implementation.........................................................4-21

4.10 USB ............................................................................................................4-22

4.11 IOAPIC (I/O Advanced Programmable Interrupt Controller).......................4-23

4.12 PCI..............................................................................................................4-24

4.13 RTC ............................................................................................................4-24

4.13.1 RTC Crystal ...................................................................................4-24

4.13.2 External Capacitors .......................................................................4-25

4.13.3 RTC Layout Considerations...........................................................4-26

4.13.4 RTC External Battery Connection..................................................4-26

4.13.5 RTC External RTCRESET Circuit..................................................4-27

4.13.6 VBIAS DC Voltage and Noise Measurements..............................4-27

4.14 Processor PLL Filter Recommendation......................................................4-28

4.14.1 Processor PLL Filter Recommendation.........................................4-28

4.14.2 Topology........................................................................................4-28

4.14.3 Filter Specification .........................................................................4-28

4.14.4 Recommendation for Intel Platforms..............................................4-30

4.14.5 Custom Solutions...........................................................................4-31

4.15 RAMDAC/Display Interface ........................................................................4-32

4.15.1 Reference Resistor (Rset) Calculation...........................................4-33

4.15.2 RAMDAC Board Design Guidelines...............................................4-33

4.16 DPLL Filter Design Guidelines....................................................................4-35

4.16.1 Filter Specification .........................................................................4-36

4.16.2 Recommended Routing/Component Placement............................4-37

4.16.3 Example LC Filter Components.....................................................4-37

5 Advanced System Bus Design ..................................................................................5-1

5.1 AGTL+ Design Guidelines............................................................................5-1

5.1.1 Initial Timing Analysis ......................................................................5-2

5.1.2 Determine General Topology, Layout, and Routing Desired...........5-3

5.1.3 Pre-Layout Simulation .....................................................................5-3

5.1.4 Place and Route Board....................................................................5-5

5.1.5 Post-Layout Simulation....................................................................5-7

5.1.6 Validation.........................................................................................5-8

5.2 Theory.........................................................................................................5-10

5.2.1 AGTL+ ...........................................................................................5-10