Type1LD Application note HW

Page 3

TABLE OF CONTENTS

1Module introduction ................................................................................................................4

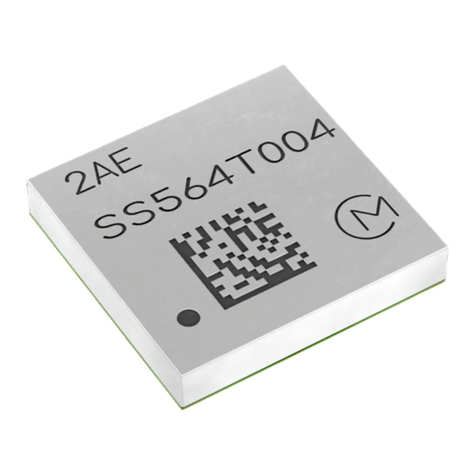

1.1 Type1LD Introduction.........................................................................................................4

1.2 Block Diagram.....................................................................................................................4

2Reference Circuit....................................................................................................................5

2.1 Reference Circuit.................................................................................................................5

3HW Design Guideline .............................................................................................................6

3.1 Underneath of module ........................................................................................................6

3.2 External 32.768KHz............................................................................................................7

3.3 Antenna................................................................................................................................7

4. RF Measurement Result.........................................................................................................9

4.1 Tx output power level (at module antenna port) ..............................................................9

4.1.1. WiFi...........................................................................................................................9

4.1.2. Bluetooth...................................................................................................................9

4.2 Rx minimum sensitivity level (at module antenna port) ...............................................10

4.2.1. WiFi.........................................................................................................................10

4.2.2. Bluetooth.................................................................................................................10

5. Current consumption ............................................................................................................11

5.1 WiFi ....................................................................................................................................11

5.1.1. Tx/Rx current consumption.....................................................................................11

5.1.2. Sleep current consumption.....................................................................................11

5.2 Bluetooth............................................................................................................................12

5.2.1. BLE current consumption .......................................................................................12

6. Throughput performance......................................................................................................13