Specification Number: SP-CJ1XK-L

P. 2/84

Murata Manufacturing Co., Ltd.

TABLE OF CONTENTS

1. Scope ..................................................................................................................................................... 4

2. Key Features.......................................................................................................................................... 4

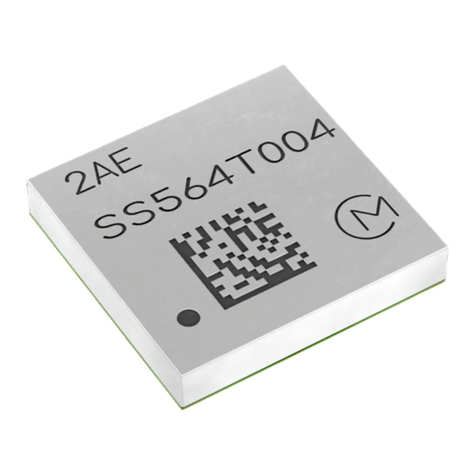

3. Ordering Information .............................................................................................................................. 4

4. Block Diagram........................................................................................................................................ 4

5. Certification Information ......................................................................................................................... 5

5.1. Radio Certification........................................................................................................................... 5

5.2. Bluetooth Qualification..................................................................................................................... 5

6. Dimensions, Marking and Terminal Configurations ............................................................................... 6

7. Module Pin Descriptions ........................................................................................................................ 7

7.1. Pin Assignments.............................................................................................................................. 7

7.2. Pin Descriptions............................................................................................................................... 8

7.3. Configuration Pins......................................................................................................................... 10

7.4. Pin States .......................................................................................................................................11

8. Absolute Maximum Ratings.................................................................................................................. 13

9. Operating Conditions............................................................................................................................ 13

9.1. Operating conditions...................................................................................................................... 13

9.2. External Sleep Clock Requirements.............................................................................................. 13

9.3. Digital I/O Requirements ............................................................................................................... 13

10. Power Sequence................................................................................................................................ 14

10.1. Power On Sequence ................................................................................................................... 14

10.2. Power Off Sequence ................................................................................................................... 14

11. Interface Timing.................................................................................................................................. 15

11.1. SDIO Timing................................................................................................................................. 15

11.1.1. Default Speed Mode ............................................................................................................. 15

11.1.2. High Speed Mode ................................................................................................................. 15

11.1.3. SDR12,SDR25,SDR50 Modes(up to 100 MHz)(1.8V)......................................................... 16

11.1.4. DDR50 Mode(50MHz)(1.8V)................................................................................................. 17

11.2. UART Timing (Default Mode)....................................................................................................... 19

11.3. Bluetooth PCM Timing................................................................................................................. 19

11.3.1. Master mode ......................................................................................................................... 19

11.3.2. Slave mode ........................................................................................................................... 20

12. DC / RF Characteristics ..................................................................................................................... 21

12.1. DC/RF Characteristics for IEEE802.11b - 2.4GHz...................................................................... 21

12.1.1. High Rate Condition for IEEE802.11b –2.4GHz.................................................................. 21

12.1.2. Low Rate Condition for IEEE802.11b –2.4GHz................................................................... 22

12.2. DC/RF Characteristics for IEEE802.11g - 2.4GHz...................................................................... 23

12.2.1. High Rate Condition for IEEE802.11g –2.4GHz.................................................................. 23

12.2.2. Low Rate Condition for IEEE802.11g –2.4GHz................................................................... 24

12.3. DC/RF Characteristics for IEEE802.11n - 2.4GHz...................................................................... 25

12.3.1. High Rate Condition for IEEE802.11n 20MHz BW –2.4GHz .............................................. 25

12.3.2. Low Rate Condition for IEEE802.11n 20MHz BW –2.4GHz............................................... 26

12.4. DC/RF Characteristics for IEEE802.11a - 5GHz......................................................................... 27

12.4.1. High Rate Condition for IEEE802.11a –5GHz..................................................................... 27

12.4.2. Low Rate Condition for IEEE802.11a –5GHz...................................................................... 28

12.5. DC/RF Characteristics for IEEE802.11n(HT20) - 5GHz ............................................................. 29

12.5.1. High Rate Condition for IEEE802.11n(HT20) –5GHz.......................................................... 29

12.5.2. Low Rate Condition for IEEE802.11n(HT20) –5GHz .......................................................... 30

12.6. DC/RF Characteristics for IEEE802.11n(HT 40MHz) - 5GHz..................................................... 31

12.6.1. High Rate Condition for IEEE802.11n(HT40) –5GHz.......................................................... 31

12.6.2. Low Rate Condition for IEEE802.11n(HT40) –5GHz .......................................................... 32

12.7. DC/RF Characteristics for Bluetooth........................................................................................... 33

12.7.1. Basic Data Rate Condition.................................................................................................... 33

12.7.2. Enhanced Data Rate Condition............................................................................................ 34

12.8. DC/RF Characteristics for Bluetooth Low Energy....................................................................... 35

12.8.1. 1Mbps PHY Condition........................................................................................................... 35

12.8.2. 2Mbps PHY Condition........................................................................................................... 36

13. Land Patterns..................................................................................................................................... 37