© PHYTEC America L.L.C. 2023 6

1.1 List of Figures

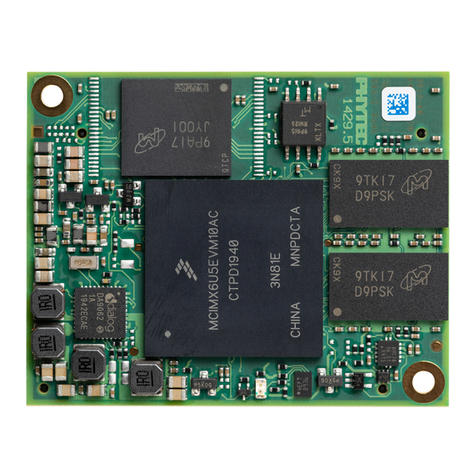

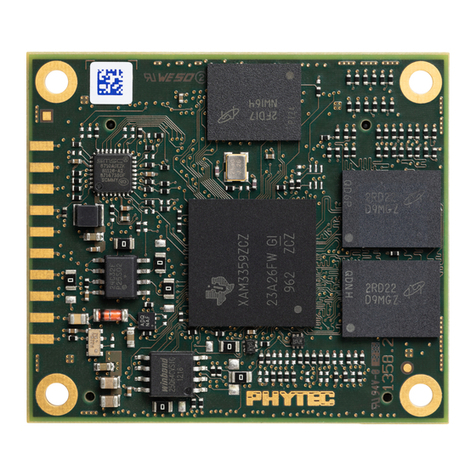

Figure 1. phyCORE-AM62Ax DSC SOM.................................................................................................. 13

Figure 2. phyCORE-AM62Ax DSC Block Diagram .................................................................................. 14

Figure 3. phyCORE-AM62Ax DSC Dimensions Top View....................................................................... 15

Figure 4. phyCORE-AM62Ax DSC Dimensions End View....................................................................... 16

Figure 5. phyCORE-AM62Ax DSC Component Placement (processor side).......................................... 17

Figure 6. phyCORE-AM62Ax DSC Component Placement (connector side)........................................... 18

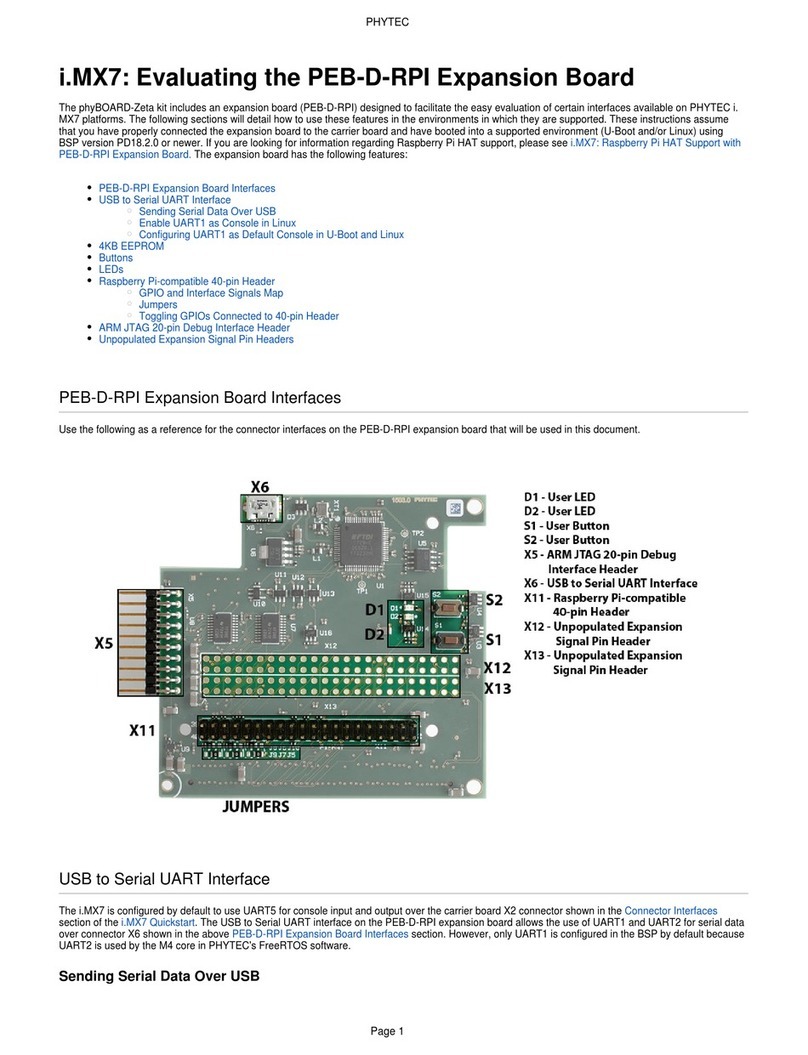

Figure 7. Position Solder Jumper Pad Numbering Scheme .................................................................... 20

Figure 8. Jumper Locations (Connector side)......................................................................................... 22

Figure 9. Landing Pattern Pinning Detail................................................................................................ 23

Figure 10. Landing Pattern (SOM Edge Dimensions) ............................................................................. 24

Figure 11. Landing Pattern Detail (SOM Corner Dimensions) ................................................................ 25

Figure 12. Landing Pattern Dimensions (Pin Alignment) ....................................................................... 26

Figure 13. Pinout example using X_VOUT0_VSYNC in our schematic................................................... 27

Figure 14. Fan design reference circuit................................................................................................... 34

Figure 15. Primary Power VIN(VCC_5V0_MAIN) reference circuit........................................................... 37

Figure 16. SOM current reader reference circuit ..................................................................................... 37

Figure 17. Phoenix connector power input with overload protection reference circuit.......................... 38

Figure 18. Reset signals pullups, pulldowns, and capacitors populated on the SOM ............................ 39

Figure 19. Carrier board power reference circuit..................................................................................... 41

Figure 20. OSPI0 CSN signal use............................................................................................................. 43

Figure 21. MMC1 SD-card Reader Reference Schematic......................................................................... 47

Figure 22. MMC1 Load Switch Reference Schematic .............................................................................. 48

Figure 23. M.2 WIFI MMC2 Connector Reference Schematic................................................................... 48

Figure 24. M.2 WIFI MMC2 Level Translators Reference Schematic ....................................................... 49

Figure 25. BOOTMODE pullups/pulldowns.............................................................................................. 50

Figure 26. Reference Schematic for BOOTMODE configuration............................................................. 52

Figure 27. MCAN0 Reference Schematic................................................................................................. 53

Figure 28. RJ45 Reference Schematic..................................................................................................... 58

Figure 29. RGMII PHY RJ45 Reference Schematic .................................................................................. 58

Figure 30. RGMII PHY Strapping Resistors Reference Schematic .......................................................... 59

Figure 31. RGMII PHY Reference Schematic ........................................................................................... 59

Figure 32. USB-HUB Reference Schematic.............................................................................................. 66

Figure 33. USB 2.0 Connector Reference Schematic .............................................................................. 66

Figure 34. USB-C Connector Reference Schematic................................................................................. 67

Figure 35. CSI Power Toggle Reference Schematic ................................................................................ 73