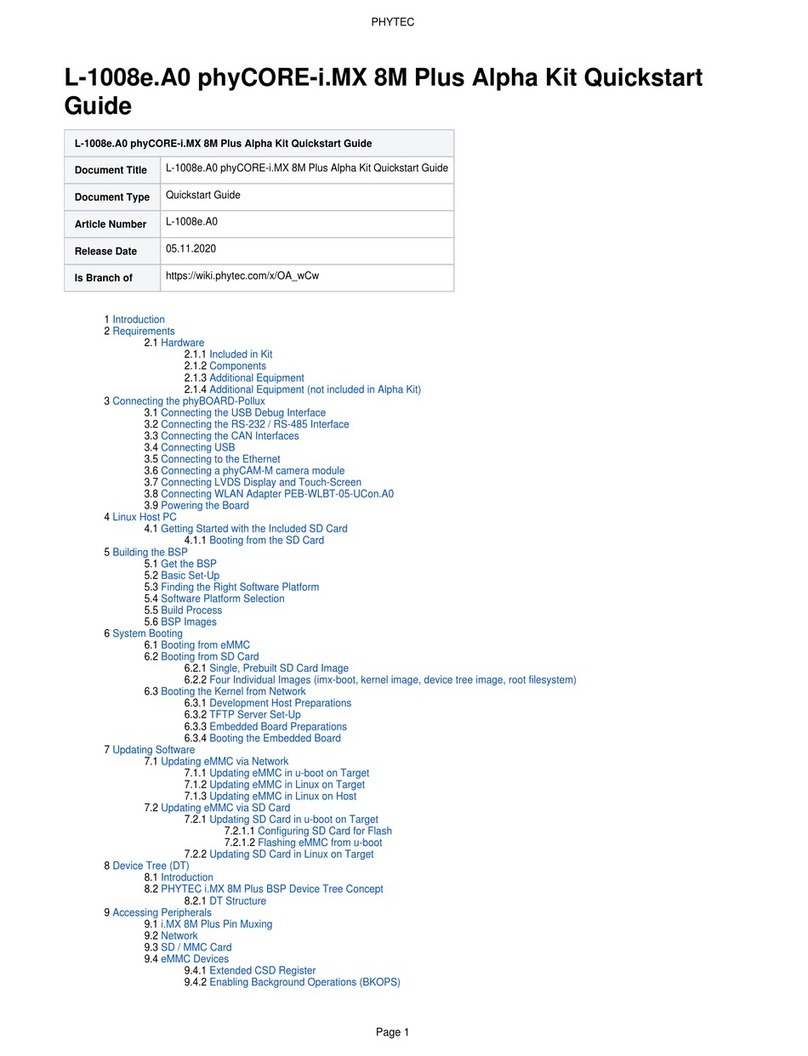

Contents

©PHYTEC Messtechnik GmbH 2006 L-484e_1

Preface...........................................................................................................1

1Introduction.........................................................................................3

1.1 Block Diagram .............................................................................6

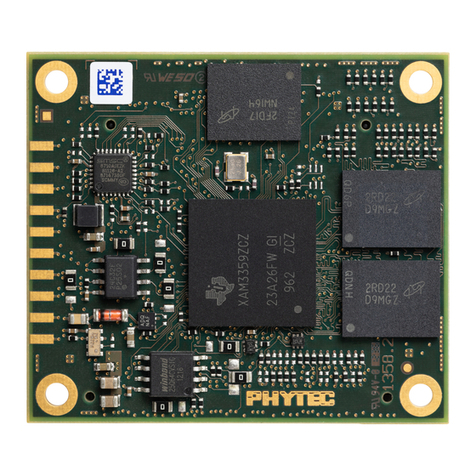

1.2 View of the phyCORE-MPC5554................................................7

1.3 Minimum Requirements to Operate the phyCORE-MPC5554 ...9

2Pin Description..................................................................................11

3Jumpers..............................................................................................25

4Power Requirements.........................................................................35

4.1 Voltage Supervision and Reset ..................................................36

5System Start-Up Configuration.......................................................37

6System Memory.................................................................................39

6.1 External Standard Flash Memory (U3, U4)...............................40

6.2 Synchronous Burst SRAM (U5 – U8) .......................................41

6.3 Serial Memory (U15).................................................................42

7FPGA System Logic Device U21......................................................45

7.1 FPGA Firmware Development...................................................47

8Serial Interfaces.................................................................................49

8.1 RS-232 Interface ........................................................................49

8.2 CAN Interface ............................................................................50

8.3 JTAG/OnCE/Nexus Debug Interface.........................................51

9LAN91C111 Ethernet Controller....................................................53

9.1 Addressing the Ethernet Controller............................................53

9.2 Interrupt......................................................................................53

9.3 MAC Address.............................................................................54

9.4 Ethernet EEPROM U18.............................................................54

9.5 10/100Base-T Interface..............................................................54

10 Real-Time Clock RTC-8564 (U16)..................................................55

11 phyCORE Development Board PCM-979......................................57

11.1 Concept of the phyCORE Development Board PCM-979 ........57

11.2 Development Board PCM-979 Overview..................................58

11.2.1 Connectors, Buttons, LED’s .........................................58

11.2.2 Jumpers on the phyCORE Development Board PCM-

979.................................................................................61

11.3 Functional Components on the phyCORE Development Board

PCM-979....................................................................................65

11.3.1 Power Supply at X5 ......................................................65

11.3.2 First Serial Interface at Socket P2A..............................67

11.3.3 Second Serial Interface at Socket P2B..........................67

11.3.4 First CAN Interface at Plug P1A ..................................68

11.3.5 Second CAN Interface at Plug P1B..............................70

11.3.6 Programmable LED D6.................................................72