SH69P55A/K55A

7

Functional Descriptions

1. CPU

The CPU contains the following functional blocks: Program

Counter (PC), Arithmetic Logic Unit (ALU), Carry Flag (CY),

Accumulator, Table Branch Register, Data Pointer (INX,

DPH, DPM, and DPL) and Stacks.

1.1. PC

The PC is used for ROM addressing consisting of 12-bit:

Page Register (PC11), and Ripple Carry Counter (PC10,

PC9, PC8, PC7, PC6, PC5, PC4, PC3, PC2, PC1, PC0).

The program counter is loaded with data corresponding to

each instruction. The unconditional jump instruction (JMP)

can be set at 1-bit page register for higher than 2K.

The program counter can address only 4K program ROM

address. (Refer to the ROM description).

1.2. ALU and CY

The ALU performs arithmetic and logic operations. The ALU

provides the following functions:

Binary addition/subtraction (ADC, ADCM, ADD, ADDM,

SBC, SBCM, SUB, SUBM, ADI, ADIM, SBI, SBIM)

Decimal adjustments for addition/subtraction (DAA, DAS)

Logic operations (AND, ANDM, EOR, EORM, OR, ORM,

ANDIM, EORIM, ORIM)

Decisions (BA0, BA1, BA2, BA3, BAZ, BNZ, BC, BNC)

Logic Shift (SHR)

The Carry Flag (CY) holds the ALU overflow that the

arithmetic operation generates. During an interrupt service

or call instruction, the carry flag is pushed into the stack and

recovered from the stack by the RTNI instruction. It is

unaffected by the RTNW instruction.

1.3. Accumulator (AC)

The accumulator is a 4-bit register holding the results of the

arithmetic logic unit. In conjunction with the ALU, data is

transferred between the accumulator and system register,

or data memory can be performed.

1.4. Table Branch Register (TBR)

Table Data can be stored in program memory and can be

referenced by using Table Branch (TJMP) and Return

Constant (RTNW) instructions. The TBR and AC are placed

by an offset address in program ROM. TJMP instruction

branch into address ((PC11 - PC8) X (28) + (TBR, AC)). The

address is determined by RTNW to return look-up value

into (TBR, AC). ROM code bit7-bit4 is placed into TBR and

bit3-bit0 into AC.

1.5. Data Pointer

The Data Pointer can indirectly address data memory.

Pointer address is located in register DPH (3-bits), DPM

(3-bits) and DPL (4-bits). The addressing range is

000H--3FFH. Pseudo index address (INX) is used to read

or write Data memory, then RAM address bit9 - bit0 which

comes from DPH, DPM and DPL.

1.6. Stack

The stack is a group of registers used to save the contents

of CY & PC (11-0) sequentially with each subroutine call or

interrupt. The MSB is saved for CY and it is organized into

13 bits X 8 levels. The stack is operated on a first-in,

last-out basis and returned sequentially to the PC by the

return instructions (RTNI/RTNW).

Note:

The stack nesting includes both subroutine calls and

interrupts requests. The maximum allowed for subroutine

calls and interrupts are 8 levels. If the number of calls and

interrupt requests exceeds 8, then the bottom of stack will

be shifted out, that program execution may enter an

abnormal state.

2. RAM

Built-in RAM contains general-purpose data memory and system register. Because of its static nature, the RAM can keep

data after the CPU entering STOP or HALT.

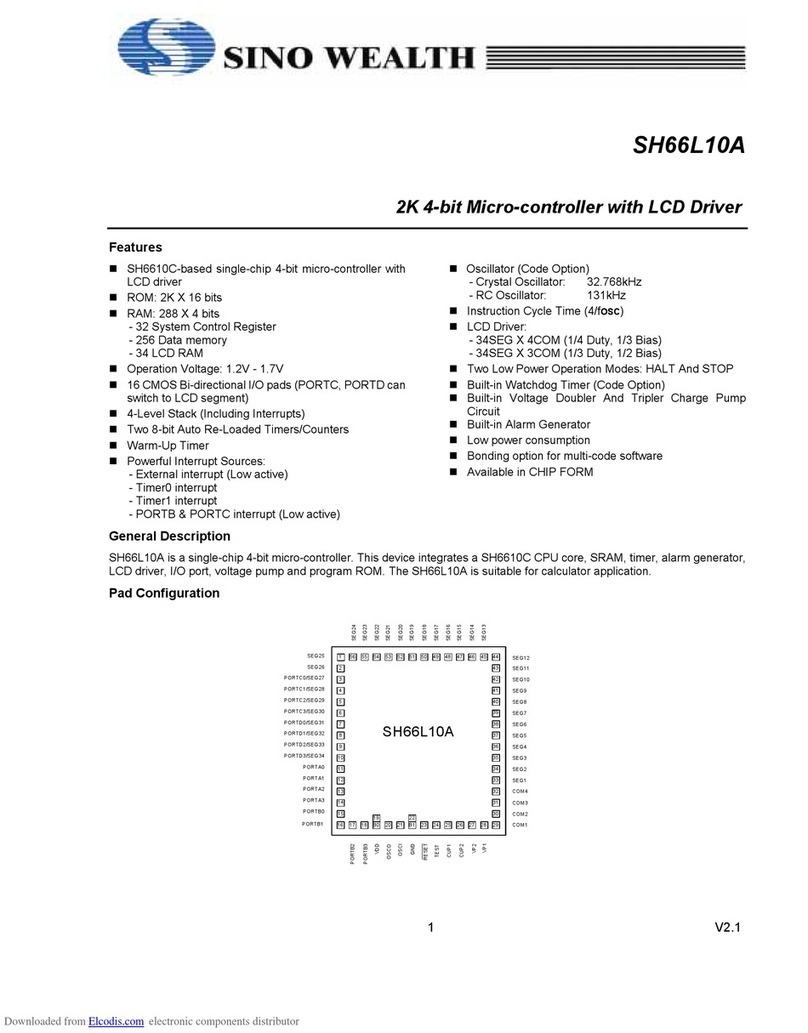

2.1. RAM Addressing

Data memory and system register can be accessed in one instruction by direct addressing. The following is the memory

allocation map:

System register: $000 - $02F, $380 - $3AF, $3C0 - $3C2

Data memory: $030 - $1A7

LCD RAM space: $300 - $313, $320 - $333

RAM Bank Table:

Bank 0

B = 0 Bank 1

B = 1 Bank 2

B = 2 Bank 3

B = 3 Bank 4

B = 4 Bank 5

B = 5 Bank 6

B = 6 Bank 7

B = 7

$000 - $07F $080 - $0FF $100 - $17F $180 - $1FF $200 - $27F $280 - $2FF $300 - $37F $380 - $3AF,

$3C0 - $3C2

Where, B: RAM bank bit use in instructions