Sino Wealth SH79F3281A User manual

Table of contents

Other Sino Wealth Microcontroller manuals

Sino Wealth

Sino Wealth SH69P55A User manual

Sino Wealth

Sino Wealth SH79F3283 User manual

Sino Wealth

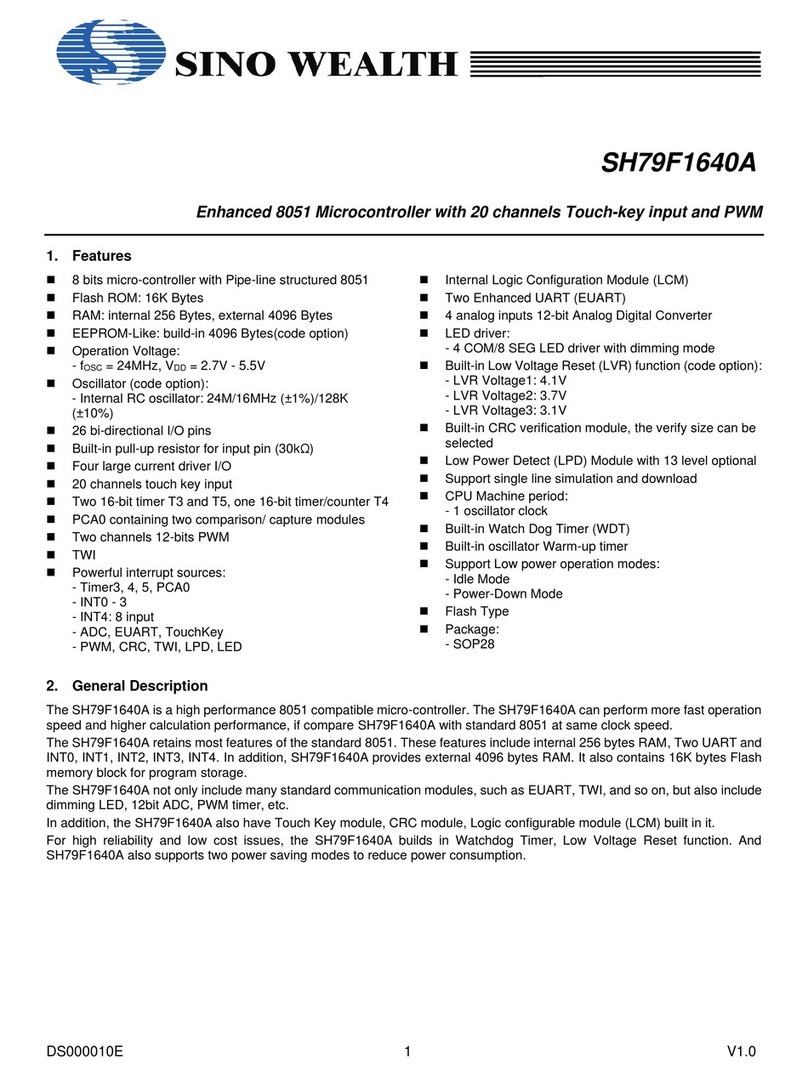

Sino Wealth SH79F1640A User manual

Sino Wealth

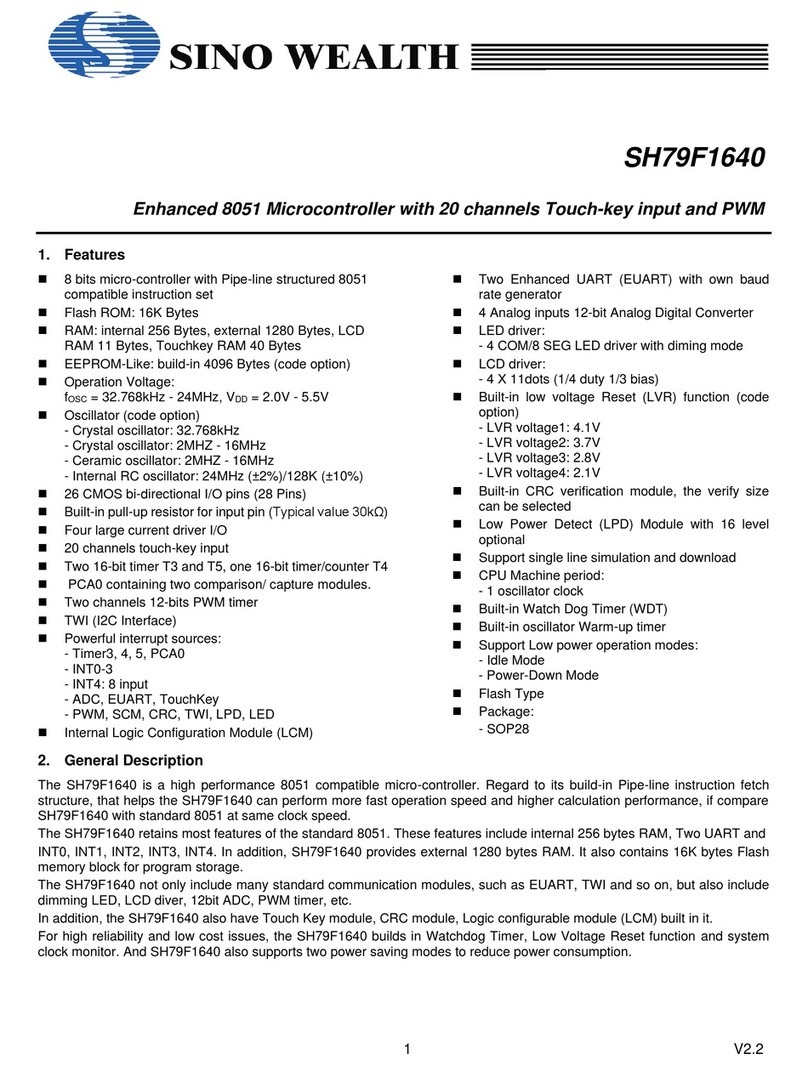

Sino Wealth SH79F1640 User manual

Sino Wealth

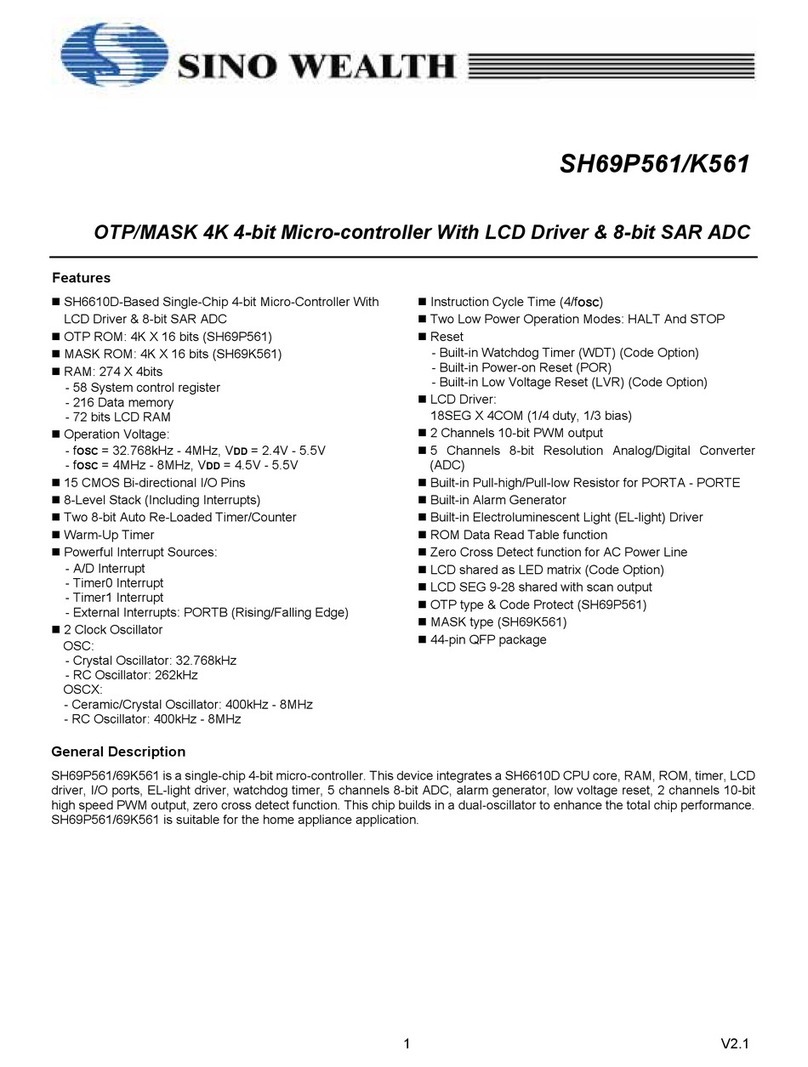

Sino Wealth SH69P561 User manual

Sino Wealth

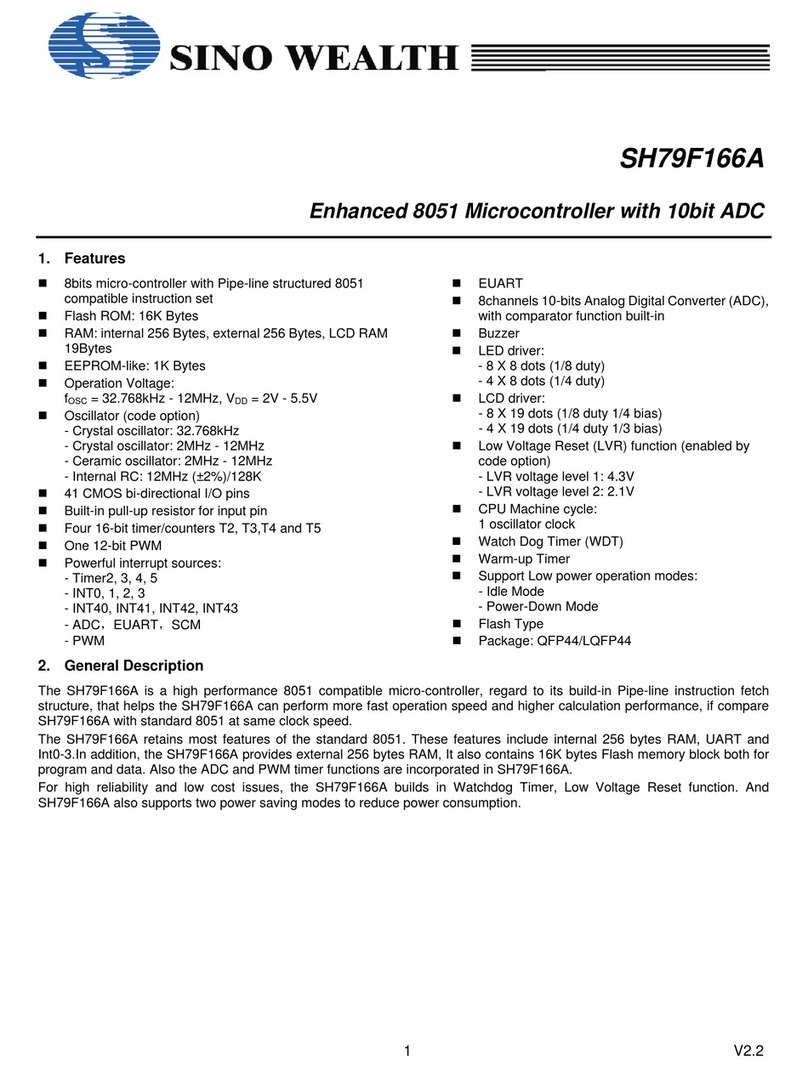

Sino Wealth SH79F166A User manual

Sino Wealth

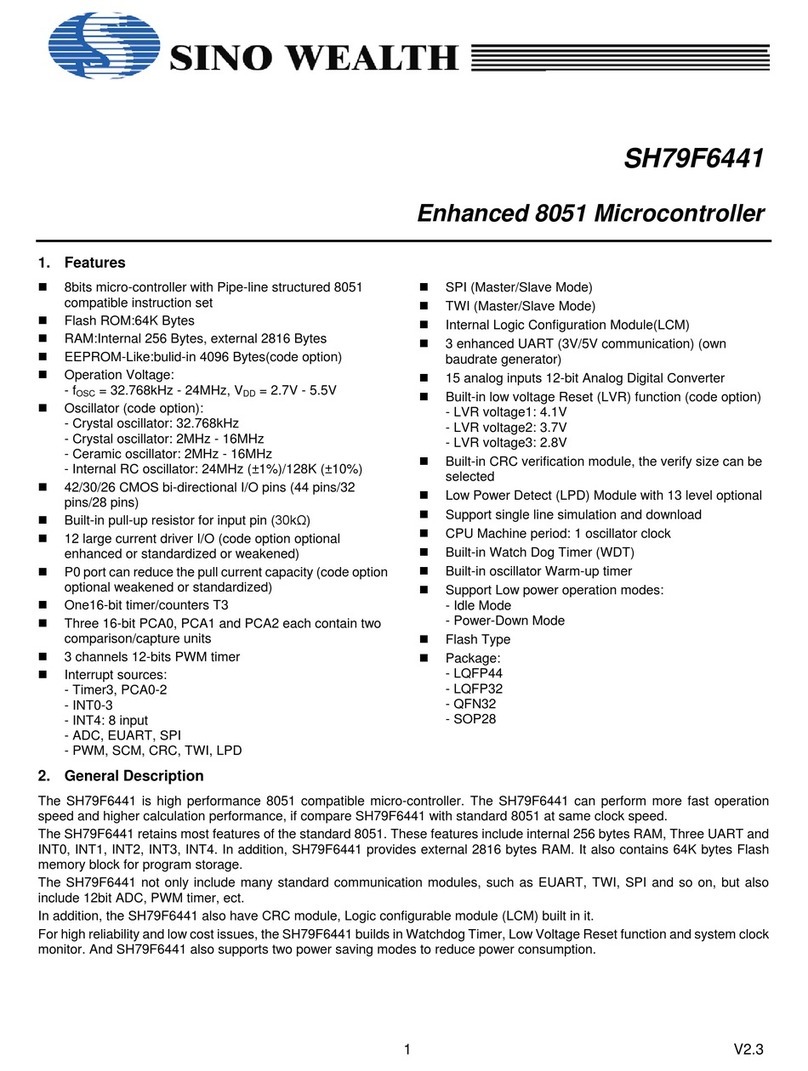

Sino Wealth SH79F6441 User manual

Sino Wealth

Sino Wealth SH79F7416 User manual

Sino Wealth

Sino Wealth SH61F83 User manual

Sino Wealth

Sino Wealth SH66L10A User manual

Popular Microcontroller manuals by other brands

Luminus

Luminus DK-114N-1 manual

STMicroelectronics

STMicroelectronics AN3248 Application note

Advanced Navigation

Advanced Navigation Spatial FOG Dual ETH Reference manual

Toshiba

Toshiba TLCS-870/C Series manual

Eurotech

Eurotech VIPER Quick start manual

Nuvoton

Nuvoton NuMicro NUC126 Series Technical reference manual

mikroElektronika

mikroElektronika Clicker 2 manual

Motorola

Motorola DSP56824ADM user manual

NXP Semiconductors

NXP Semiconductors FRDM-KL28Z user guide

NXP Semiconductors

NXP Semiconductors MC9S08PA4 Reference manual

mikroElektronika

mikroElektronika RS232 click manual

NGX Technologies

NGX Technologies BLUEBOARD-RL78 quick start guide

Texas Instruments

Texas Instruments TMS320F28004 Series manual

Silicon Laboratories

Silicon Laboratories AN1342 manual

Swatch

Swatch EM Microelectronic EMDVK8500 quick start guide

PIKODER

PIKODER USB2PPM user manual

Maxim Integrated

Maxim Integrated MAXREFDES132 manual

Winbond

Winbond W90P710 Programming guide