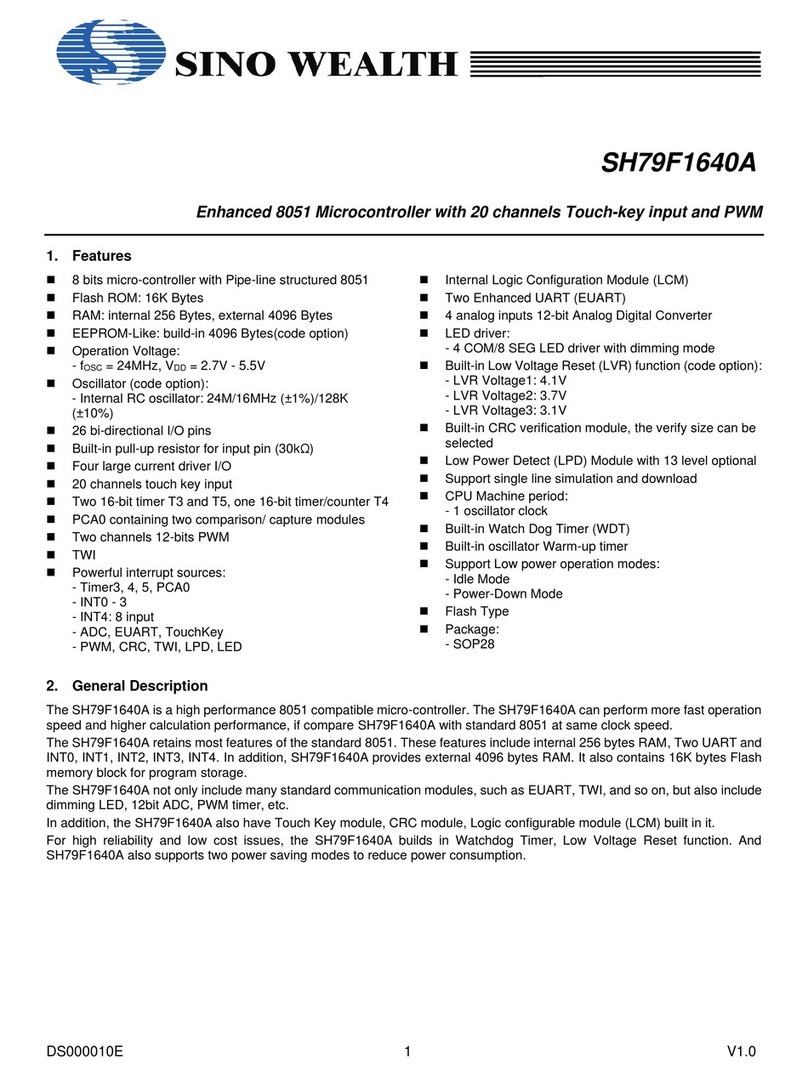

Sino Wealth SH79F1640 User manual

Table of contents

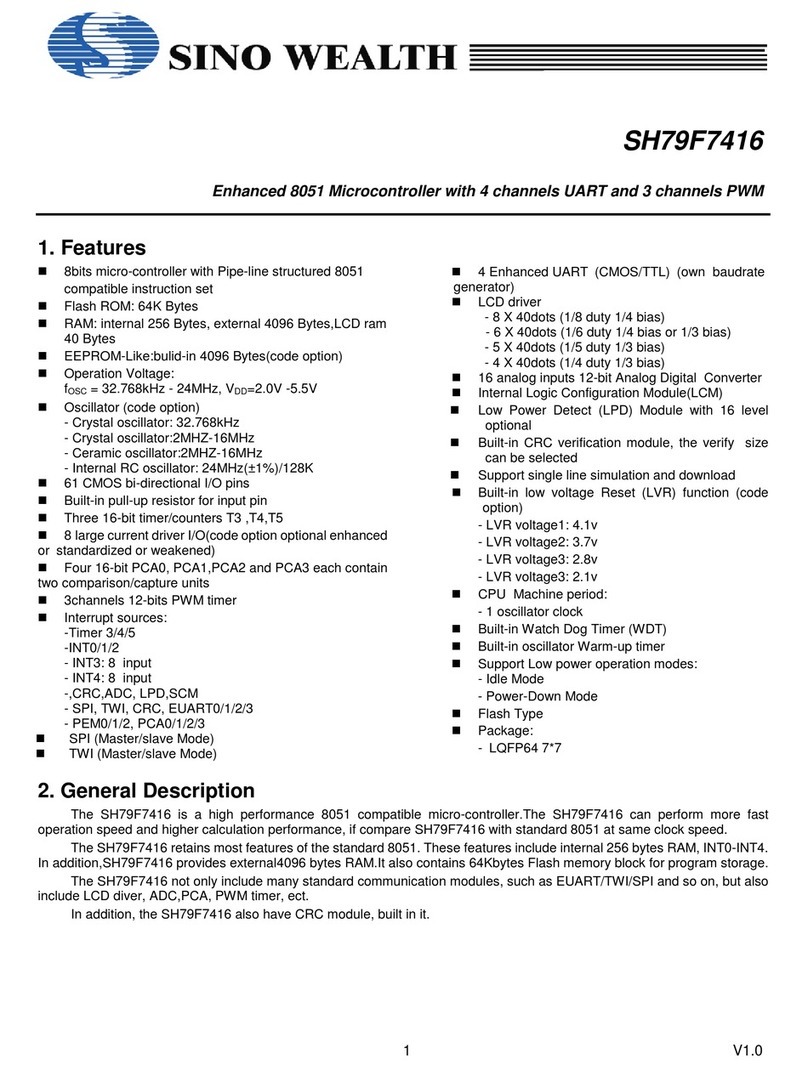

Other Sino Wealth Microcontroller manuals

Sino Wealth

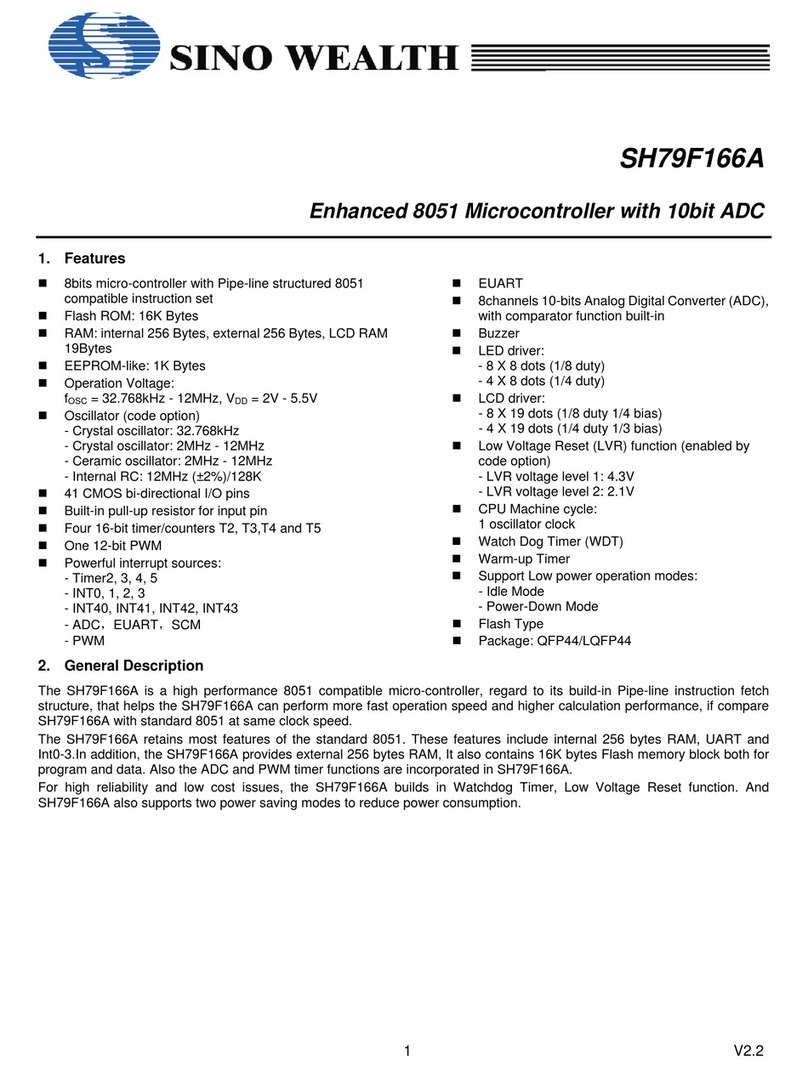

Sino Wealth SH79F166A User manual

Sino Wealth

Sino Wealth SH69P55A User manual

Sino Wealth

Sino Wealth SH79F9661A User manual

Sino Wealth

Sino Wealth SH79F3283 User manual

Sino Wealth

Sino Wealth SH79F1622 User manual

Sino Wealth

Sino Wealth SH79F6441 User manual

Sino Wealth

Sino Wealth SH69P561 User manual

Sino Wealth

Sino Wealth SH79F3281A User manual

Sino Wealth

Sino Wealth SH61F83 User manual

Sino Wealth

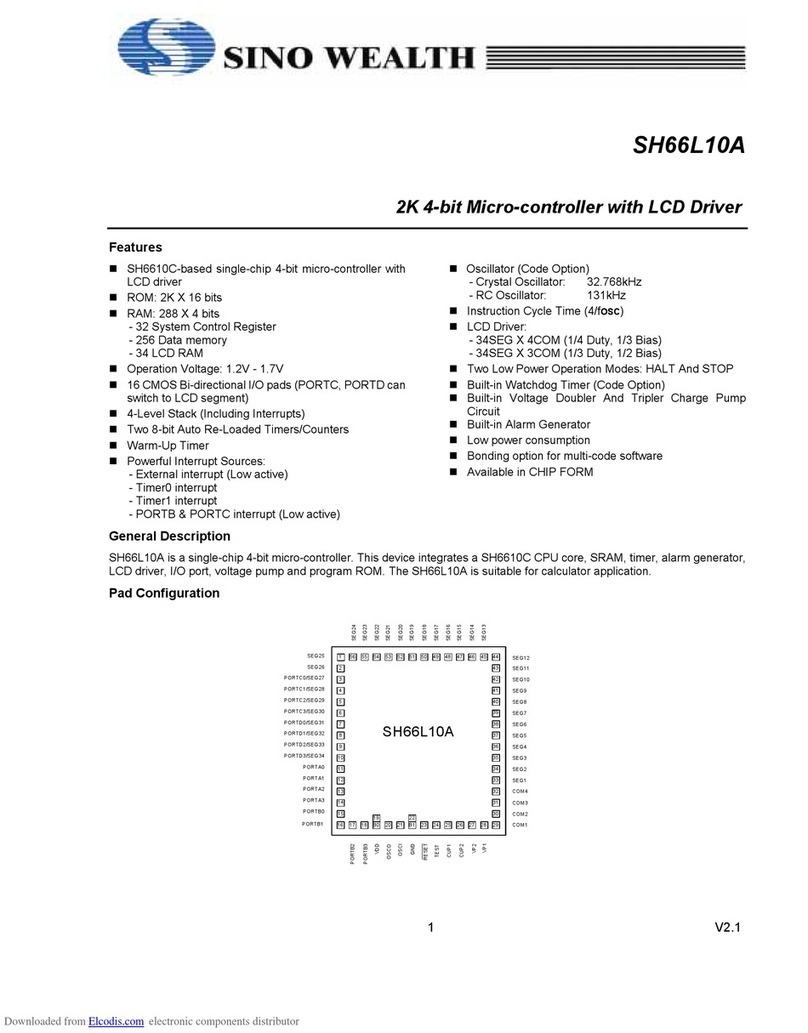

Sino Wealth SH66L10A User manual

Popular Microcontroller manuals by other brands

Silicon Laboratories

Silicon Laboratories C8051F41 Series user guide

DEUTSCHMANN AUTOMATION

DEUTSCHMANN AUTOMATION UNIGATE IC-DeviceNet instruction manual

Cypress Semiconductor

Cypress Semiconductor EZ-USB GX3 CY4701 Reference Design Guide

Jorjin

Jorjin WS2118E00 user guide

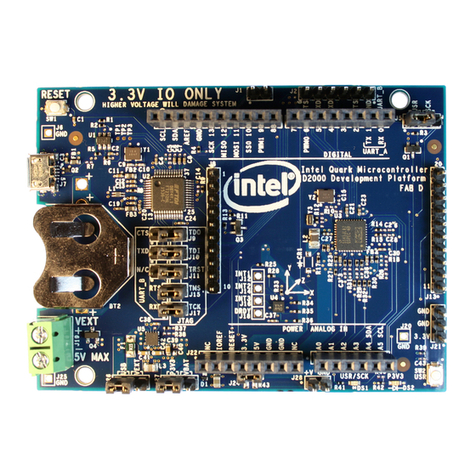

Intel

Intel Quark D2000 user guide

NXP Semiconductors

NXP Semiconductors LPC18xx series user manual

Silicon Laboratories

Silicon Laboratories EFM32 Hardware Design Guidelines

Silicon Laboratories

Silicon Laboratories C8051F336DK user guide

FDI

FDI uEZGUI-4088-43WQN user manual

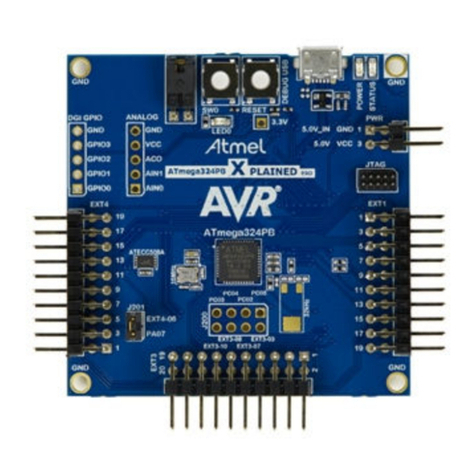

Atmel

Atmel ATmega324PB Getting started

Atmel

Atmel ATZB-EVB-24-SMA user manual

NXP Semiconductors

NXP Semiconductors UM108 Series user guide