Texas Instruments TMS320C6201 User manual

Other Texas Instruments Computer Hardware manuals

Texas Instruments

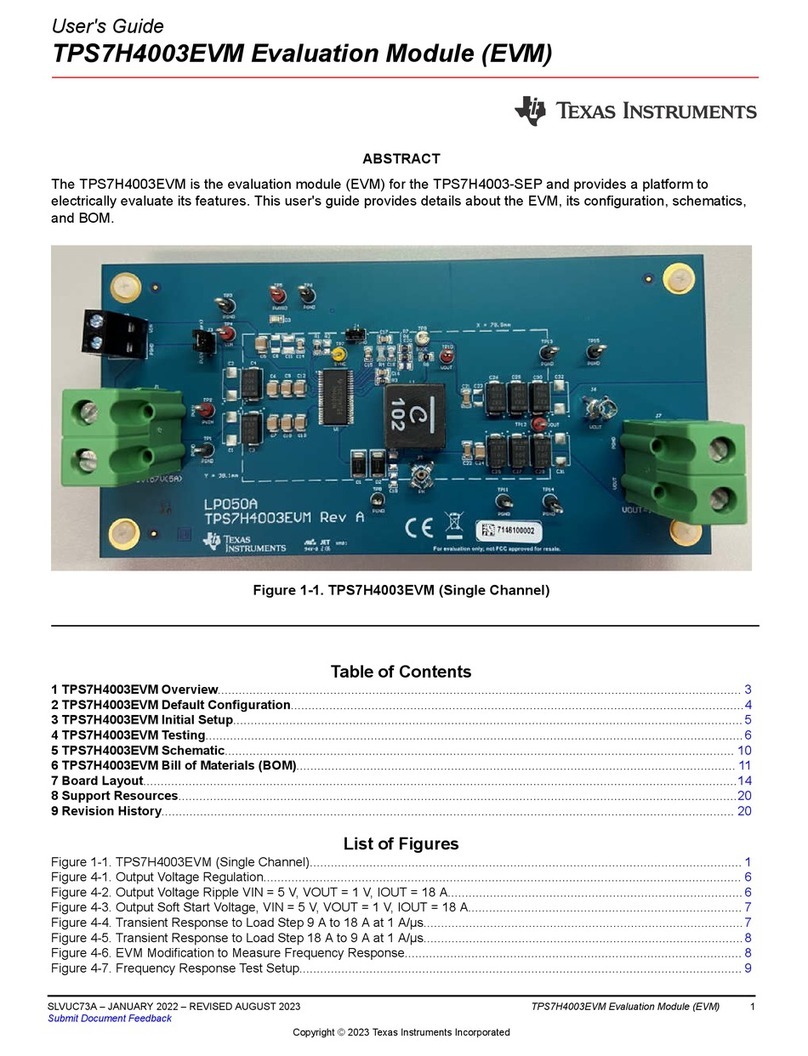

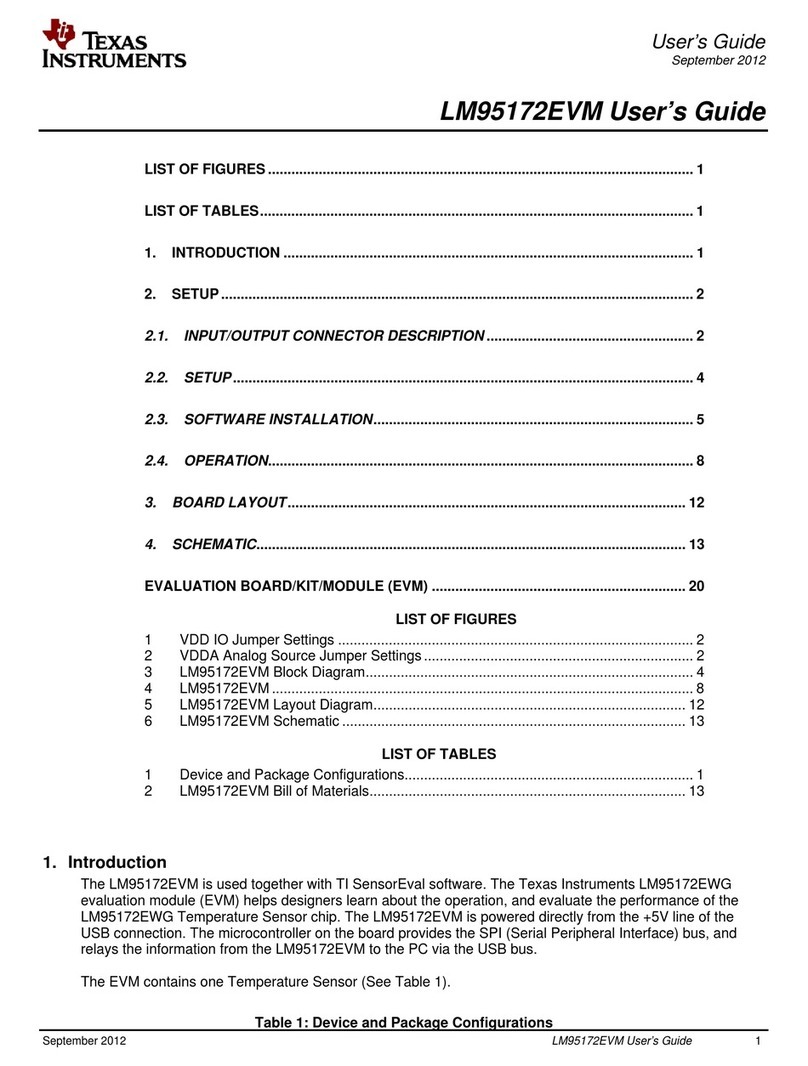

Texas Instruments LM95172EVM User manual

Texas Instruments

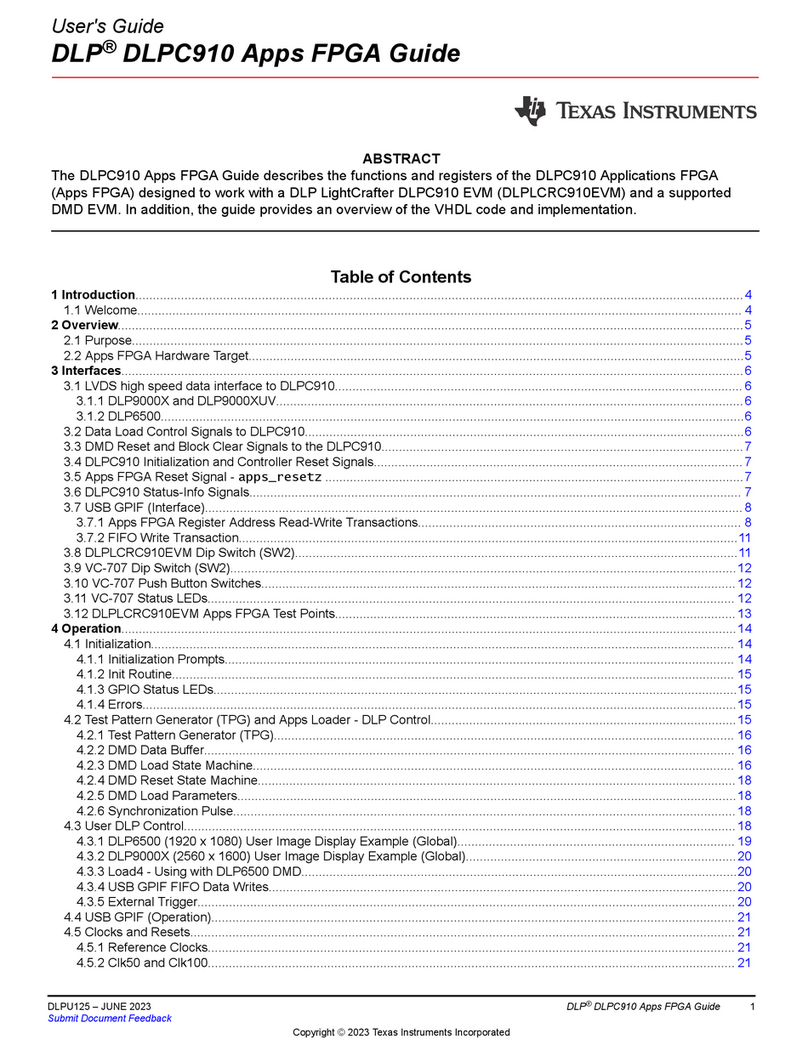

Texas Instruments DLPLCRC910EVM User manual

Texas Instruments

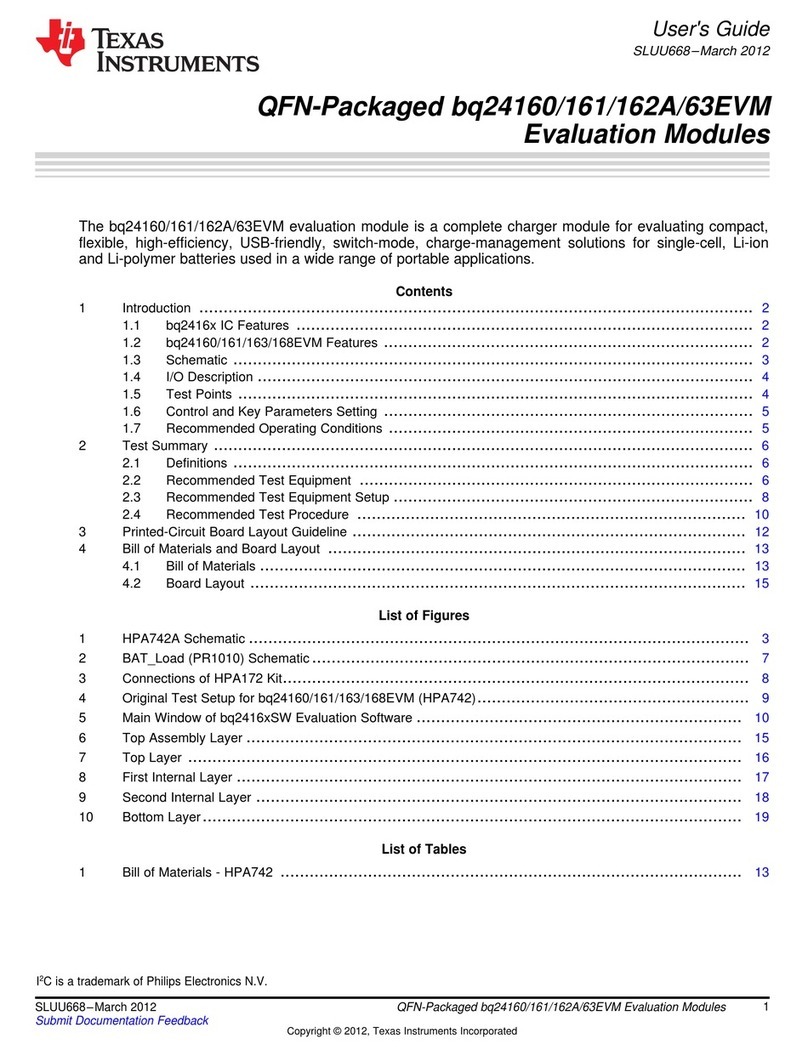

Texas Instruments bq2416063EVM User manual

Texas Instruments

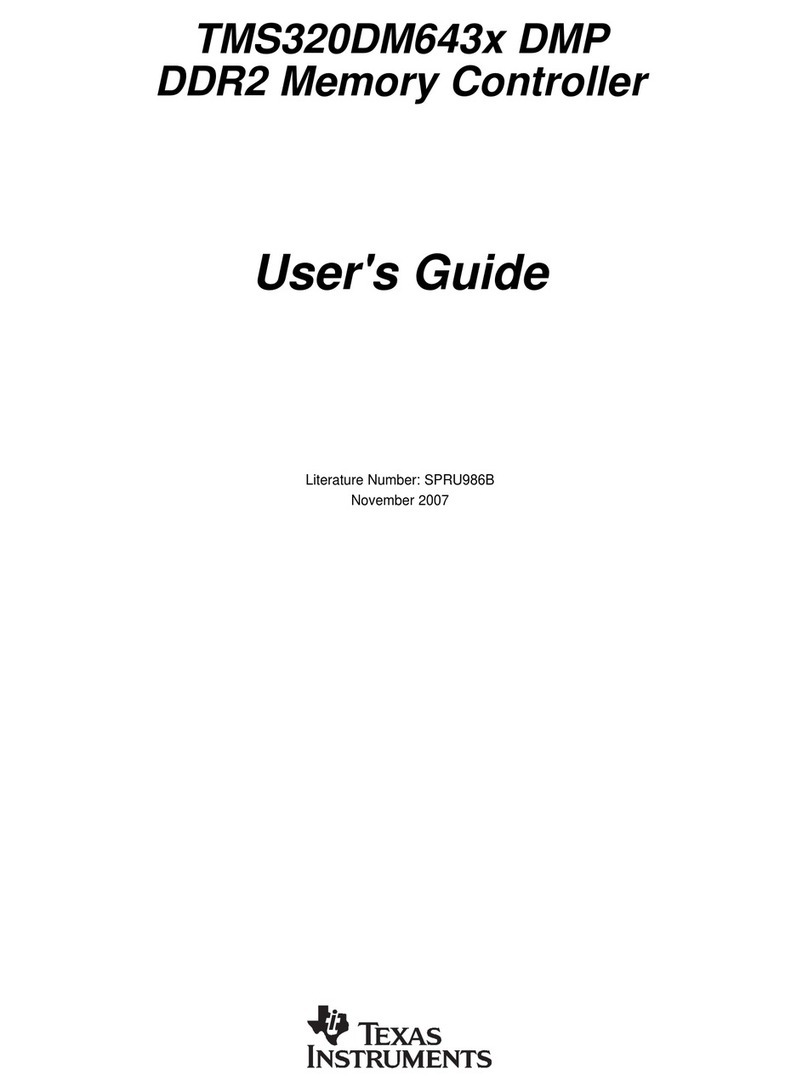

Texas Instruments TMS320DM643 User manual

Texas Instruments

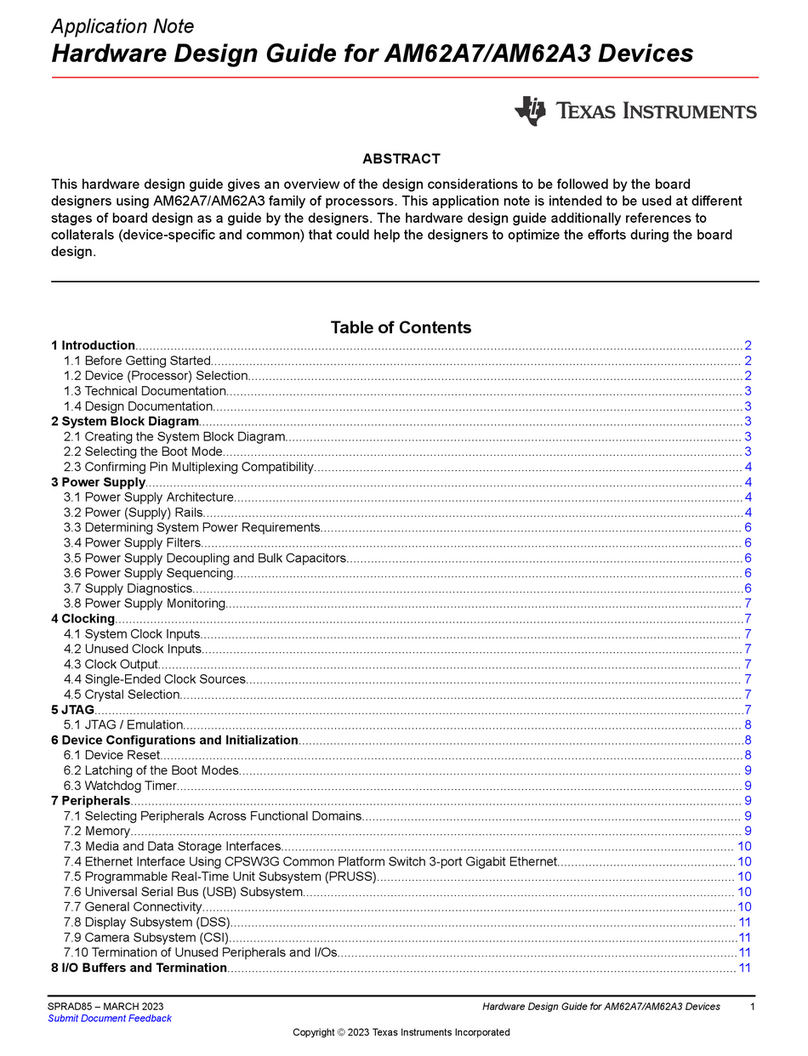

Texas Instruments AM62A7 Guide

Texas Instruments

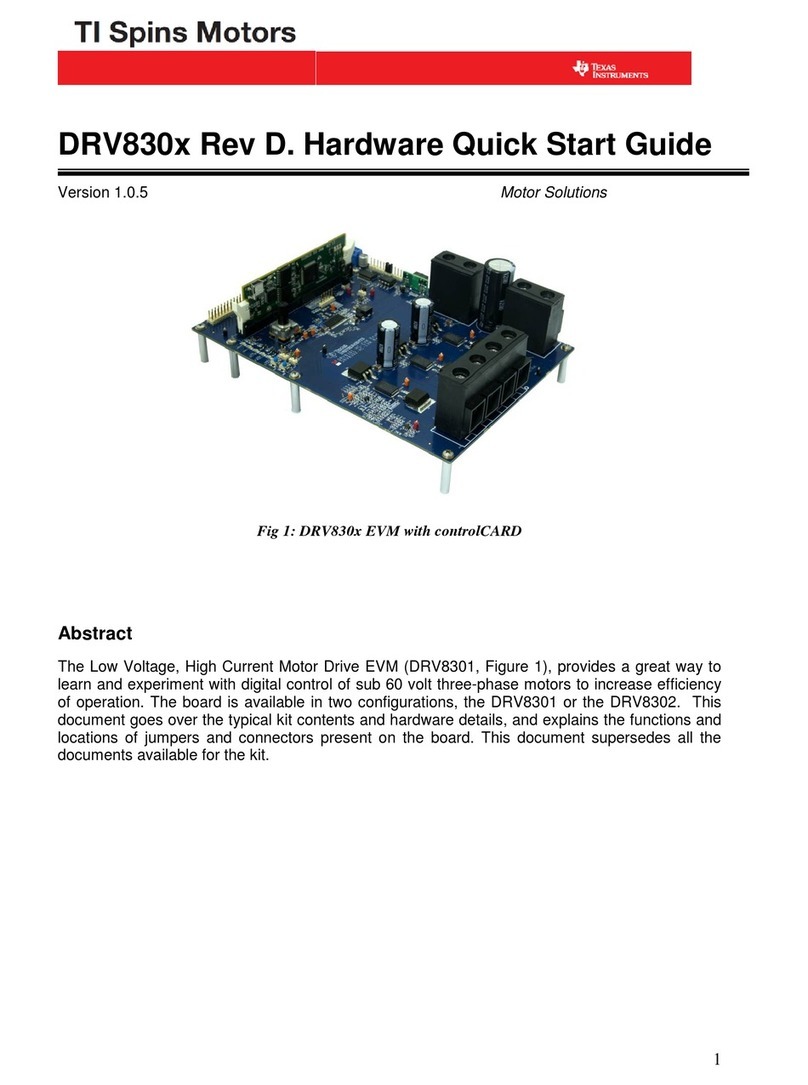

Texas Instruments DRV830x Rev D. User manual

Texas Instruments

Texas Instruments TAS3002 Installation and user guide

Texas Instruments

Texas Instruments TMS320C3x User manual

Texas Instruments

Texas Instruments TPS650231EVM User manual

Texas Instruments

Texas Instruments OMAP35 Series User manual

Texas Instruments

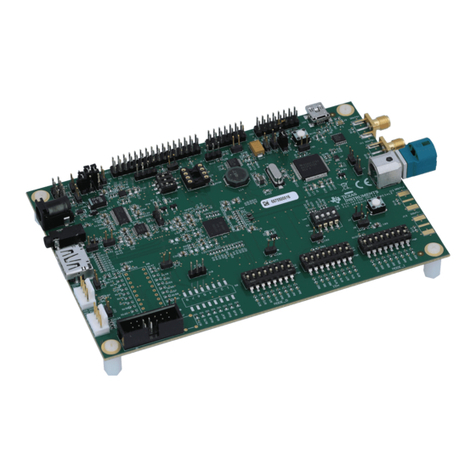

Texas Instruments DS90Ux929-Q1EVM User manual

Texas Instruments

Texas Instruments OMAP-L137 EVM User manual

Texas Instruments

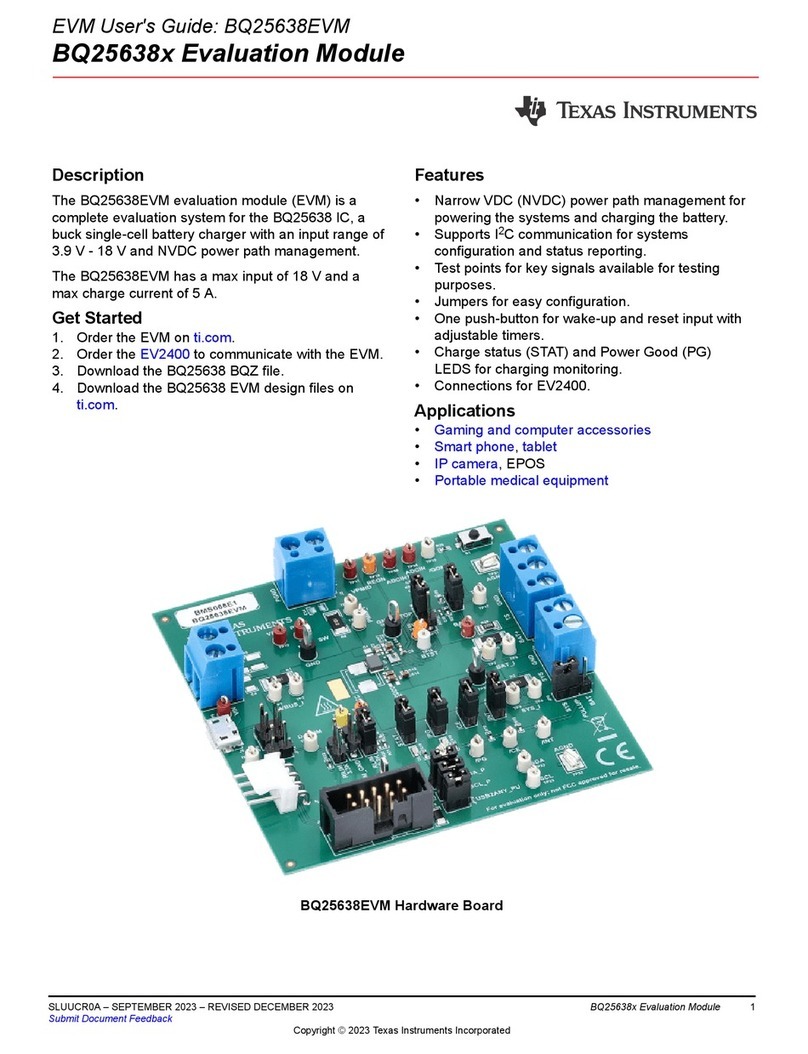

Texas Instruments BQ25638 Series User manual

Texas Instruments

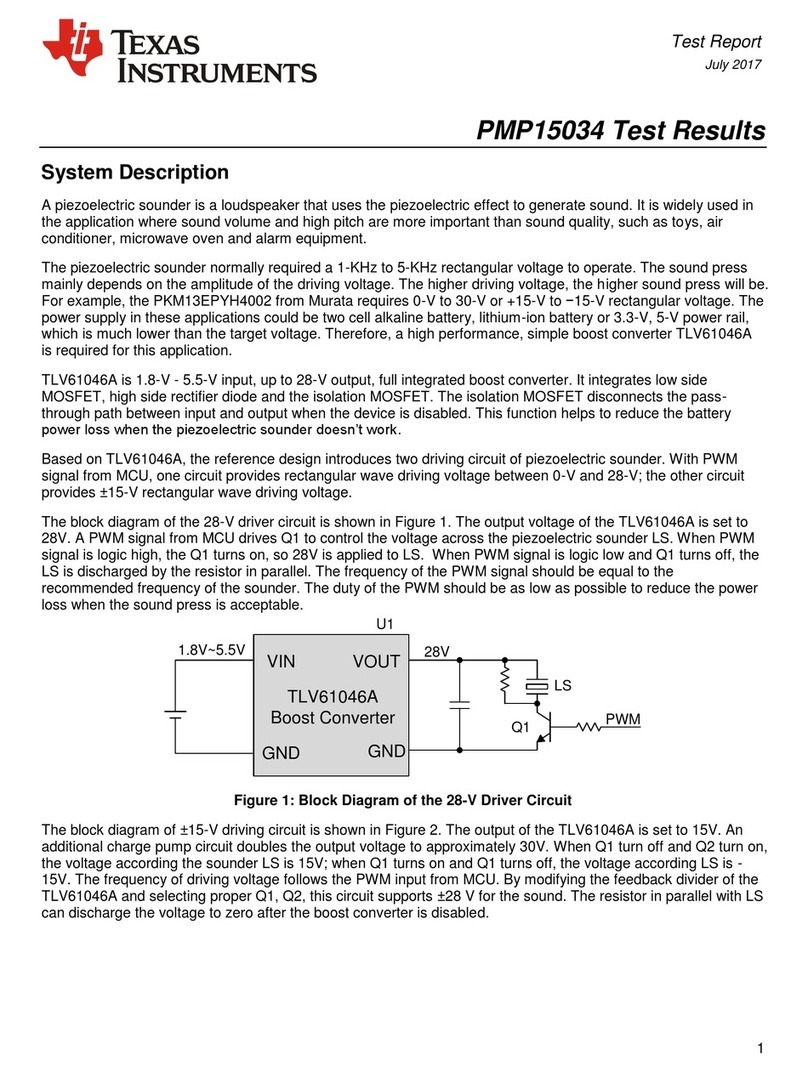

Texas Instruments PMP15034 User manual

Texas Instruments

Texas Instruments CC2540 User manual

Texas Instruments

Texas Instruments TVP5154EVM User manual

Texas Instruments

Texas Instruments Jacinto 7 DRA829 User manual

Texas Instruments

Texas Instruments CC2533 Installation manual

Texas Instruments

Texas Instruments TAS5707EVM User manual

Texas Instruments

Texas Instruments PGA309EVM User manual

Popular Computer Hardware manuals by other brands

EMC2

EMC2 VNX Series Hardware Information Guide

Panasonic

Panasonic DV0PM20105 Operation manual

Mitsubishi Electric

Mitsubishi Electric Q81BD-J61BT11 user manual

Gigabyte

Gigabyte B660M DS3H AX DDR4 user manual

Raidon

Raidon iT2300 Quick installation guide

National Instruments

National Instruments PXI-8186 user manual