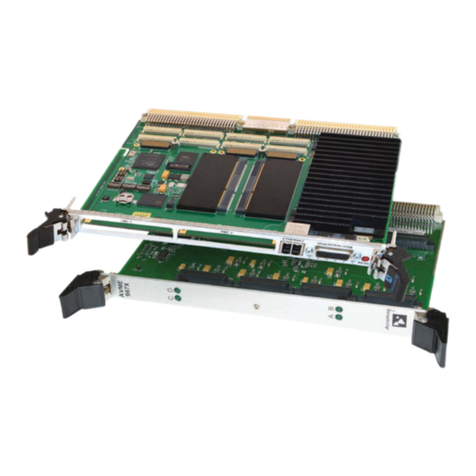

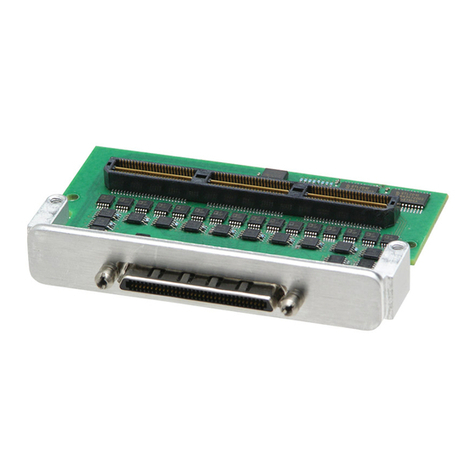

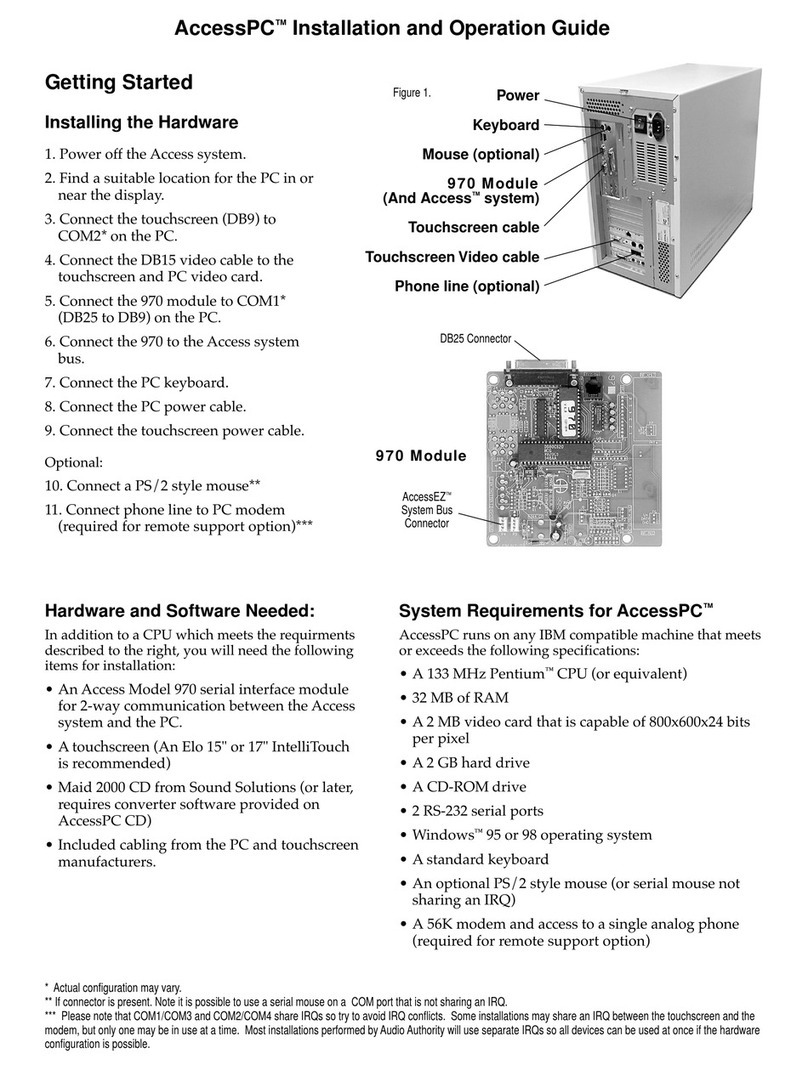

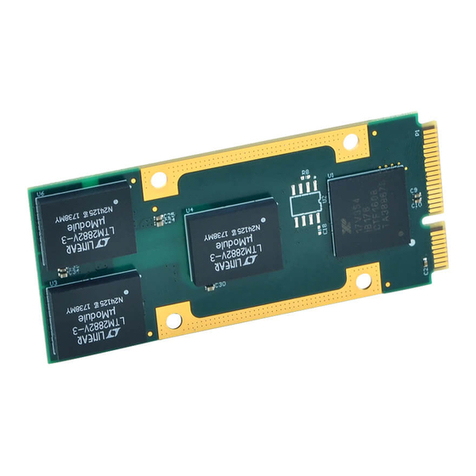

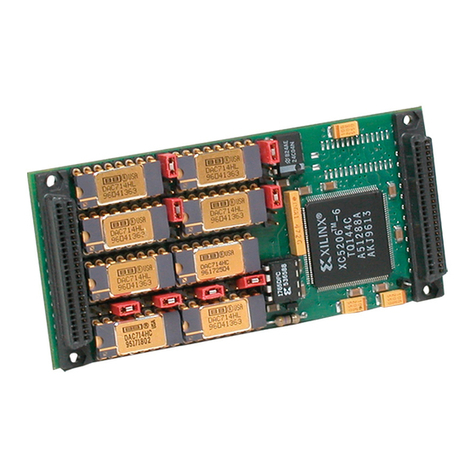

NOTE 2: APCE7020E-LF IS AN EXAMPLE OF A CARRIER THAT USES THE

CHAMP CONNECTOR SEE IMAGE OF CARRIER........................................................... 20

2.5 Noise and Grounding Considerations ..........................................................................20

2.6 Logic Interface Connector ...........................................................................................20

Table 2.4: Logic Interface Connections........................................................................................ 20

3.0 PROGRAMMING INFORMATION........................................................................... 22

CONFIGURATION REGISTERS................................................................................................................22

Table 3.1 Configuration Registers................................................................................................ 23

Table 3.2: AP482 Memory Map................................................................................................... 23

Global Interrupt Enable Status Register (Read/Write) - (BAR0 + 0x0000 0000) ....................................27

Table 3.3 Global Interrupt Register ............................................................................................ 27

Module Location In System Register (Read Only) - (BAR0 + 0x0000 0004)............................................28

Table 3.4 Location Register........................................................................................................ 28

Counters Interrupt Status/Clear Register (Read/Write) - (BAR0 + 0x0000 0008) ..................................28

Table 3.5 Counter Interrupt Status Clear Register..................................................................... 29

Counter Interrupt Enable/Disable Register (Read/Write) - (BAR0 + 0x0000 000C) ...............................29

Table 3.6 Counter Interrupt Enable Register............................................................................. 29

Counter Trigger Register (Write) - (BAR0 + 0x0000 0010).....................................................................30

Table 3.7 Counter Trigger Register ............................................................................................ 30

Counter Stop Register (Write) - (BAR0 + 0x0000 0014).........................................................................31

Table 3.8 Counter Stop Register ................................................................................................ 31

Load Read Back Register (Write) - (BAR0 + 0x0000 0018).....................................................................31

Table 3.9 Load Read Back Register ............................................................................................ 32

Toggle Counter Constants Register (Read/Write) - (BAR0 + 0x0000 001C) ...........................................32

Table 3.10 Toggle Counter Constant Register ........................................................................... 32

Counter Control Register (Read/Write)................................................................................................33

Quadrature Position Measurement .....................................................................................................34

Figure 3.1 Quadrature Cycles with X4 Encoding........................................................................ 34

Table 3.11 Counter Control Register (Quadrature Position Measurement).............................. 35

Pulse Width Modulation ......................................................................................................................37

Table 3.12 Counter Control Register (Pulse Width Modulation)............................................... 38

Watchdog Timer Operation .................................................................................................................39

Table 3.13 Counter Control Register (Watchdog Timer) ........................................................... 40

Event Counting Operation....................................................................................................................41

Table 3.14 Counter Control Register (Event Counting) ............................................................. 42

Frequency Measurement Operation ....................................................................................................43

Table 3.15 Counter Control Register (Frequency Measurement) ............................................. 44

Input Pulse Width Measurement .........................................................................................................45

Table 3.16 Counter Control Register (Pulse Width Measurement)........................................... 46

Input Period Measurement..................................................................................................................47