-

1.0 GENERAL INFORMATION ................................................................................................................. 5

KEY FEATURES.................................................................................................................................. 5

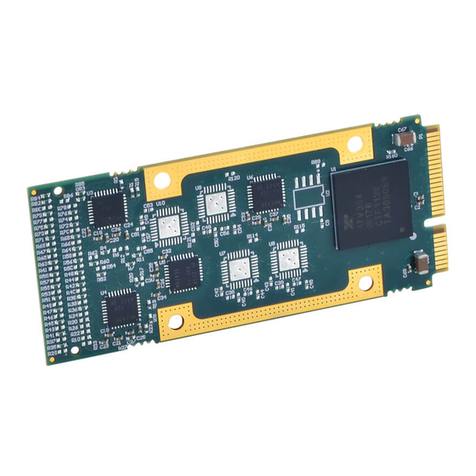

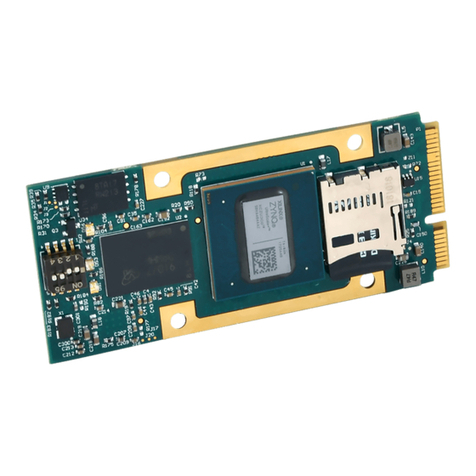

ENGINEERING DESIGN KIT ............................................................................................................... 6

BOARD CONTROL SOFTWARE.......................................................................................................... 6

2.0 PREPARATION FOR USE ................................................................................................................... 6

UNPACKING AND INSPECTION......................................................................................................... 6

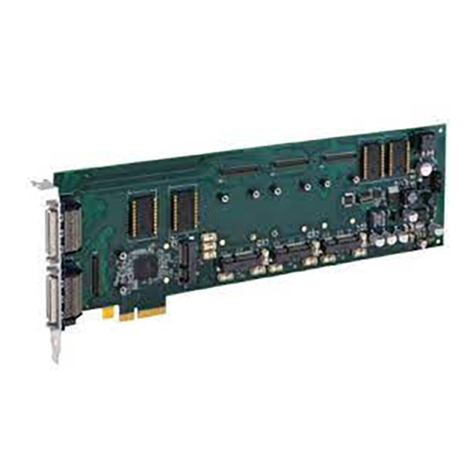

CARD CAGE CONSIDERATIONS......................................................................................................... 6

Front Panel Field I/O Connector J1 .................................................................................................. 8

Analog Inputs: Noise and Grounding Considerations...................................................................... 9

Non-Isolation Considerations .......................................................................................................... 9

3.0 PROGRAMMING INFORMATION...................................................................................................... 9

AXM-A75 Memory Map................................................................................................................... 9

FLASH Data Format ........................................................................................................................13

Board Status and Reset Register (Read/Write, PCIBar2 + 8000H)................................................. 14

Control Register - (Read/Write, PCIBar2 + 8100H) ........................................................................15

Status Register 0 - (Read/Write, PCIBar2 + 8104H) ....................................................................... 16

Status Register 1 - (Read/Write, PCIBar2 + 8108H) ....................................................................... 16

Digital I/O (Read/Write, PCIBar2 + 810CH).................................................................................... 16

Conversion Timer Register - (Read/Write, PCIBar2 + 8110H)........................................................ 16

FLASH Data Register - (Read/Write, PCIBar2 + 8114H) ................................................................. 17

Digital I/O Direction Register - (Read/Write, PCIBar2 + 8118H).................................................... 17

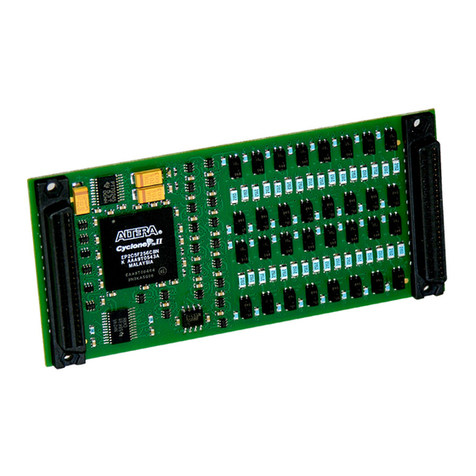

ADC Channels................................................................................................................................. 17

ADC Data Format ........................................................................................................................... 18

ADC Offset Register........................................................................................................................18

ADC Gain Register .......................................................................................................................... 18

Uncalibrated ADC Performance..................................................................................................... 19

Analog Input Channel Calibration Procedure ................................................................................ 19

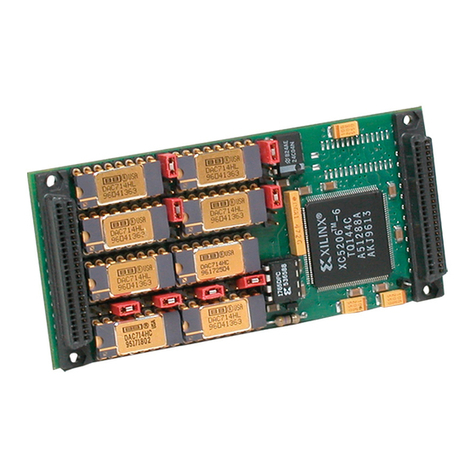

DAC Channels................................................................................................................................. 20

DAC Data Register.......................................................................................................................... 20

DAC Coarse Gain Register ..............................................................................................................21

DAC Fine Gain Register ..................................................................................................................21

DAC Offset Register........................................................................................................................22

Updating DAC outputs ................................................................................................................... 22

4.0 THEORY OF OPERATION................................................................................................................. 22

Field I/O Connections.....................................................................................................................22