KINTEX UltraScale+ FPGA Board AXKU040 User Manual

Table of Contents

Version Record.......................................................................................................2

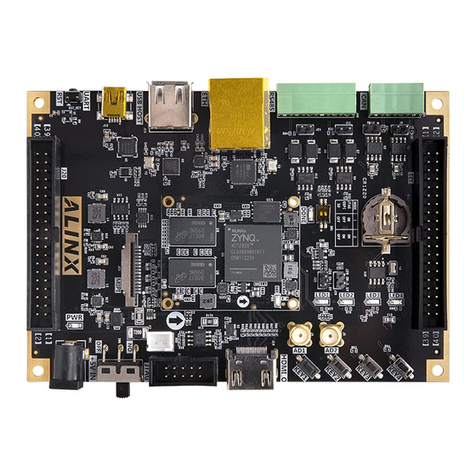

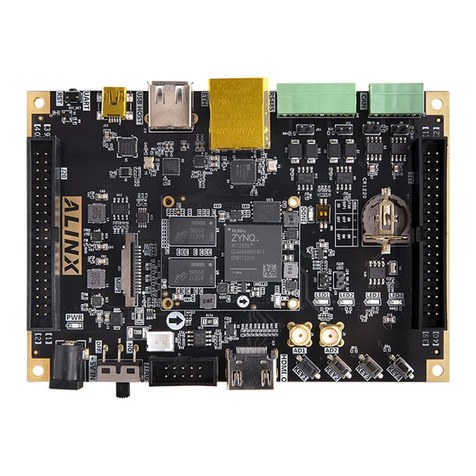

Part 1: FPGA Development Board Introduction............................................... 4

Part 2: FPGA Chip................................................................................................. 8

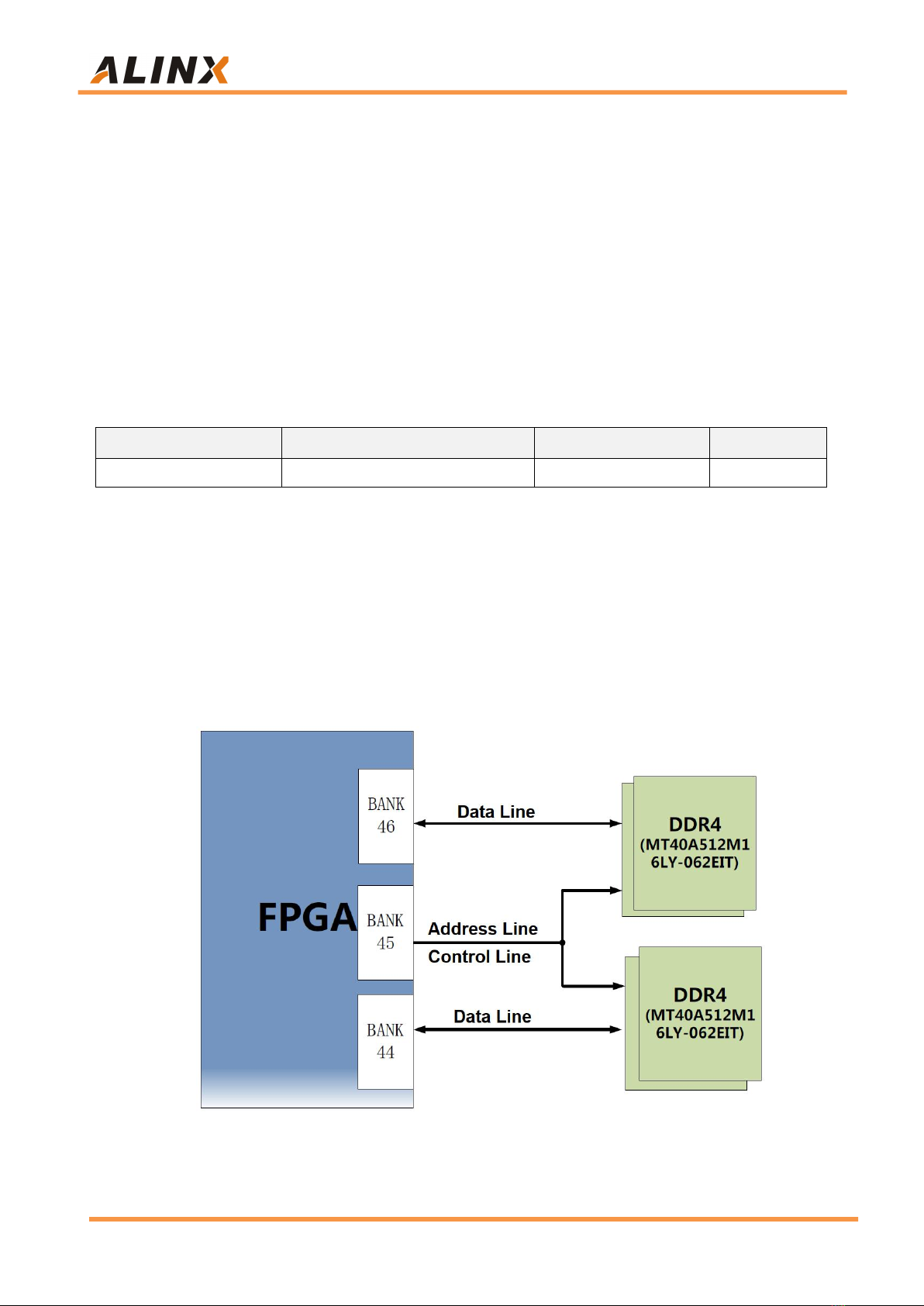

Part 3: DDR4 DRAM...........................................................................................10

Part 4: QSPI Flash.............................................................................................. 15

Part 5: Clock configuration.................................................................................16

Part 5.1: 200Mhz differential clock source..............................................16

Part 5.2: 125Mhz differential clock source..............................................16

Part 5.3: 156.25Mhz differential clock source........................................17

Part 6: USB to Serial Port.................................................................................. 19

Part 7: SFP+ Optical fiber interface................................................................. 20

Part 8: HDMI Video Output Interface............................................................... 22

Part 9: Gigabit Ethernet Interface.....................................................................24

Part 10: FMC Expansion Port........................................................................... 27

Part 11: SD Card Slot......................................................................................... 47

Part 12: SMA and SATA Interface.....................................................................49

Part 13: Temperature Sensor............................................................................ 51

Part 14: JTAG Interface......................................................................................52

Part 15: LED Light...............................................................................................53

Part 16: Keys........................................................................................................55

Part 17: Power Supply........................................................................................56

Part 18: Fan..........................................................................................................58

Part 19: Form Factory.........................................................................................59