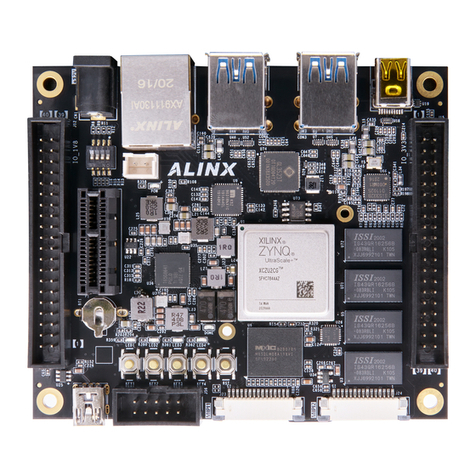

ZYNQ Ultrascale + FPGA Board AXU7EV User Manual

Amazon Store: https://www.amazon.com/alinx

Table of Contents

Version Record.......................................................................................................2

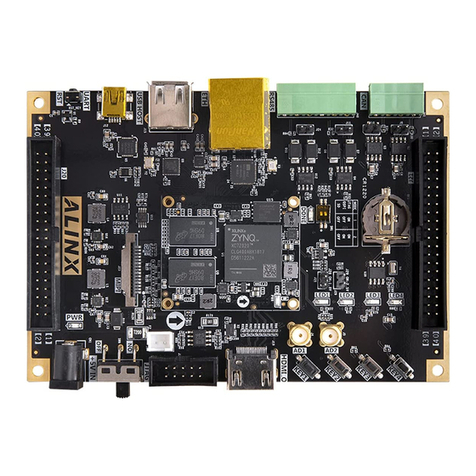

Part 1: FPGA Development Board Introduction............................................... 6

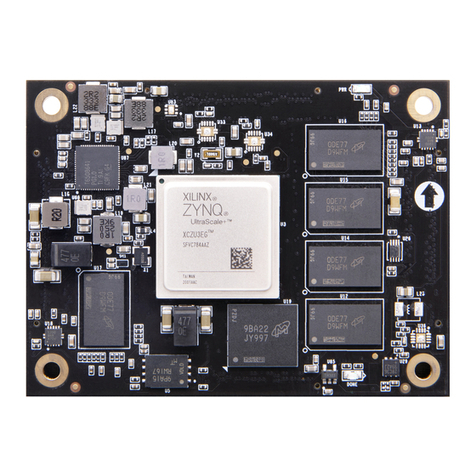

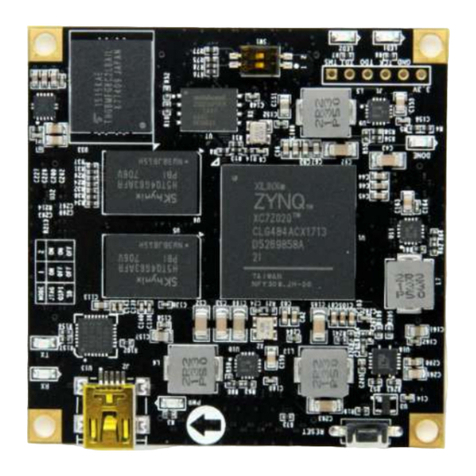

Part 2: ACU7EV Core Board............................................................................. 11

Part 2.1: ACU7EV Core Board Introduction............................................11

Part 2.2: ZYNQ Chip...................................................................................12

Part 2.3: DDR4 DRAM............................................................................... 14

Part 2.4: QSPI Flash...................................................................................23

Part 2.5: eMMC Flash.................................................................................24

Part 2.6: Clock configuration..................................................................... 26

Part 2.7: Power Supply...............................................................................28

Part 2.8: ACU7EV Core Board Size Dimension.................................... 30

Part 2.9: Board to Board Connectors pin assignment..........................30

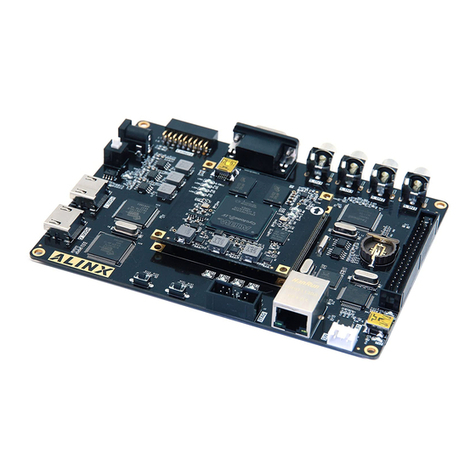

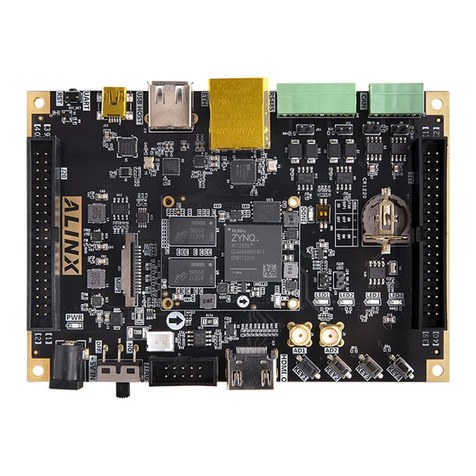

Part 3: Carrier Board...........................................................................................39

Part 3.1: Carrier Board Introduction.........................................................39

Part 3.2: PCIe Slot...................................................................................... 39

Part 3.3: M.2 Interface................................................................................42

Part 3.4: DP Interface................................................................................. 43

Part 3.5: USB3.0 Interface.........................................................................44

Part 3.6: HDMI Output Interface...............................................................46

Part 3.7: HDMI Input Interface.................................................................. 47

Part 3.8: Gigabit Ethernet Interface......................................................... 49

Part 3.9: USB to Serial Port.......................................................................52

Part 3.10: SFP Interface.............................................................................53

Part 3.11: SD Card Slot Interface............................................................. 54

Part 3.12: MIPI Camera Interface............................................................ 55

Part 3.13: FMC Interface............................................................................56

Part 3.14: CAN Communication Interface.............................................. 60