AT90S1200

3

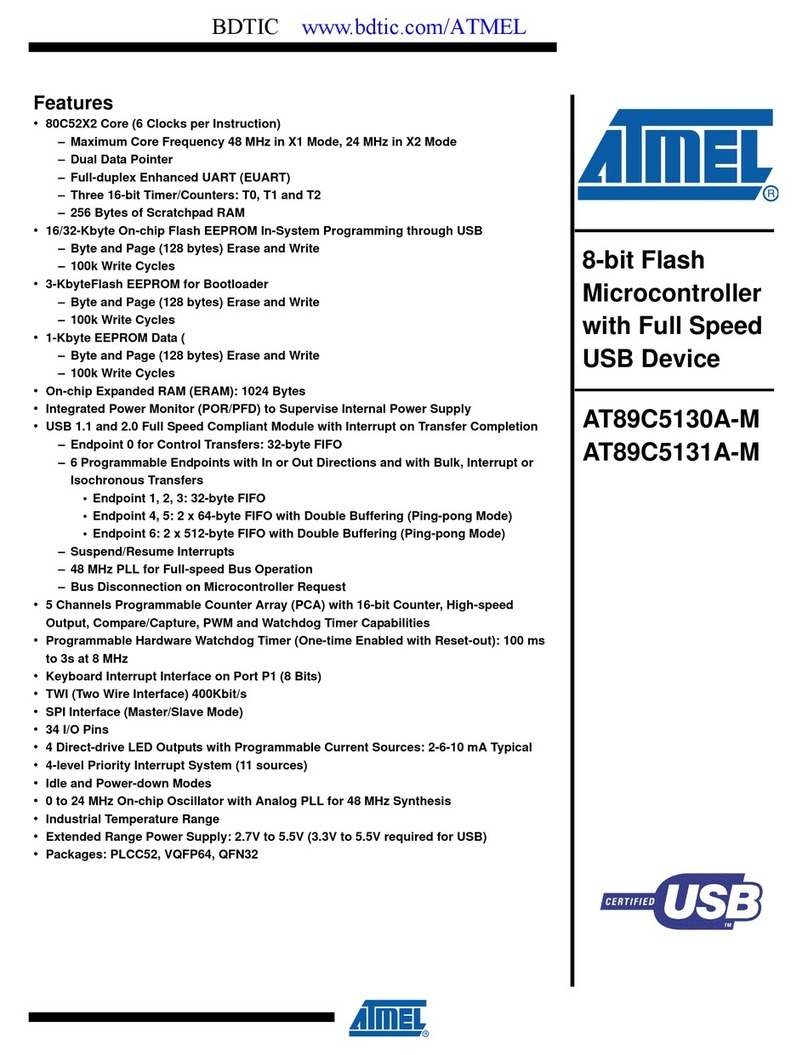

The architecture supports high level languages efficiently as well as extremely dense assembler code programs. The

AT90S1200 provides the following features: 1K bytes of In-System Programmable Flash, 64 bytes EEPROM, 15 general

purpose I/O lines, 32 general purpose working registers, internal and external interrupts, programmable Watchdog Timer

with internal oscillator, an SPI serial port for program downloading and two software selectable power saving modes. The

Idle Mode stops the CPU while allowing the registers, timer/counter, watchdog and interrupt system to continue functioning.

The power down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next

external interrupt or hardware reset.

The device is manufactured using Atmel’s high density nonvolatile memory technology. The on-chip In-System Program-

mable Flash allows the program memory to be reprogrammed in-system through an SPI serial interface or by a

conventional nonvolatile memory programmer. By combining an enhanced RISC 8-bit CPU with In-System Programmable

Flash on a monolithic chip, the Atmel AT90S1200 is a powerful microcontroller that provides a highly flexible and cost

effective solution to many embedded control applications.

The AT90S1200 AVR is supported with a full suite of program and system development tools including: macro assemblers,

program debugger/simulators, in-circuit emulators, and evaluation kits.

Pin Descriptions

VCC

Supply voltage pin.

GND

Ground pin.

Port B (PB7..PB0)

Port B is an 8-bit bi-directional I/O port. Port pins can provide internal pull-up resistors (selected for each bit). PB0 and PB1

also serve as the positive input (AIN0) and the negative input (AIN1), respectively, of the on-chip analog comparator. The

Port B output buffers can sink 20 mA and thus drive LED displays directly. When pins PB0 to PB7 are used as inputs and

are externally pulled low, they will source current if the internal pull-up resistors are activated. The Port B pins are tri-stated

when a reset condition becomes active, even if the clock is not active.

Port B also serves the functions of various special features of the AT90S1200 as listed on page 27.

Port D (PD6..PD0)

Port D has seven bi-directional I/O pins with internal pull-up resistors, PD6..PD0. The Port D output buffers can sink 20 mA.

As inputs, Port D pins that are externally pulled low will source current if the pull-up resistors are activated. The Port D pins

are tri-stated when a reset condition becomes active, even if the clock is not active.

Port D also serves the functions of various special features of the AT90S1200 as listed on page 31.

RESET

Reset input. A low level on this pin for more than 50 ns will generate a reset, even if the clock is not running. Shorter pulses

are not guaranteed to generate a reset.

XTAL1

Input to the inverting oscillator amplifier and input to the internal clock operating circuit.

XTAL2

Output from the inverting oscillator amplifier.

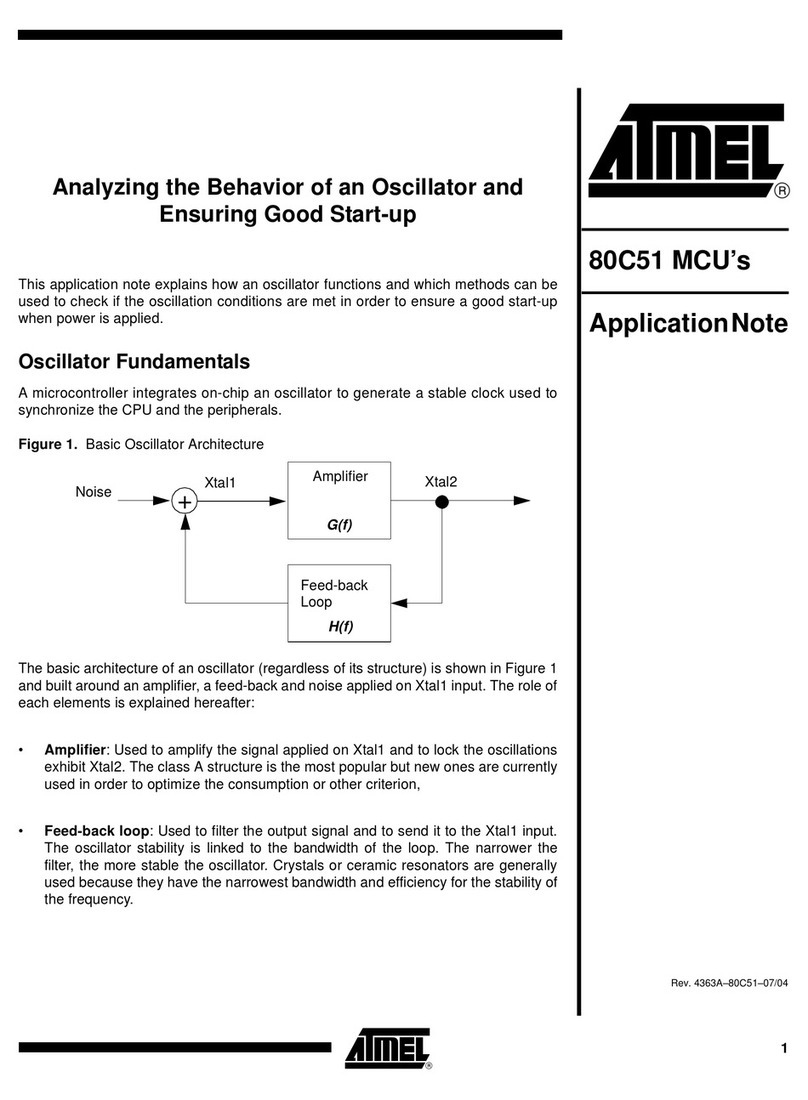

Crystal Oscillator

XTAL1 and XTAL2 are input and output, respectively, of an inverting amplifier which can be configured for use as an on-

chip oscillator, as shown in Figure 2. Either a quartz crystal or a ceramic resonator may be used. To drive the device from

an external clock source, XTAL2 should be left unconnected while XTAL1 is driven as shown in Figure 3.