CONTENTS

S1D13700 Technical Manual

EPSON

i

Table of Contents

1 Overview...............................................................................................................................1

1.1 Features.......................................................................................................................................1

1.2 System Overview.........................................................................................................................2

1.3 List of Abbreviations.....................................................................................................................4

2 Pins .......................................................................................................................................5

2.1 Pin Connection.............................................................................................................................5

2.1.1 Pin Assignments.............................................................................................................5

2.1.2 Pin Description...............................................................................................................6

2.1.3 Package Dimensions......................................................................................................8

2.2 Pin Functions...............................................................................................................................9

2.2.1 Power Supply Pins .........................................................................................................9

2.2.2 Oscillator and Clock Input Pins ......................................................................................9

2.2.3 System Bus Connecting Pins.......................................................................................10

2.2.4 LCD Driver Control Pins...............................................................................................13

2.2.5 TEST Control Pins........................................................................................................13

3 Commands and Command Registers..............................................................................14

3.1 Types of Commands (when Indirectly Interfaced)......................................................................14

3.2 Command Register Map (when Directly Interfaced)..................................................................15

3.3 Command Description ...............................................................................................................17

3.3.1 Operation Control Commands......................................................................................17

3.3.2 Display Control Commands..........................................................................................25

3.3.3 Drawing Control Commands........................................................................................43

3.3.4 Memory Control Commands ........................................................................................44

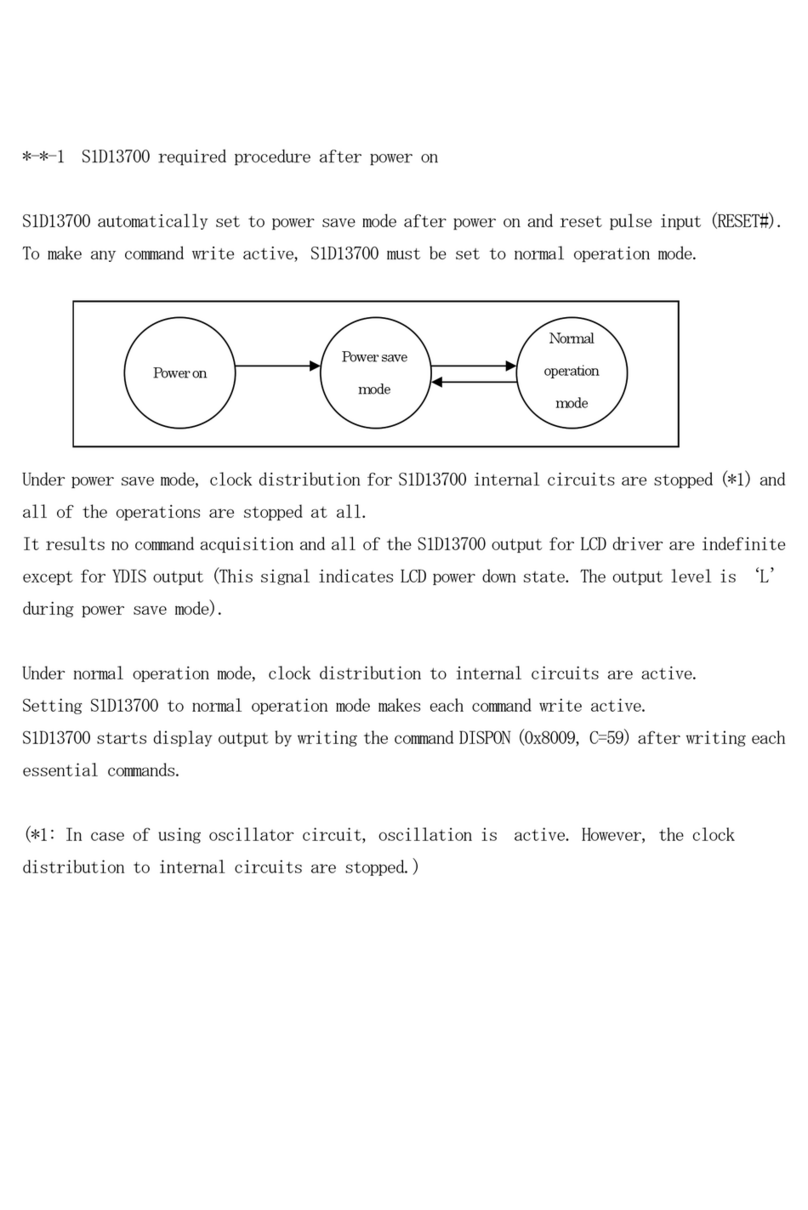

4 Function Description.........................................................................................................45

4.1 Display Functions.......................................................................................................................45

4.1.1 Screen Management....................................................................................................45

4.1.2 Character Generator (CG)............................................................................................47

4.1.3 Screen Configuration....................................................................................................50

4.1.4 Cursor...........................................................................................................................61

4.1.5 Relationship between Display Memory and Screens...................................................62

4.1.6 Determining Various Parameters..................................................................................64

4.1.7 Scrolling........................................................................................................................65

4.1.8 Attribute Display using the Layered Function...............................................................68

4.2 Oscillator Circuit.........................................................................................................................70

4.3 Example of Initial Settings..........................................................................................................71

4.4 Character Codes and Character Fonts......................................................................................81

4.4.1 Character Fonts (Internal CG)......................................................................................81

4.4.2 Character Codes..........................................................................................................82

5 Specifications.....................................................................................................................83

5.1 Absolute Maximum Ratings.......................................................................................................83

5.2 Recommended Operating Conditions........................................................................................83

5.3 Electrical Characteristics ...........................................................................................................84

5.4 Timing Characteristics ...............................................................................................................86

5.4.1 System Bus (Generic Bus/80-series MPU)..................................................................86

5.4.2 System Bus Read/write characteristics II (MC68K-series MPU)..................................89

5.4.3 External Clock Input Characteristics ............................................................................92

5.4.4 LCD Control SignalTiming Characteristics..................................................................93

6 MPU Interface.....................................................................................................................95

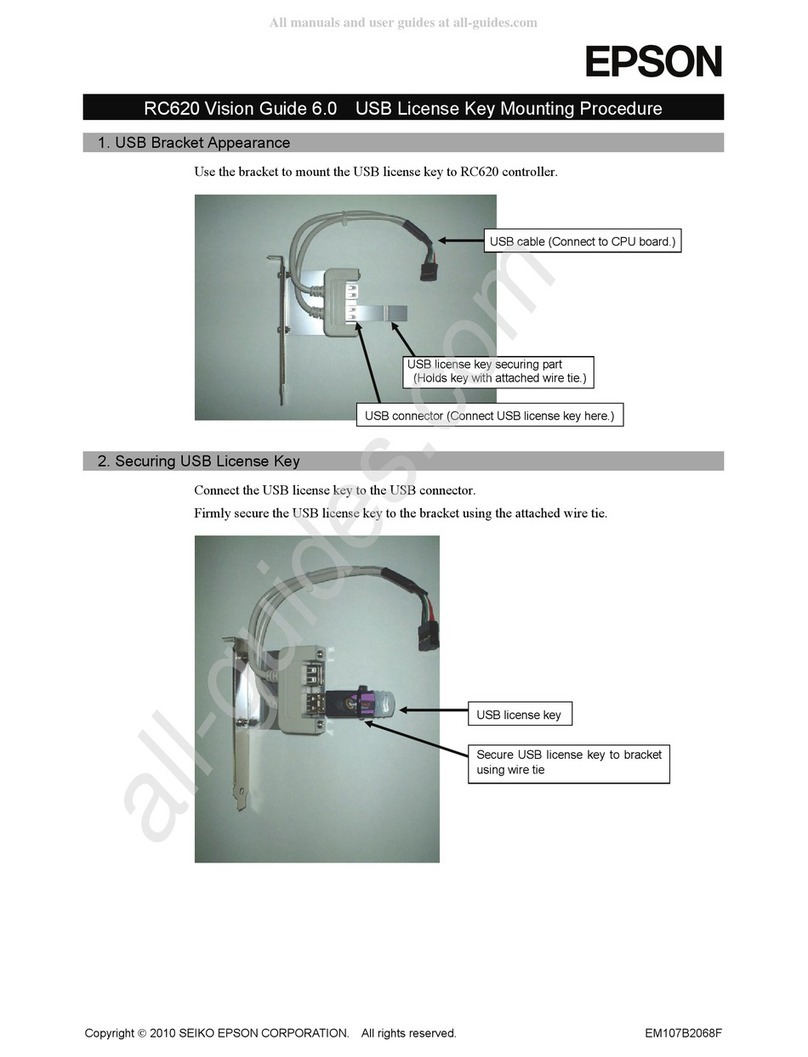

6.1 Connection to the System Bus...................................................................................................95

6.1.1 80-series MPU..............................................................................................................95

6.1.2 68-series MPU..............................................................................................................95

6.2 Interfaces with the MPU (Reference).........................................................................................96