SPC7281F0A

– i –

Contents

1. DESCRIPTION .................................................................................................................................................. 1

2. FEATURES........................................................................................................................................................ 1

3. INTERNAL BLOCK DESCRIPTION .................................................................................................................. 3

3.1 BLOCK DIAGRAM ..................................................................................................................................... 3

3.2 BLOCK DIAGRAM DESCRIPTION............................................................................................................ 3

4. INTERNAL CONNECTION DIAGRAM .............................................................................................................. 4

5. PIN ASSIGNMENT DIAGRAM .......................................................................................................................... 5

6. PIN DESCRIPTION ........................................................................................................................................... 6

7. FUNCTIONAL DESCRIPTION ........................................................................................................................ 10

7.1 MEMORY MAP ........................................................................................................................................ 10

7.1.1 All Memory Space.......................................................................................................................... 10

7.1.2 IEEE1394LINK/Transaction Controller xCSBUF Area (SRAM)..................................................... 11

7.2 IEEE1394 PACKET FORMAT ................................................................................................................. 12

7.2.1 Transmit Packet Format ................................................................................................................ 12

7.2.2 Receive Packet Format.................................................................................................................. 14

7.3 IEEE1394 HARDWARE SBP-2 CONTROL ............................................................................................. 17

7.4 IDE INTERFACE CONTROL ................................................................................................................... 17

7.5 BUILT-IN CPU.......................................................................................................................................... 17

7.6 FLASH CONTROLLER ............................................................................................................................ 18

8. INTERNAL REGISTER.................................................................................................................................... 19

8.1 IEEE1394 LINK CONTROLLER REGISTER MAPPING ......................................................................... 19

8.1.1 Register Table ............................................................................................................................... 19

8.1.2 Register/Bit Table .......................................................................................................................... 22

8.1.3 Register Map ................................................................................................................................. 26

8.1.4 Detail Description of Register ........................................................................................................ 42

8.2 FLASH ROM CONTROL REGISTER ...................................................................................................... 88

9. ELECTRICAL CHARACTERISTICS................................................................................................................ 91

9.1 ABSOLUTE MAXIMUM RATINGS........................................................................................................... 91

9.2 RECOMMENDED OPERATING CONDITION ......................................................................................... 91

9.3 DC CHARACTERISTICS (ACCORDING TO RECOMMENDED OPERATING CONDITION) ................ 92

9.4 AC CHARACTERISTICS ......................................................................................................................... 94

9.4.1 Clock Timing .................................................................................................................................. 94

9.4.2 PHY-LINK Interface Timing ........................................................................................................... 95

9.4.3 IDE Interface Timing...................................................................................................................... 96

9.4.4 CPU Interface Timing .................................................................................................................. 104

10. EXAMPLES OF EXTERNAL CONNECTION FOR REFERENCE PURPOSES ........................................... 105

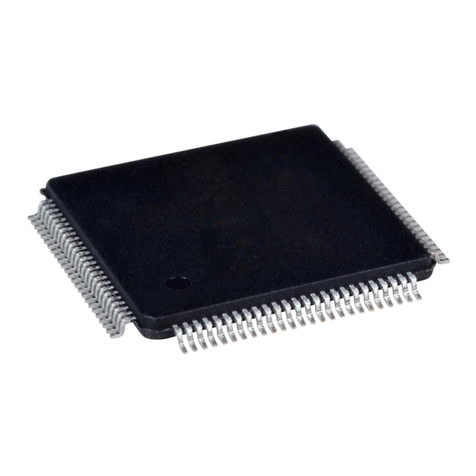

11. SHAPE OF PACKAGE .................................................................................................................................. 108