Epson S1R72V17 Instruction Manual

Other Epson Controllers manuals

Epson

Epson S1R75801F00A User manual

Epson

Epson S5U1C17564T2 User manual

Epson

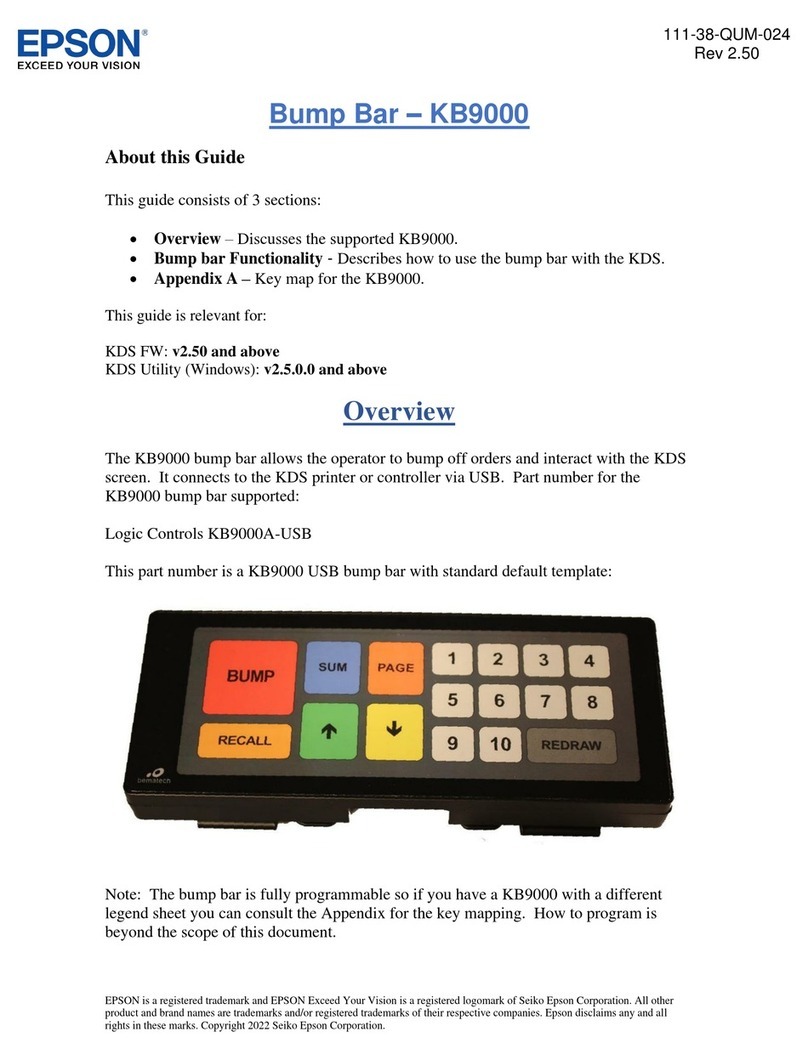

Epson KB9000 User manual

Epson

Epson S1D13700 User manual

Epson

Epson S1D13706 User manual

Epson

Epson S2R72A11 Installation and operating instructions

Epson

Epson BO-IC400 User manual

Epson

Epson S1R72105 User manual

Epson

Epson S1D13504 User manual

Epson

Epson RC700 User manual

Epson

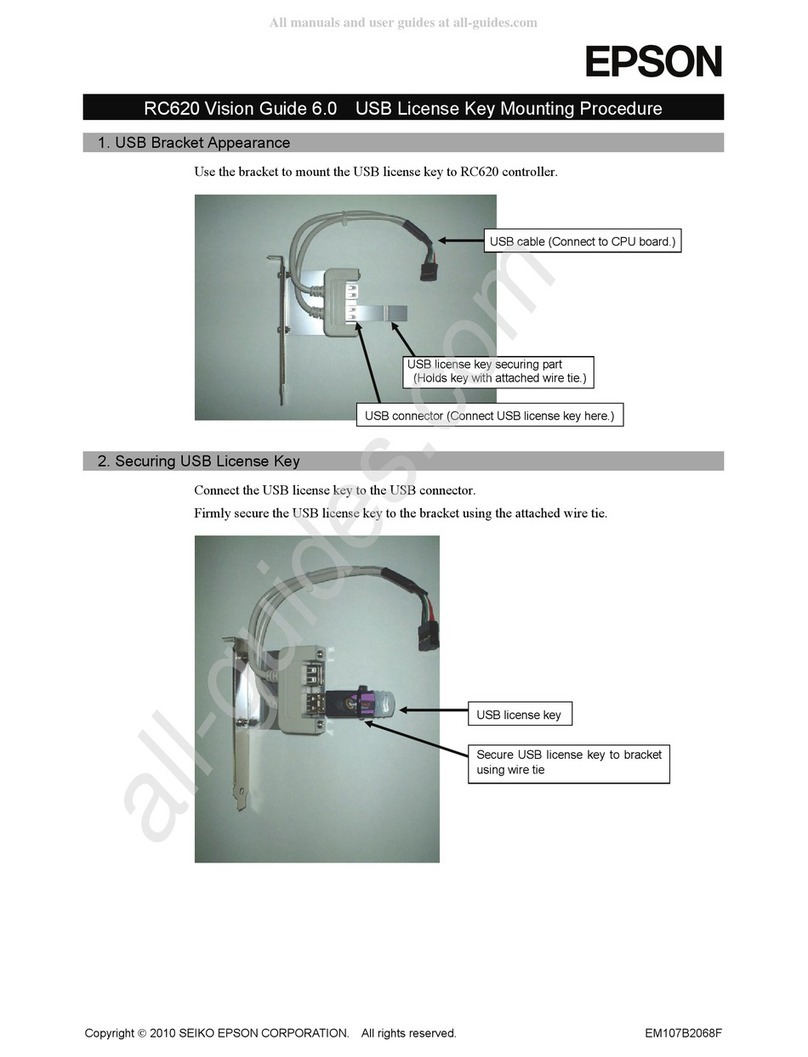

Epson RC620 CU User manual

Epson

Epson S1D13505F00A User manual

Epson

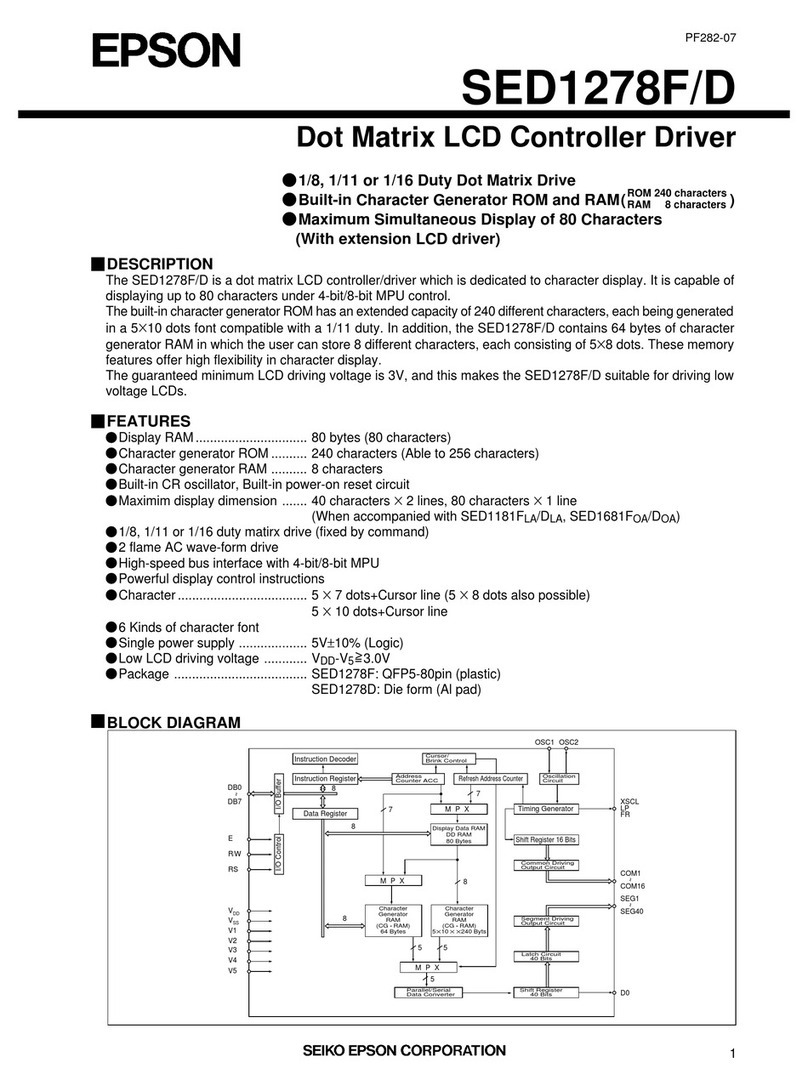

Epson SED1278F/D User manual

Epson

Epson S1D13504 User manual

Epson

Epson S1D13704 User manual

Epson

Epson RC180 User manual

Epson

Epson S1R72104 User manual

Epson

Epson RC620 Series User manual

Epson

Epson RC700 User manual

Epson

Epson S2R72V18 User manual

Popular Controllers manuals by other brands

Digiplex

Digiplex DGP-848 Programming guide

YASKAWA

YASKAWA SGM series user manual

Sinope

Sinope Calypso RM3500ZB installation guide

Isimet

Isimet DLA Series Style 2 Installation, Operations, Start-up and Maintenance Instructions

LSIS

LSIS sv-ip5a user manual

Airflow

Airflow Uno hab Installation and operating instructions