MODEL SDP100 VERSION V_1.00

PREPARED BY H/W DATE 25/05/2007

SUBJECT TECHNICAL MANUAL PAGE 4/70

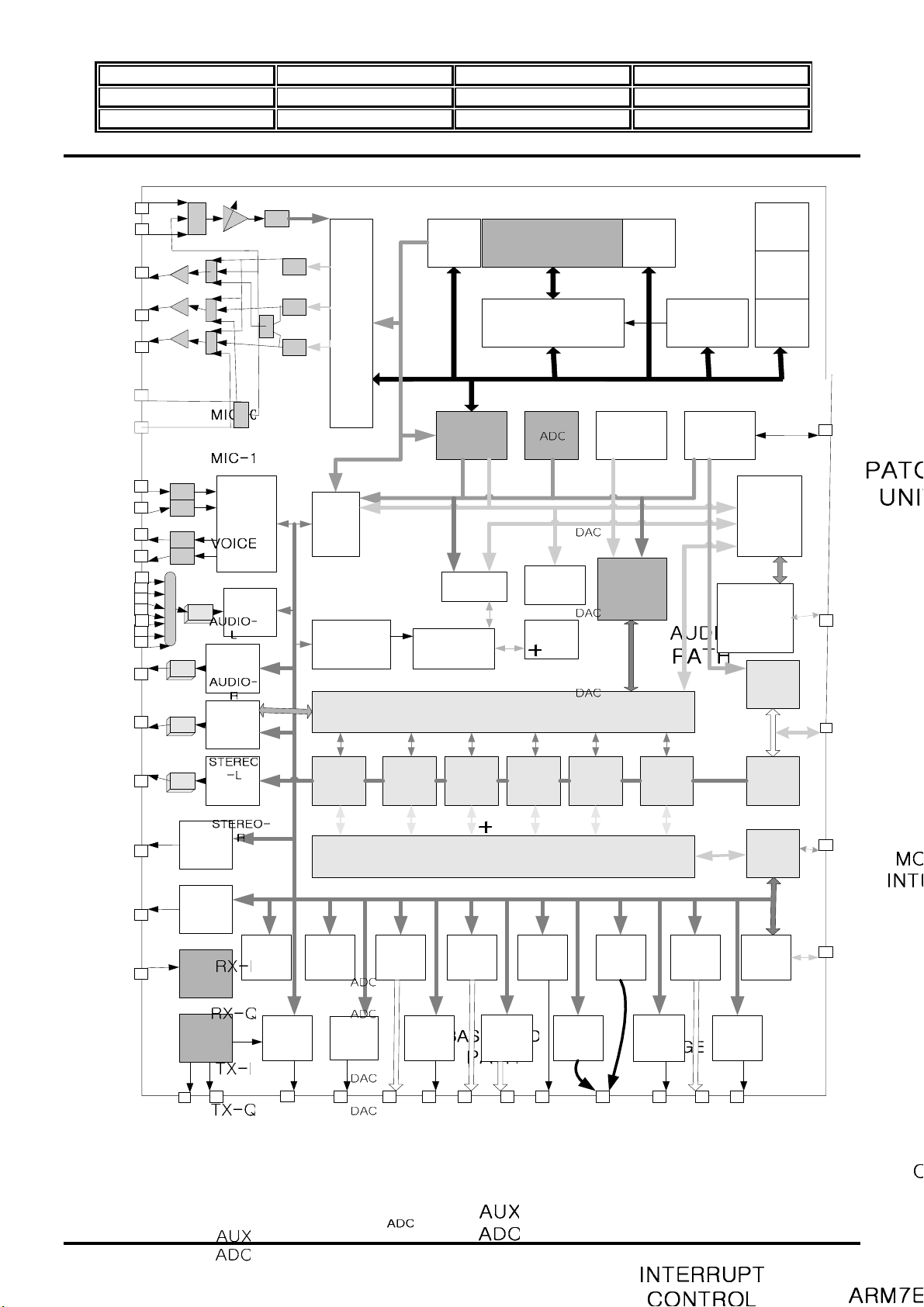

-.Two programmable acoustic compensation filters.

-. GSM/GPRS quad vocoders for adaptive multirate(AMR), enhanced full rate(EFR), full rate(FR) and half rate(HR).

-. GSM channel coding, equalization and A5/1 and A5/2 ciphering.

-.GPRS GEA1 and GEA2 ciphering.

-. Programmable GSM/GPRS model.

-. Packet Switched data with CS1/CS2/CS3/CS4 coding schemes.

-.GSM circuit switch data.

-. GPRS Class 12.

zVoice Interface and Voice Front End.

-. Two microphone inputs sharing one low noise amplifier with programmable gain and automatic gain control(AGC)

mechanisms.

-. Voice power amplifier with programmable gain.

-. 2’nd order Sigma-Delta A/D converter for voice uplink path.

-. D/A Converter for Voice downlink path.

-. Supports Half-duplex hands-free operation.

-. Compliant with GSM 03.50.

1.3 Multimedia Feature

zLCD/NAND Flash Interface

-. Dedicated Parallel Interface supports 3 external devices with 8/16 bits NAND flash interface, 8/9/16/18 bit Parallel

interface and serial interface for LCM.

-. Built-in NAND flash controller with 1 bit ECC for mass storage.

zLCD Controller

-. Supports simultaneous connection to up to 3 parallel LCD and 2 serial LCD modules.

-. Supports LCM format : RGB332, RGB444, RGB565, RGB666, RGB888.

-. Supports LCD Module with maximum resolution up to 800x600 at 24bpp.

-. Per pixel alpha channel.

-. True colour engine

-. Supports hardware display rotation.

-. Capable of combining display memories with up to 6 blending layers.

zImage Signal Processor

-. 8/10 bit Bayer format image input.

-. YUV422 format image input.

-. Capable of processing image of size up to 3M pixels.

-. Colour correction matrix.

-. Gamma correction.

-. Automatic exposure(AE) control.

-. Automatic focus control.

-. Automatic white balance(AWB) control.

-. Programmable AE/AEB windows.

SDP100 TECHNICAL MANUAL Page 3.4