Figure 5-21. PLC Verifying Jumpers J16 through J20...........................................................5-41

Figure 5-22. PLC Verifying Jumpers J21 through J25...........................................................5-42

Figure 5-23. PLC Jumper Settings, Transmit Carrier Frequency Range................................5-43

Figure 5-24. PLC Analog Module, Carrier Level Indicator Modes - Jumpers.......................5-46

Figure 5-25. Location of Potentiometers on Digital PLC Module .........................................5-47

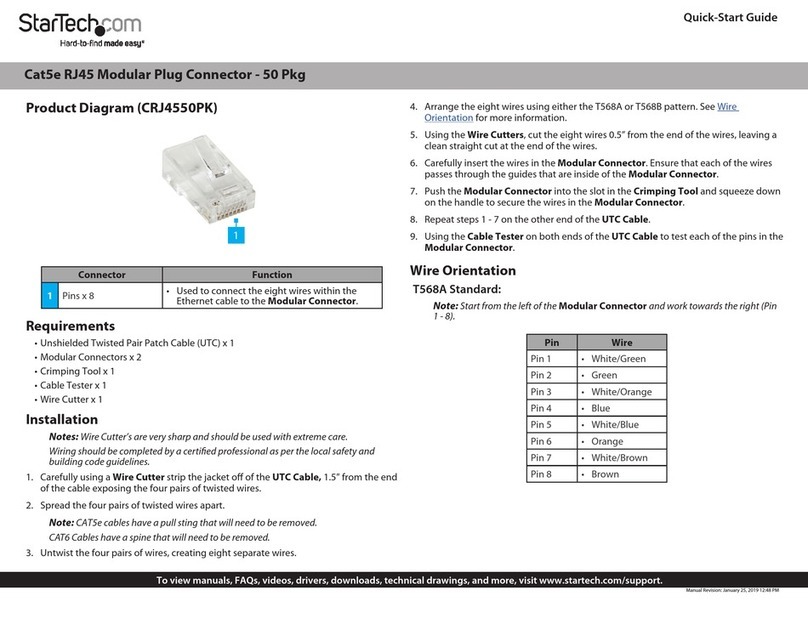

Figure 5-26. J6 Pin Numbers..................................................................................................5-48

Figure 5-27. 9508 RF Chassis Mounted on the HPS/RFL GARD Pro System......................5-49

Figure 5-28. Front View of the 9508 RF Chassis —Module Locations in 50W System......5-50

Figure 5-29. 9508 RF Chassis Block Diagram.......................................................................5-51

Figure 5-30. 9508 RF Chassis Power Amplifier.....................................................................5-52

Figure 5-31. Additional 50W Module in 100W Systems .......................................................5-53

Figure 5-32. Location of 50W Power Amplifier Module.......................................................5-53

Figure 5-33. 50W Power Amp Circuit Board.........................................................................5-54

Figure 5-34. Power Amplifier, Power Supply........................................................................5-56

Figure 5-35. Power Amplifier, Power Supply, Block Diagram..............................................5-57

Figure 5-36. TX Filter, Top View...........................................................................................5-58

Figure 5-37. Location of Jumpers on the TX Filter, PC Board 107828-2..............................5-59

Figure 5-38. Location of Jumpers on the TX Filter, PC Board 107828-1..............................5-61

Figure 5-39. Balance Board....................................................................................................5-62

Figure 5-40. Location of Jumpers on the Balance Board .......................................................5-63

Figure 5-41. Line Board..........................................................................................................5-64

Figure 5-42. RFL9508 Line Board, Block Diagram...............................................................5-64

Figure 5-43. Location of Jumpers on the Line board..............................................................5-66

Figure 5-44. Location of Jumpers on the RX Filter board......................................................5-67

Figure 5-45. Location of Jumpers on the RX Filter board, Showing Jumper Groupings.......5-68

Figure 5-46. 9508 Attenuator Board.......................................................................................5-69

Figure 5-47. 9508 Mother Board, Rear View.........................................................................5-70

Figure 5-48. Rear Panel Wiring of a typical HPS/RFL GARD Pro system PLC with a 50W 9508

RF Chassis. ..............................................................................................................................5-73

Figure 5-49. Rear Panel Wiring of a typical HPS/RFL GARD Pro system PLC with a 100W

9508 RF Chassis. .....................................................................................................................5-74

Figure 5-50. Optional Power Supply I/O Module, Single On/Off Switch..............................5-75

Figure 5-51. Switched Battery Output, Functional Diagram..................................................5-76

Figure 5-52. Making Connections to a Second PLC Module.................................................5-77

Figure 5-53. Setting Jumpers on Second PLC Analog Module..............................................5-78

Figure 6-1. Permissive Underreaching Transfer Trip................................................................6-2

Figure 6-2. Permissive Overreaching Transfer Trip..................................................................6-2

Figure 6-3. Direct Transfer Trip ................................................................................................6-3

Figure 6-4. Directional Comparison Blocking...........................................................................6-4

Figure 6-5. Directional Comparison Unblocking ......................................................................6-5

Figure 6-6. Digital Teleprotection Configuration –General Tab..............................................6-7

Figure 6-7. Digital Teleprotection Timeslot Configuration screen ...........................................6-9

Figure 6-8. Teleprotection Service Comms Bus allocation.....................................................6-10

Figure 6-9. Teleprotection Service Comms Bus Configuration ..............................................6-10

Figure 6-10. Digital Comms Configuration fields...................................................................6-15

Figure 6-11. Digital Teleprotection Configuration Example...................................................6-16

Figure 6-12. TPS configuration –Advanced Tab....................................................................6-17

Figure 6-13. TPS Status –Channel Tab...................................................................................6-19