IDT 8A 72QFN Series User manual

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

1

February 14, 2019

Description

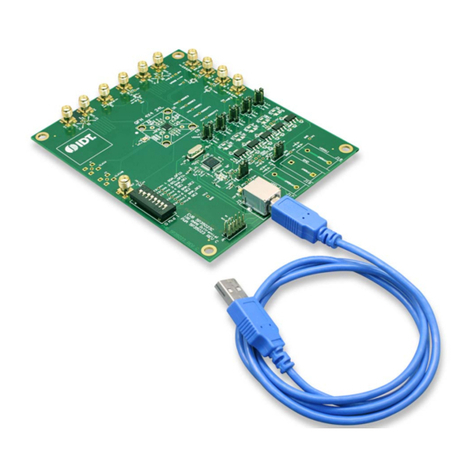

The 8Axxxx 72QFN EVK is designed to help customers evaluate

IDT ClockMatrix devices. This document discusses the following

about the EVK:

Introduces the board and its power supply and jumper settings

Describes the input and output connectors for normal

operation

Explains how to bring up the board using the Timing

Commander software GUI

Discusses how to configure and program the board to

generate standard-compliant frequencies

Kit Contents

8A34xxx 72QFN Evaluation Board

USB Type A cable

Requirements

IDT Timing Commander Software Installed (available at

www.idt.com/timingcommander)

ClockMatrix GUI (available at www.idt.com/clockmatrix)

USB 2.0 or USB 3.0 interface

Windows XP SP3 or later

Processor: Minimum 1GHz

Memory: Minimum 512MB; recommended 1GB

Available disk space: Minimum 600MB (1.5GB 64-bit);

recommended 1GB (2GB 64-bit)

Network access during installation if the .NET framework is

not currently installed on the system

8A3xxxx 72QFN EVK Board

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

2

February 14, 2019

Important Notes

Disclaimer

Integrated Device Technology, Inc. and its affiliated companies (herein referred to as “IDT”) shall not be liable for any damages arising out of defects resulting from

(i) delivered hardware or software

(ii) non-observance of instructions contained in this manual and in any other documentation provided to user, or

(iii) misuse, abuse, use under abnormal conditions, or alteration by anyone other than IDT.

TO THE EXTENT PERMITTED BY LAW, IDT HEREBY EXPRESSLY DISCLAIMS AND USER EXPRESSLY WAIVES ANY AND ALL WARRANTIES, WHETHER

EXPRESS, IMPLIED, OR STATUTORY, INCLUDING, WITHOUT LIMITATION, IMPLIED WARRANTIES OF MERCHANTABILITY AND OF FITNESS FOR A

PARTICULAR PURPOSE, STATUTORY WARRANTY OF NON-INFRINGEMENT, AND ANY OTHER WARRANTY THAT MAY ARISE BY REASON OF USAGE

OF TRADE, CUSTOM, OR COURSE OF DEALING.

Important Equipment Warning: Ensure the correct connection of all cables. Supplying the board using the wrong

polarity could result in damage to the board and/or the equipment. Check that all jumpers have been removed from

the board before applying power.

Contents

1. Usage Guide.................................................................................................................................................................................................4

1.1 Board Overview...................................................................................................................................................................................4

1.2 Board Power Supply............................................................................................................................................................................5

1.3 Voltage Selection Jumpers..................................................................................................................................................................5

1.4 GPIO Switches, LEDs, and Test Points ..............................................................................................................................................6

1.5 USB Jack.............................................................................................................................................................................................7

1.6 I2C between FTDI, CM Device, and Onboard EEPROM .....................................................................................................................7

2. Working with Timing Commander™ for Programing/Configuration..............................................................................................................8

2.1 Default Operation ................................................................................................................................................................................8

2.2 Using Timing Commander to Control the Board..................................................................................................................................9

2.3 Output Terminations and Rework to Take 1PPS Input......................................................................................................................15

3. How to Upload Firmware to the RAM .........................................................................................................................................................16

4. Schematics.................................................................................................................................................................................................18

5. Ordering Information...................................................................................................................................................................................18

6. Revision History..........................................................................................................................................................................................18

!

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

3

February 14, 2019

List of Figures

Figure 1. Overview of 72QFN ClockMatrix Evaluation Board.............................................................................................................................4

Figure 2. Example of Voltage Jumpers...............................................................................................................................................................5

Figure 3. GPIO Setting and Status Display Area................................................................................................................................................7

Figure 4. Board Setting for Default Operation ....................................................................................................................................................8

Figure 5. Starting Up Timing Commander GUI...................................................................................................................................................9

Figure 6. Selecting 8A34001 using Personality File v4.6..................................................................................................................................10

Figure 7. Timing Commander GUI with a Settings File Opened.......................................................................................................................11

Figure 8. Setting I2C for Connecting the Board with GUI..................................................................................................................................12

Figure 9. A Green Band appears when a Valid Connection is Made................................................................................................................12

Figure 10. Firmware Version Mismatch Warning Message ................................................................................................................................13

Figure 11. Reading Firmware Version ................................................................................................................................................................13

Figure 12. Read Firmware Version of ClockMatrix Chip.....................................................................................................................................14

Figure 13. AC Coupling and Terminations for Input Clock..................................................................................................................................15

Figure 14. Configuring CLK0 as CMOS to Receive a 1PPS Input......................................................................................................................15

List of Tables

Table 1. GPIO Settings......................................................................................................................................................................................6

Table 2. EEPROM I2C Connections ..................................................................................................................................................................7

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

4

February 14, 2019

1. Usage Guide

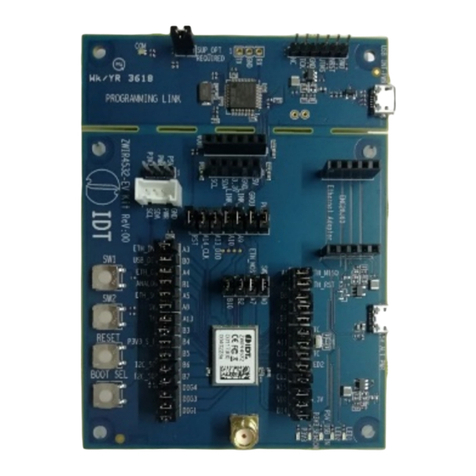

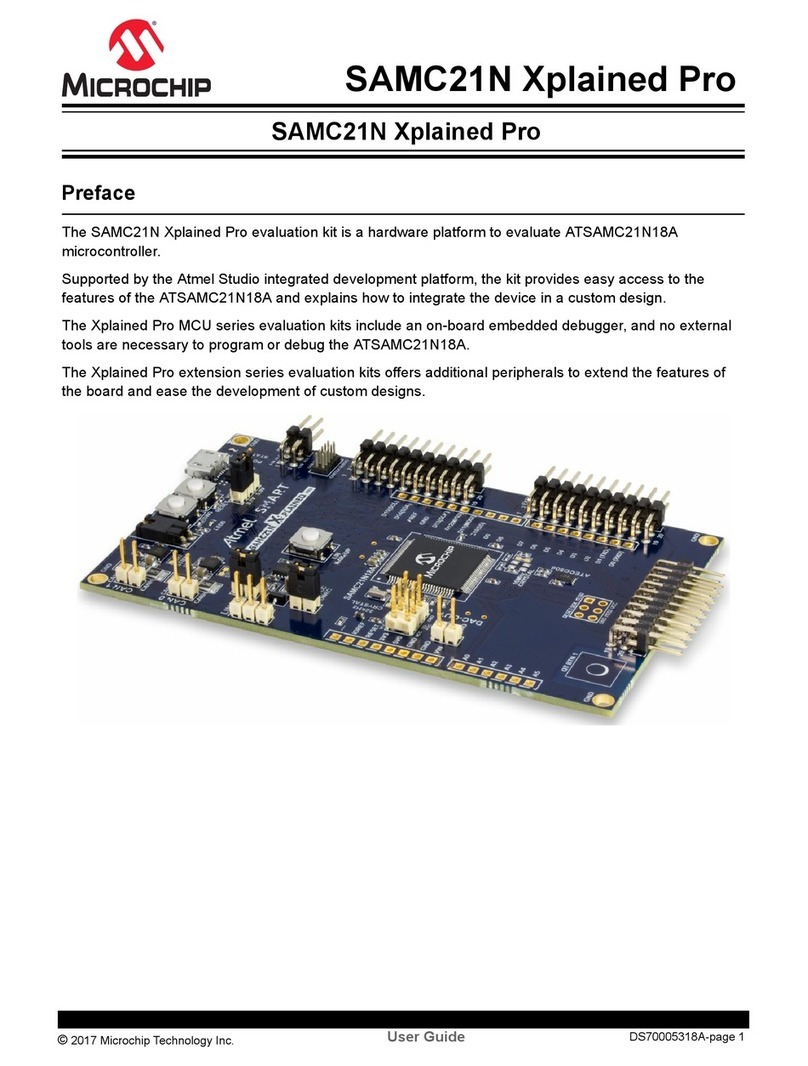

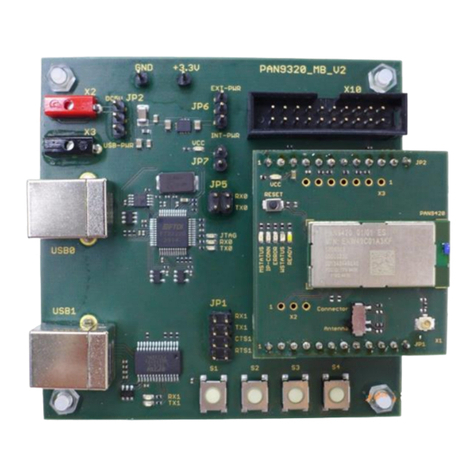

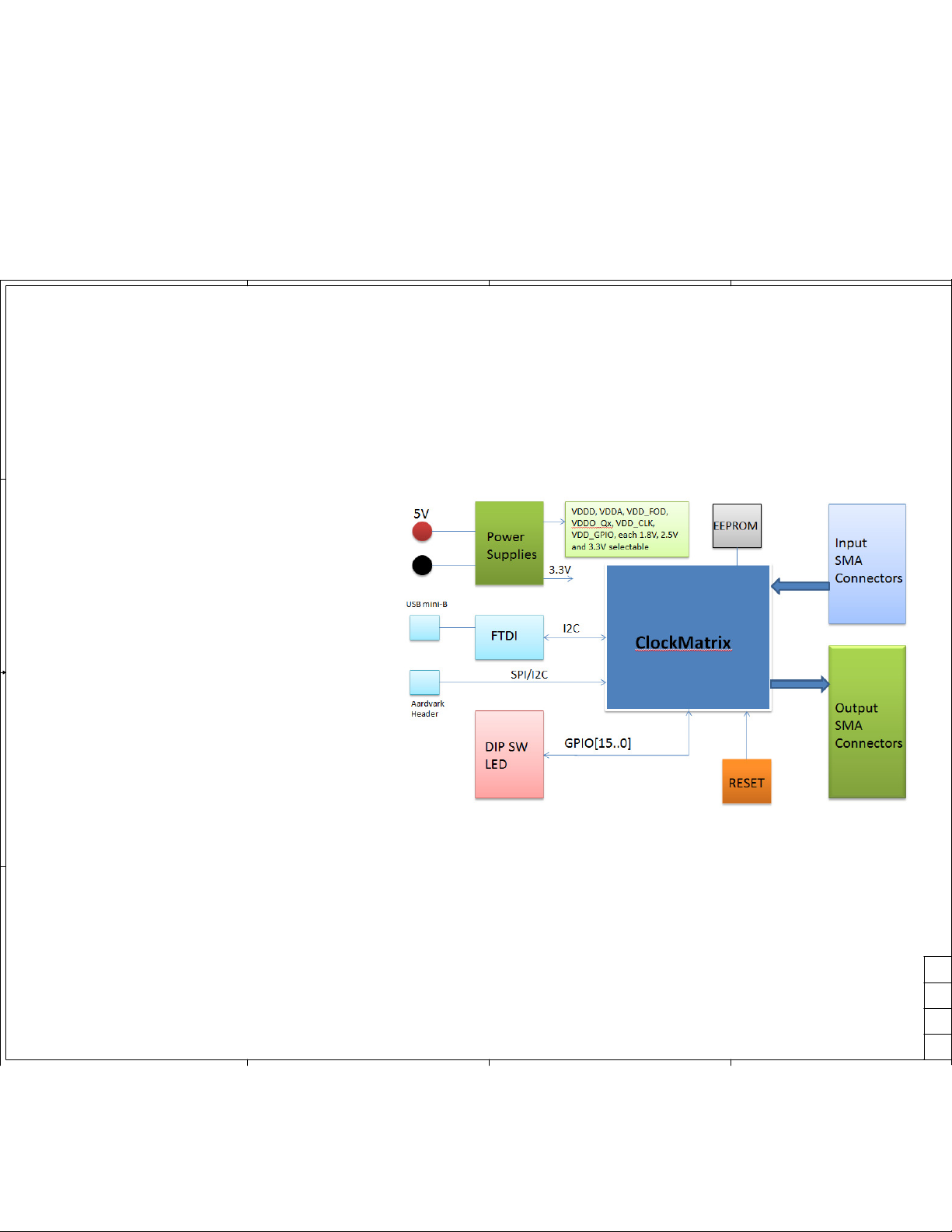

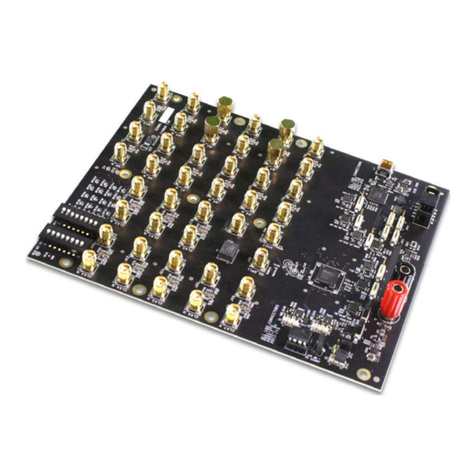

1.1 Board Overview

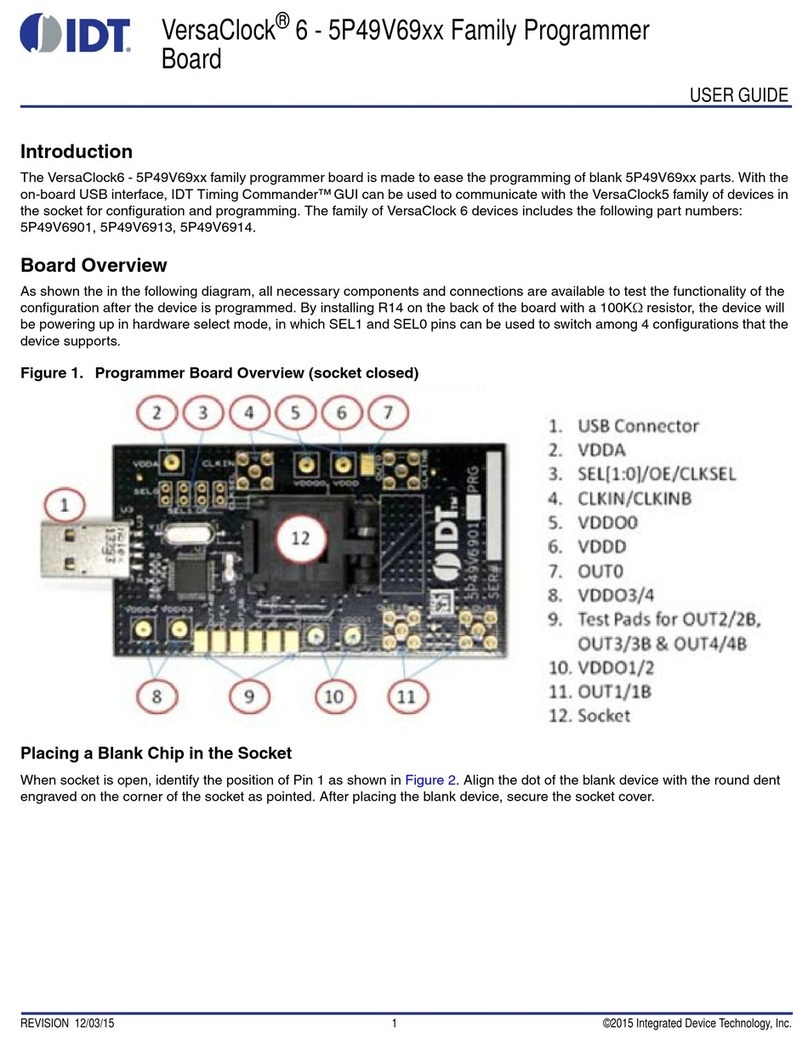

The following diagram identifies various components of the board: input and output SMA connectors, power supply jacks, and some jumper

settings necessary for the board operations.

Figure 1. Overview of 72QFN ClockMatrix Evaluation Board

Detailed descriptions of the board are as follows:

Input SMA Connectors –There are five differential inputs labeled CLK0/nCLK0–CLK4/nCLK4. Each input clock can be configured

differentially (LVDS, PECL 2.5V, and PECL 3.3V) or in single-ended format (CMOS).

Output SMA Connectors –There are 12 outputs labeled as Q0/nQ0–Q11/nQ11. Each output clock can be configured differentially (LVDS,

LVPECL, or user-defined amplitude) or in single-ended format (LVCMOS –in-phase or out-of-phase).

GPIO switch, LEDs, and test points –There are seven GPIOs available. Each GPIO can be set a “low” or “high” level (if input) or

displayed with an LED (if output). Some GPIOs are used to set the chip in a certain working condition on power-up. For more information,

see GPIO Switches, LEDs, and Test Points.

USB connector –A USB mini connector connects the evaluation board to a PC for GUI communications. No power is drawn from the USB

connector other than to power the FTDI USB chip.

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

5

February 14, 2019

VDDQx voltage selection jumpers –Each output voltage can be individually supplied with 1.8V, 2.5V, or 3.3V. These jumpers are used to

select the voltage for the output voltages.

Reset button –A small button is used to reset the board.

OSCI Input connector –An SMA connector, J45, can optionally supply a clock signal to overdrive the crystal.

Optional OCXO/TCXO Reference –An OCXO/TCXO footprint, is output at J82. It can be connected to J46 (below) as the reference for

the System DPLL.

SysDPLL Input –An SMA connector, J46, is provided to supply a local OCXO/TCXO reference as an optional reference for the System

DPLL.

Crystal –A crystal of various frequencies must be present for board operations. A 3225 footprint is provided for SMT crystals. For easy

plug-in of a canned crystal, two through holes are also available.

EEPROM –An SO-8 socket is provided to hold an EEPROM device of compatible package. An EEROM is used to store firmware and

customer configuration data, if needed.

1.2 Board Power Supply

The board uses a single +5V supply for its power supplies. When running the board, please set the bench power supply at 5V/2A. The red jack

(J1) is positive; the black jack (J2) is the ground.

Multiple LDOs are used to generate 3.3V, 2.5V, and 1.8V from the +5V supply.

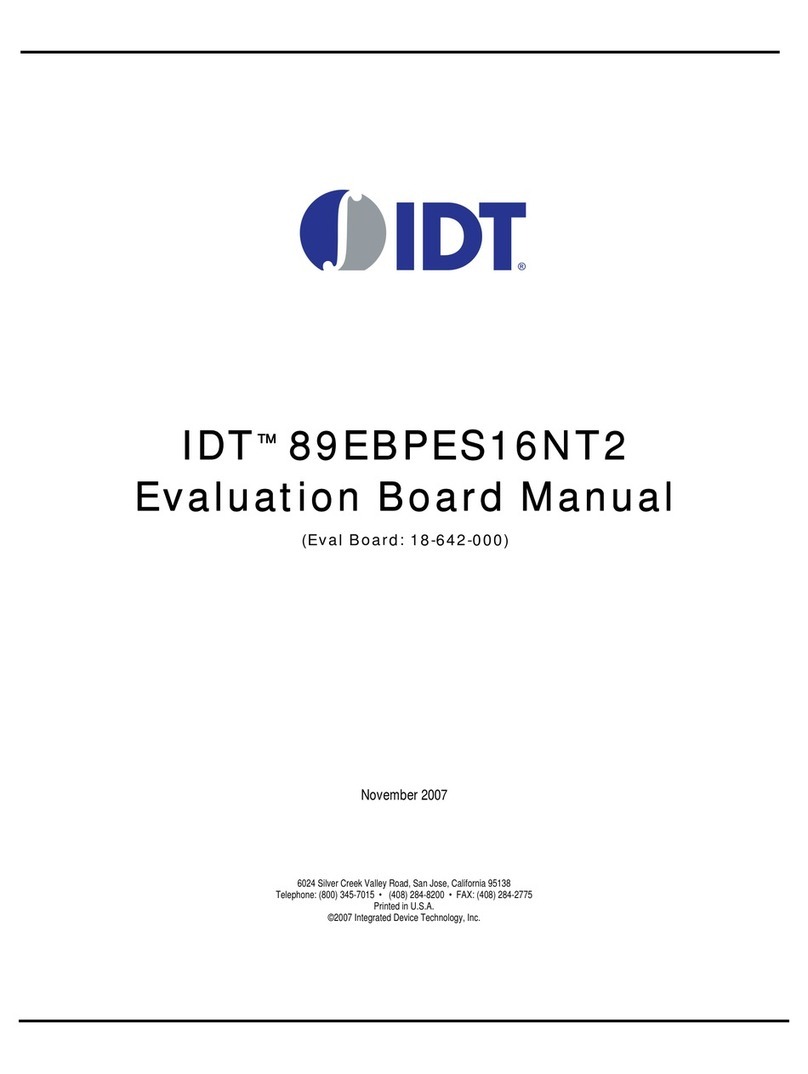

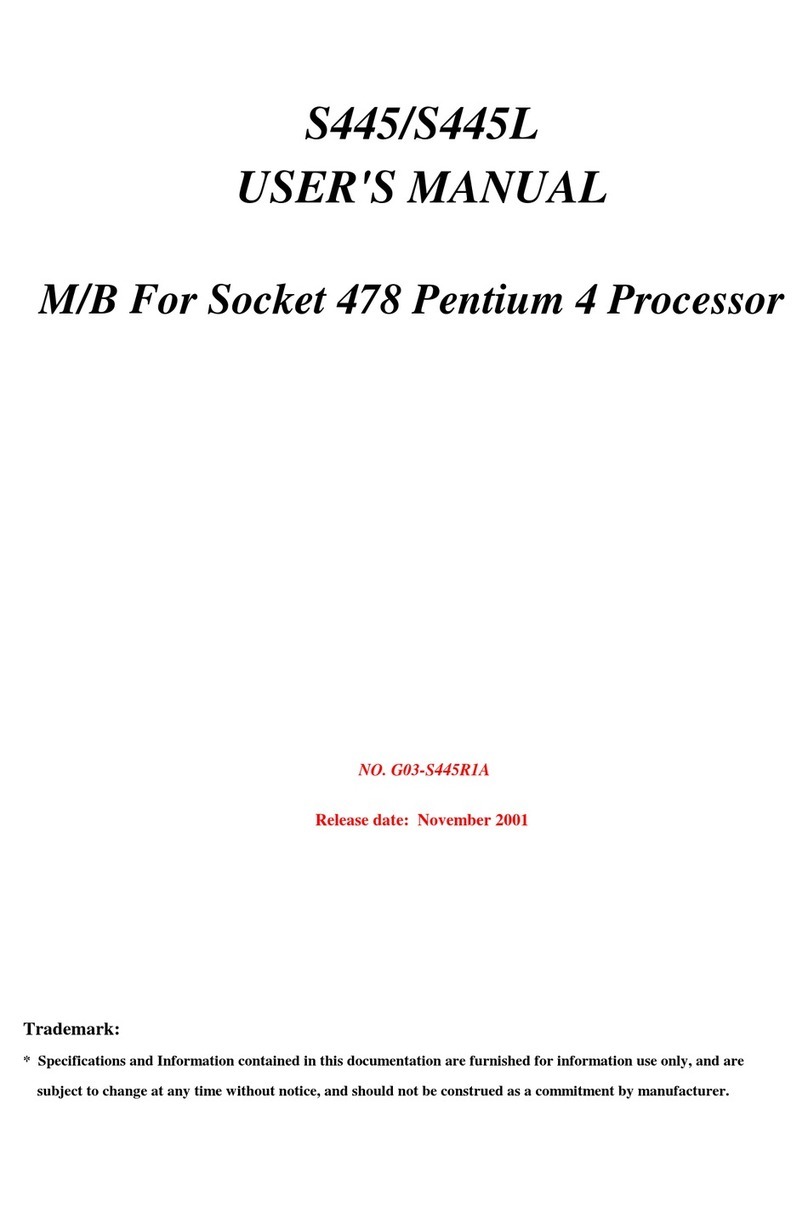

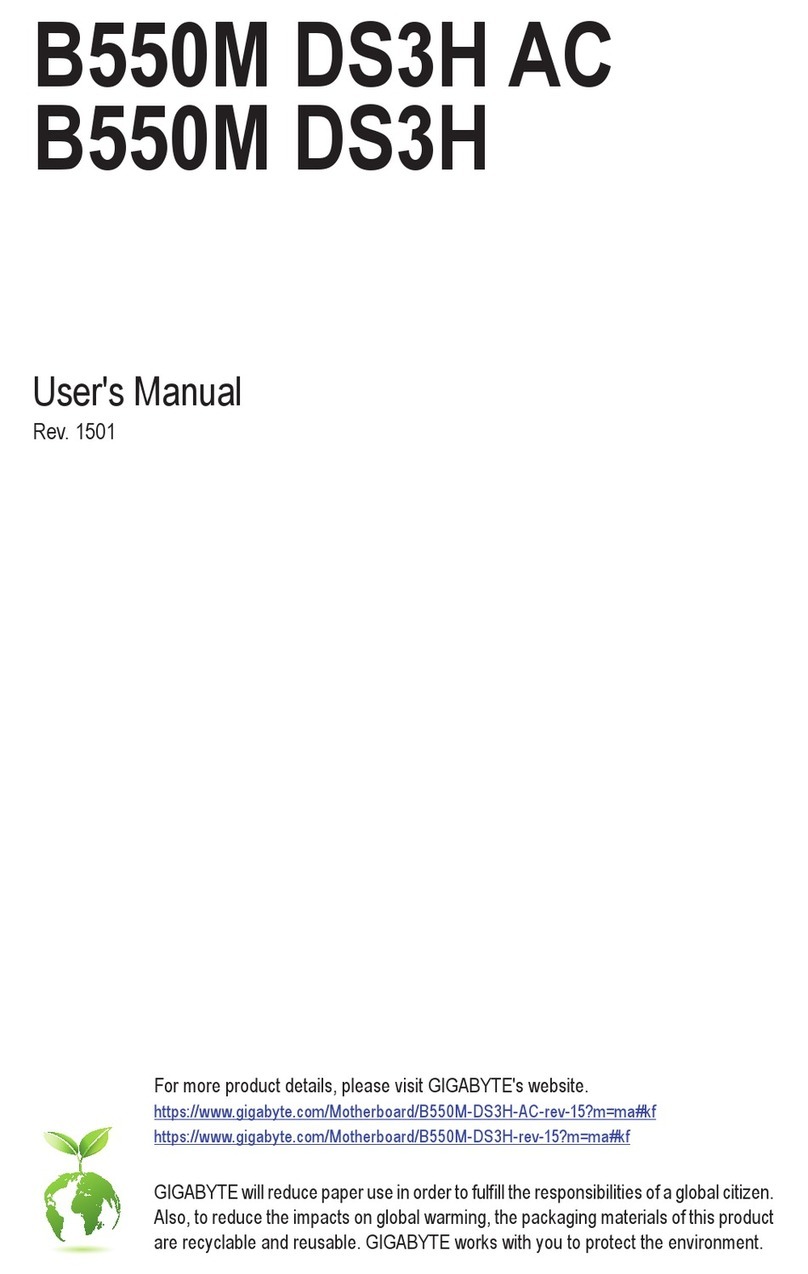

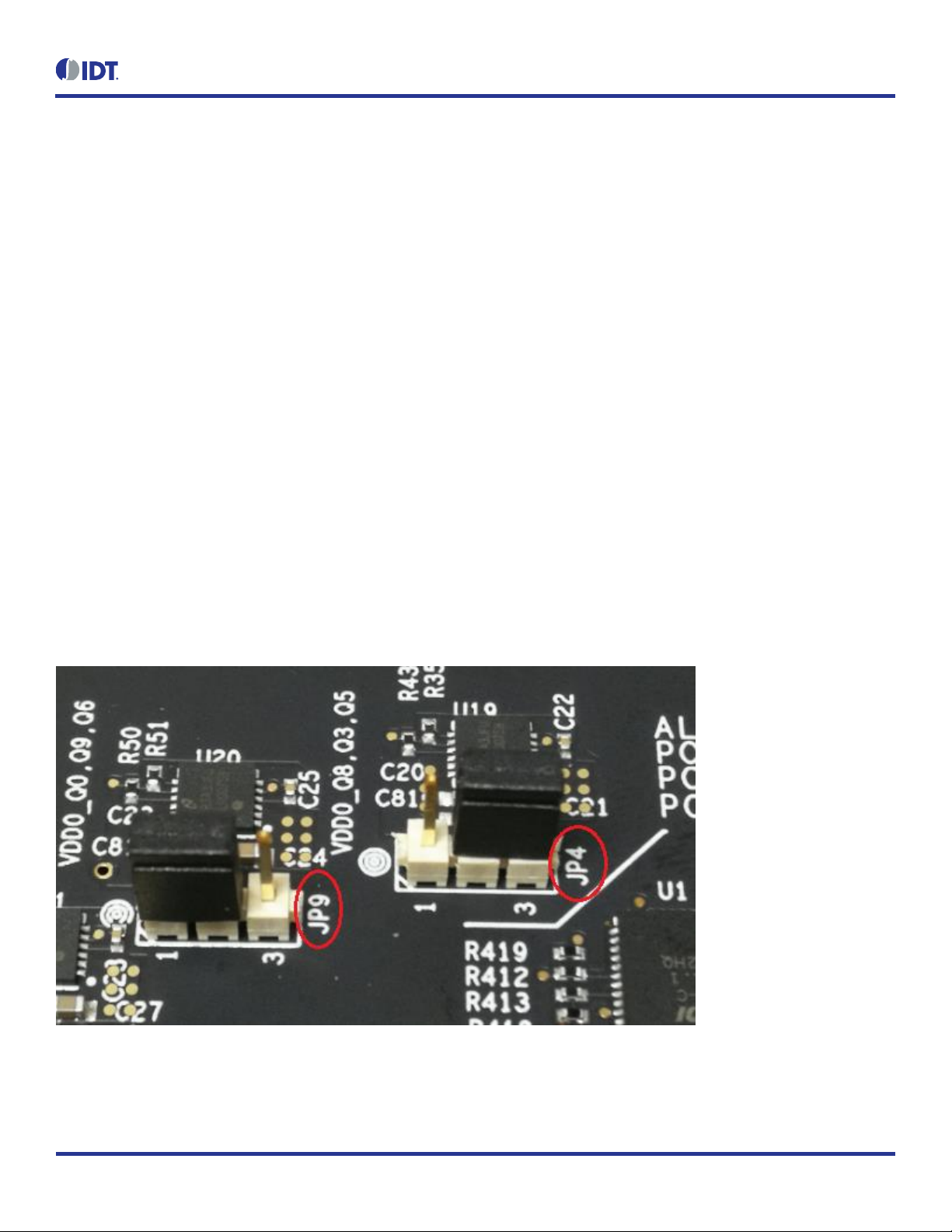

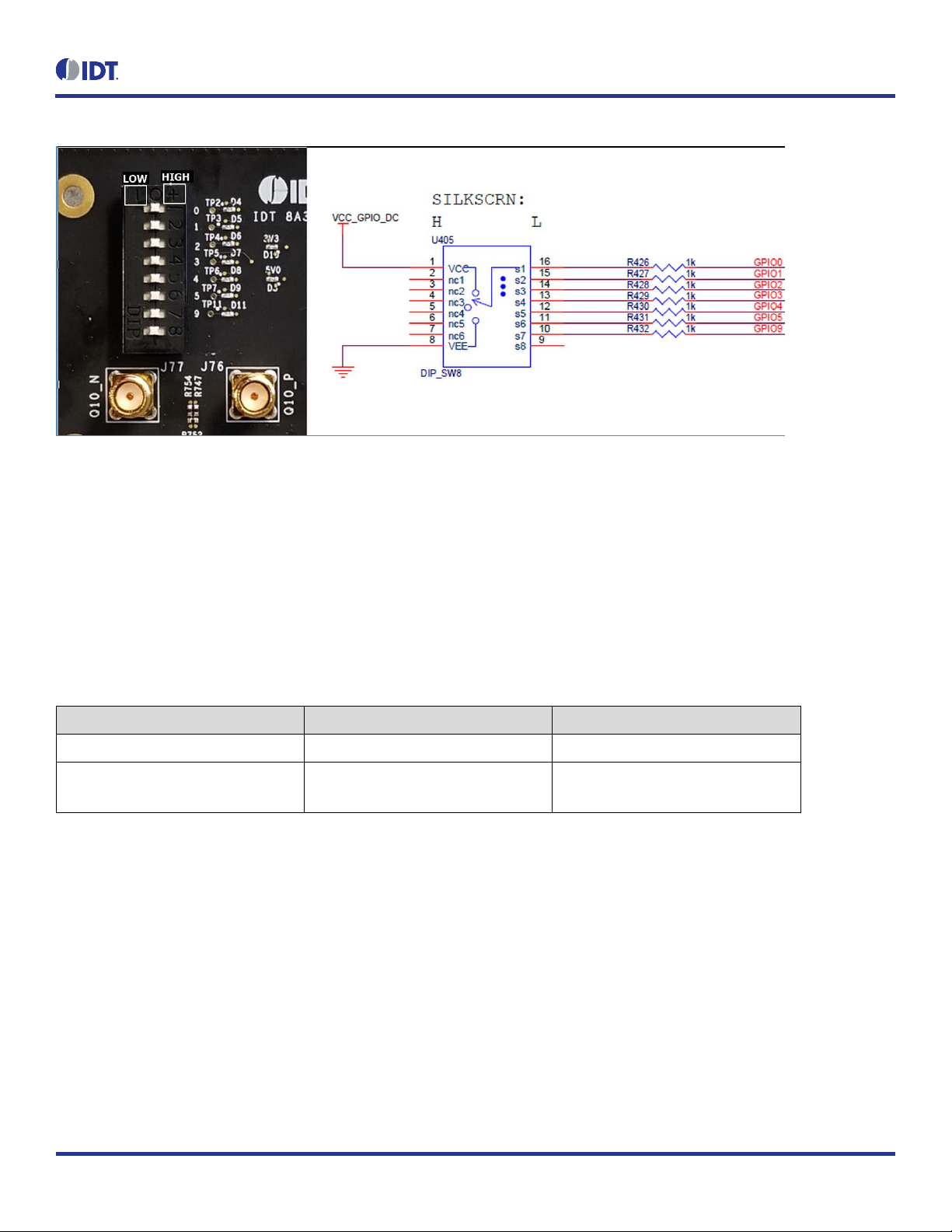

1.3 Voltage Selection Jumpers

There are eight headers/jumpers to select different voltages for different functional blocks of the chip. Each header has pin 1 and 3 labeled in

silkscreen –jumping pin 1 and pin 2 will select 3.3V; jumping pin 2 and pin 3 will select 2.5V; no jumper will have 1.8V.

Please see the following example for JP4 and JP9 –JP4 will select 2.5V; JP9 will select 3.3V.

Figure 2. Example of Voltage Jumpers

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

6

February 14, 2019

The following list shows which head/jumper is used to select what voltage:

JP1 –VDDD

JP2 –VDDA

JP3 –VCC_GPIO_DC

JP4 –VDDO_Q8_3_5

JP5 –VDDO_Q2_4_11

JP6 –VDDO_1_10_7

JP7 –VDD_CLK0

JP9 –VDDO_Q0_9_6

Important Equipment Warning: VDD_FOD voltage is selected by resistors R908 and R909. In order to prevent

damage to the device, both R908 and R909 should not be stuffed, in which case VDD_FOD = 1.8V.

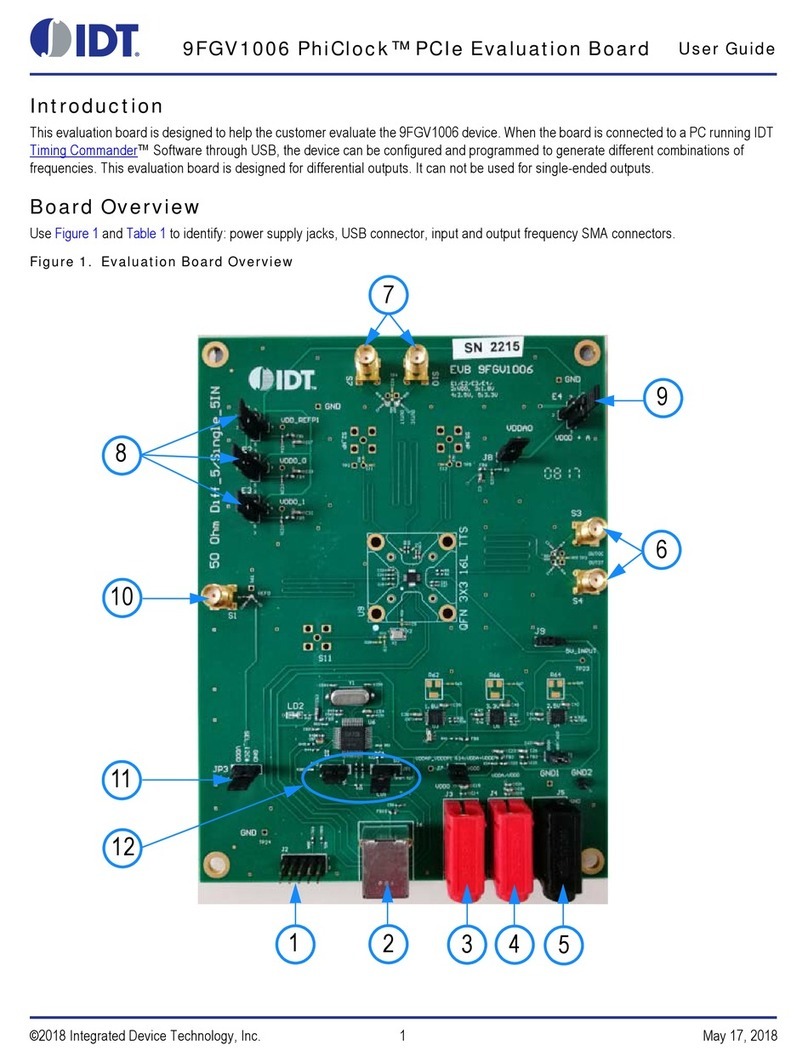

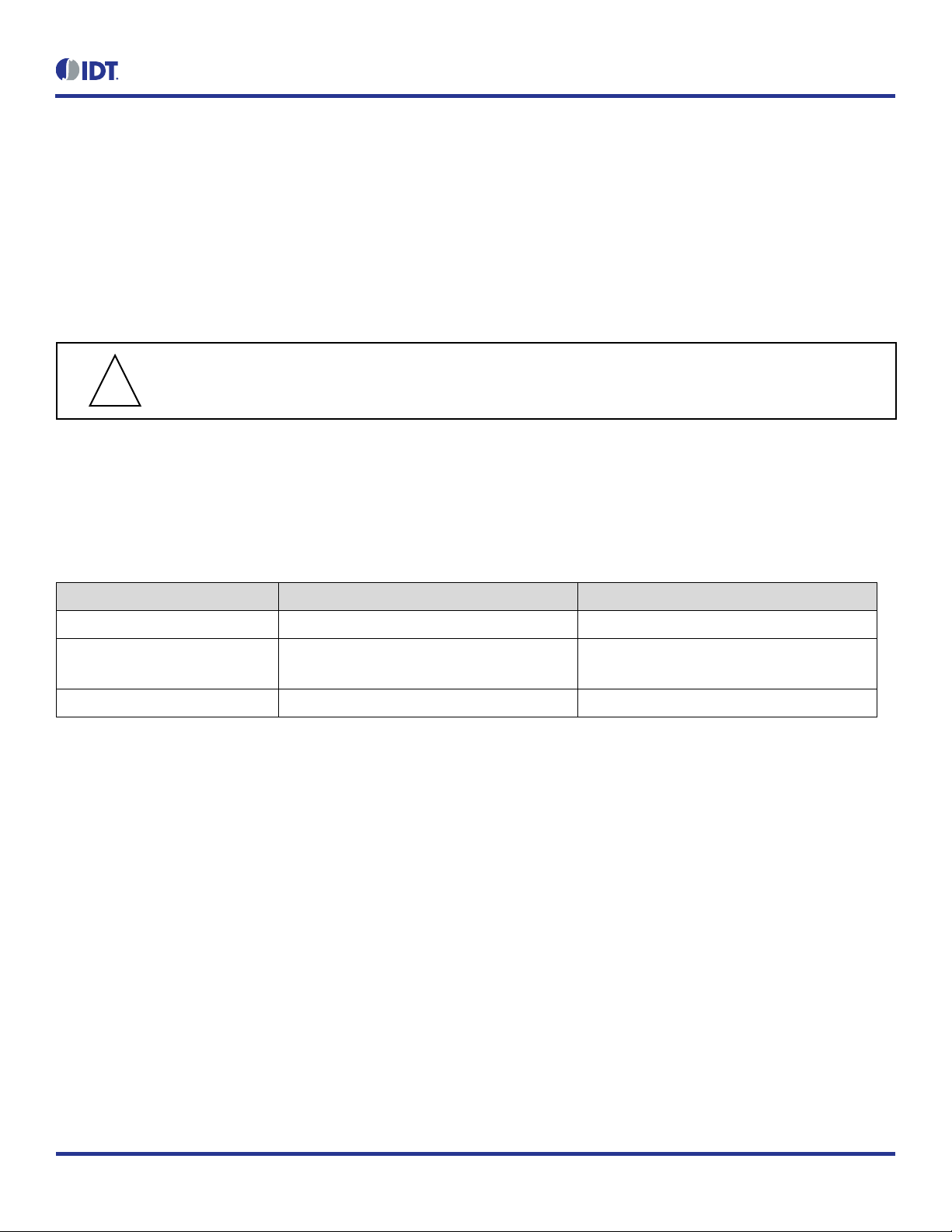

1.4 GPIO Switches, LEDs, and Test Points

An 8-bit dip switch sets the logic levels for seven GPIOs (GPIO0-5 and GPIO9). The following table shows the GPIO levels for each setting and

the corresponding LED state.

Table 1. GPIO Settings

Dip Switch Position

GPIO Logic Level

LED

Left

Low

On

Center

High if GPIO is configured as Input

High or Low according to the GPIO output setting

High if GPIO is configured as Input

High or Low according to the GPIO output setting

Right

High

Off

Please see the picture and labels in Figure 3.

When the GPIOs are configured as outputs (such as User-Controlled or LOL indicator), the dip switch for the corresponding GPIO should be

placed in the center position. The LED will indicate the state of the GPIO.

!

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

7

February 14, 2019

Figure 3. GPIO Setting and Status Display Area

1.5 USB Jack

The board has a USB mini-connector. The other end of the USB cable is a USB Type A connector going to a PC.

1.6 I2C between FTDI, CM Device, and Onboard EEPROM

One of the major differences between the 72QFN and 144BGA144 chips is that there is only one serial bus on the 72QFN chip. The I2C bus

between the FTDI chip and CM chip is the same bus between the CM chip and the onboard EEPROM. The onboard EEPROM is used to store

device firmware and/or customer’s configuration data. JP12 and JP13 must be jumped between pin 1 and 2 to enable the I2C connections.

Table 2. EEPROM I2C Connections

JP12/JP13

JP12/JP13

Jumper Position

Pin 1 and 2

Pin 2 and 3

EEPROM I2C Path

FDTI and CM Chip;

CM Chip and EEPROM

N/A

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

8

February 14, 2019

2. Working with Timing Commander™for Programing/Configuration

The following sections are best cross-referenced with the ClockMatrix GUI Step-by-Step User Guide which is available on www.idt.com.

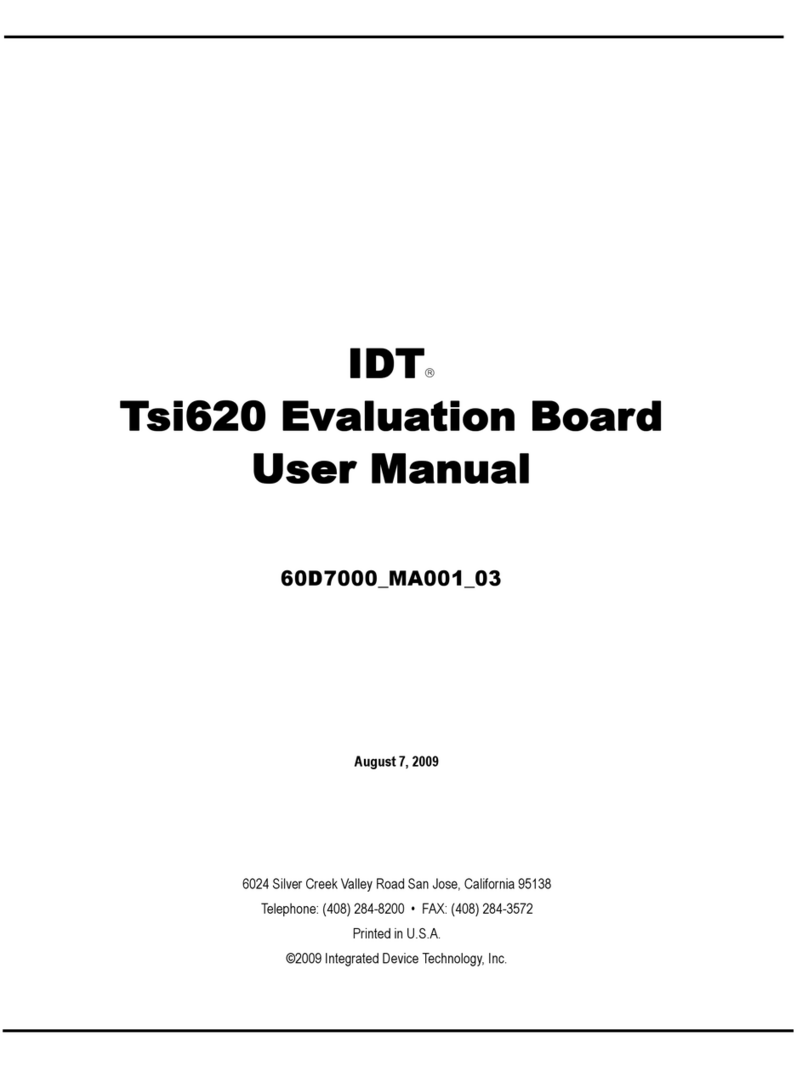

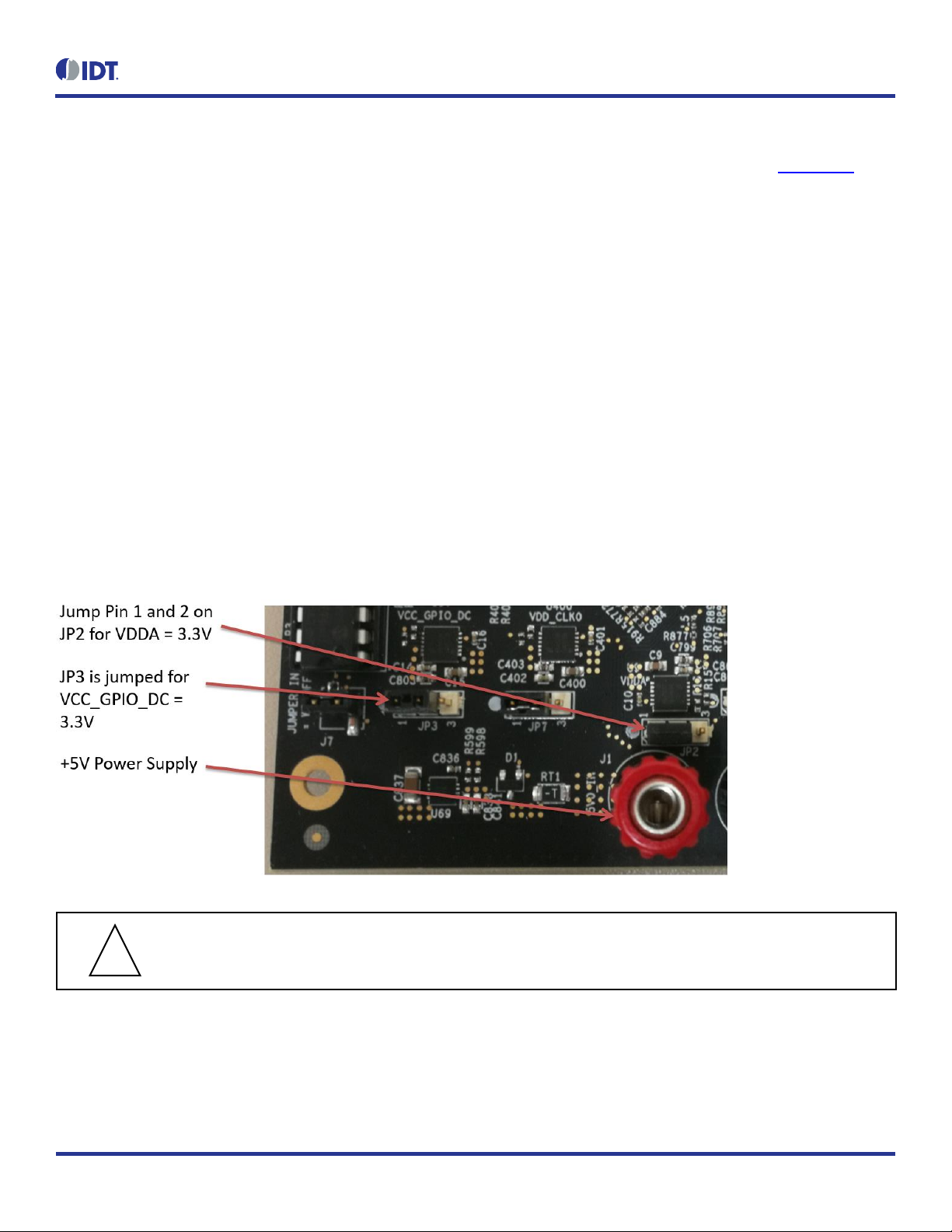

2.1 Default Operation

The board can operate off an EEPROM that has stored all information including firmware and a default configuration data. A default operation

provides a sanity check on the board before running the board through the IDT Timing Commander. Please set the board in the following default

conditions (see Figure 4 for jumper and switch positions).

Set all the GPIOs to the center position. This will ensure that GPIO9 is high and that the serial port is configured for I2C 1-byte

addressing.

VDDA = 3.3V, VDD_ FOD = 1.8V, and VDDO_Qx = 3.3V

Crystal frequency = 50MHz

CLK0 = 25MHz

FTDI, CM device, and EEPROM share the same I2C bus by jumping Pin 1 and 2 of JP12 and JP13

With the above default conditions ready, connect the board to the PC using a USB type A to USB mini cable, and power up the board using a

single +5V supply. On power-up, the ClockMatrix chip will read its firmware and configuration data from EEPROM and update all registers.

When this process is completed, the following frequencies are available:

Q0 = 122.88MHz

Q1 = 122.88MHz

Figure 4. Board Setting for Default Operation

Important Equipment Warning: In order to set GPIO9 to “High”, the switch for GPIO9 must be set either to the “+”

(high) position or the center position.

!

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

9

February 14, 2019

2.2 Using Timing Commander to Control the Board

Once the default operation is successful, complete the following steps to configure and program the ClockMatrix device per your specific

application requirements using Timing Commander GUI tools:

1. Power up the board and set the main serial port in I2C mode by GPIO9 = “high”. Connect the board to the PC.

2. Start the Timing Commander software. You will see options of “New Setting File” and “Open Setting file”. For a new configuration, select

“New Setting File”.

Figure 5. Starting Up Timing Commander GUI

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

10

February 14, 2019

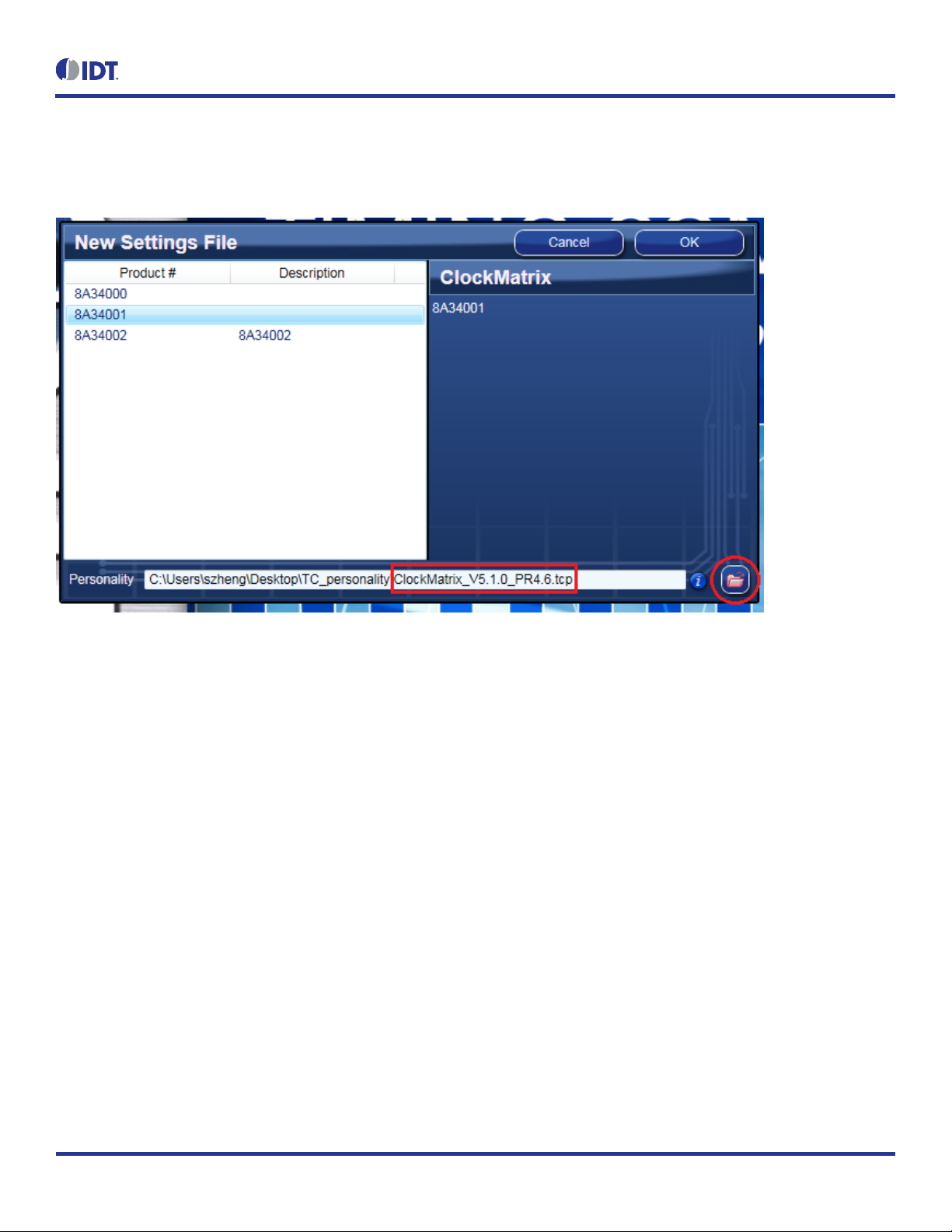

3. After selecting “New Settings File”, a device selection window will pop up. In the window, choose the intended device in the list (in this

example, 8A34001 is selected). Click the button at the lower right corner of the window (red circle) to browse and select the correct

personality file (in this example, personality v4.6 is selected). Click OK.

Figure 6. Selecting 8A34001 using Personality File v4.6

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

11

February 14, 2019

4. The GUI window with the 8A34001 block diagram will open for configurations; or if “Open Settings File” is selected in Step 3, you will be

prompted to browse and select an existing .tcs file and the personality file. When the configuration file is open, all configured values will be

displayed (see Figure 7).

Figure 7. Timing Commander GUI with a Settings File Opened

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

12

February 14, 2019

5. In order to connect the board with Timing Commander (PC), click the button (red circle) at the up-right corner of the GUI to set up the

communication protocols (see Figure 7).

After I2C and one-byte addressing are selected, click OK to close the window.

Figure 8. Setting I2C for Connecting the Board with GUI

6. Click on the chip symbol at the upper-right corner to initiate the connection. The connection is valid when a green band appears at the

upper-right corner of the window, as shown below.

Figure 9. A Green Band appears when a Valid Connection is Made

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

13

February 14, 2019

7. If ClockMatrix chip’s firmware, or firmware loaded from EEPROM, has a different version from that in the Personality file, a firmware version

mismatch warning message will appear. Click “Close” button to close the message window and a connection is made.

Figure 10. Firmware Version Mismatch Warning Message

8. Once the connection is made, the firmware version can be read within the GUI. Click the “Firmware Utility” button to bring up the Firmware

Utility window, as shown below.

Figure 11. Reading Firmware Version

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

14

February 14, 2019

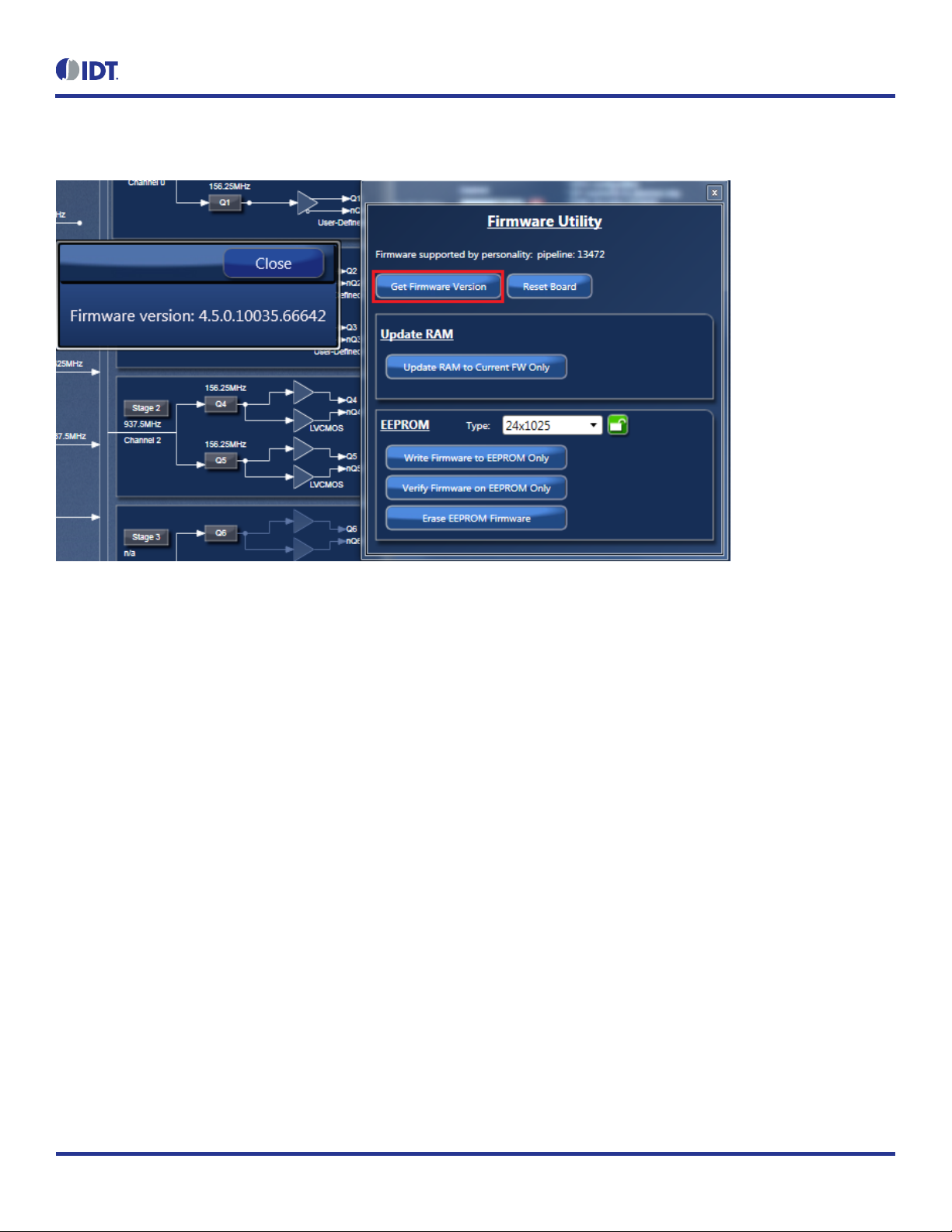

9. Within the Firmware Utility window, click the “Get Firmware Version” button to read the firmware version.

Figure 12. Read Firmware Version of ClockMatrix Chip

10. In the case where the firmware version mismatches each other, a firmware upgrade is necessary to update the chip’s firmware. To do so,

complete the steps in How to Upload Firmware (see Section 3) to update the chip’s firmware.

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

15

February 14, 2019

2.3 Output Terminations and Rework to Take 1PPS Input

All outputs are terminated with a 100Ωresistor across the output pair. This is the recommended termination regardless of the Voffset and

Vswing settings. Since the outputs are DC-coupled, they will support a 1PPS output without any need for rework.

Important Equipment Warning: When connecting the outputs to measurement equipment, use a DC-block to ensure

that the output operates at its intended Voffset. Otherwise, the equipment may load the output down and cause degraded

performance.

The following rework must be implemented in order to support a 1PPS input clock. All input clocks for this board are ac-coupled and terminated

as in the following figure.

Figure 13. AC Coupling and Terminations for Input Clock

For a 1PPS input, a single-ended input with DC-coupling is recommended. As such, the populated AC-coupling capacitor must be removed

and the input must be configured as LVCMOS, not differential.

1. In Figure 13, to make CLK0 supportive of 1PPS input, first configure CLK0 as LVCMOS in Timing Commander (see Figure 14).

Figure 14. Configuring CLK0 as CMOS to Receive a 1PPS Input

2. Once in LVCMOS mode, CLK0_P and CLK0_N will be two separate LVCMOS inputs instead of a differential pair. To make CLK0_P receive

a 1PPS input, replace C881 with a 0Ωresistor; and at the same time, remove R765 and R770.

!

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

16

February 14, 2019

3. How to Upload Firmware to the RAM

1. Connect to the EVK board.

2. Power up the board with no EEPROM present. This ensures the firmware is 4.0.2.7017, as displayed in the figure.

3. The GUI will indicate that the firmware on the chip does not match the GUI firmware. Press “Close”.

4. Open the “Firmware Utility” window by clicking on the button as follows.

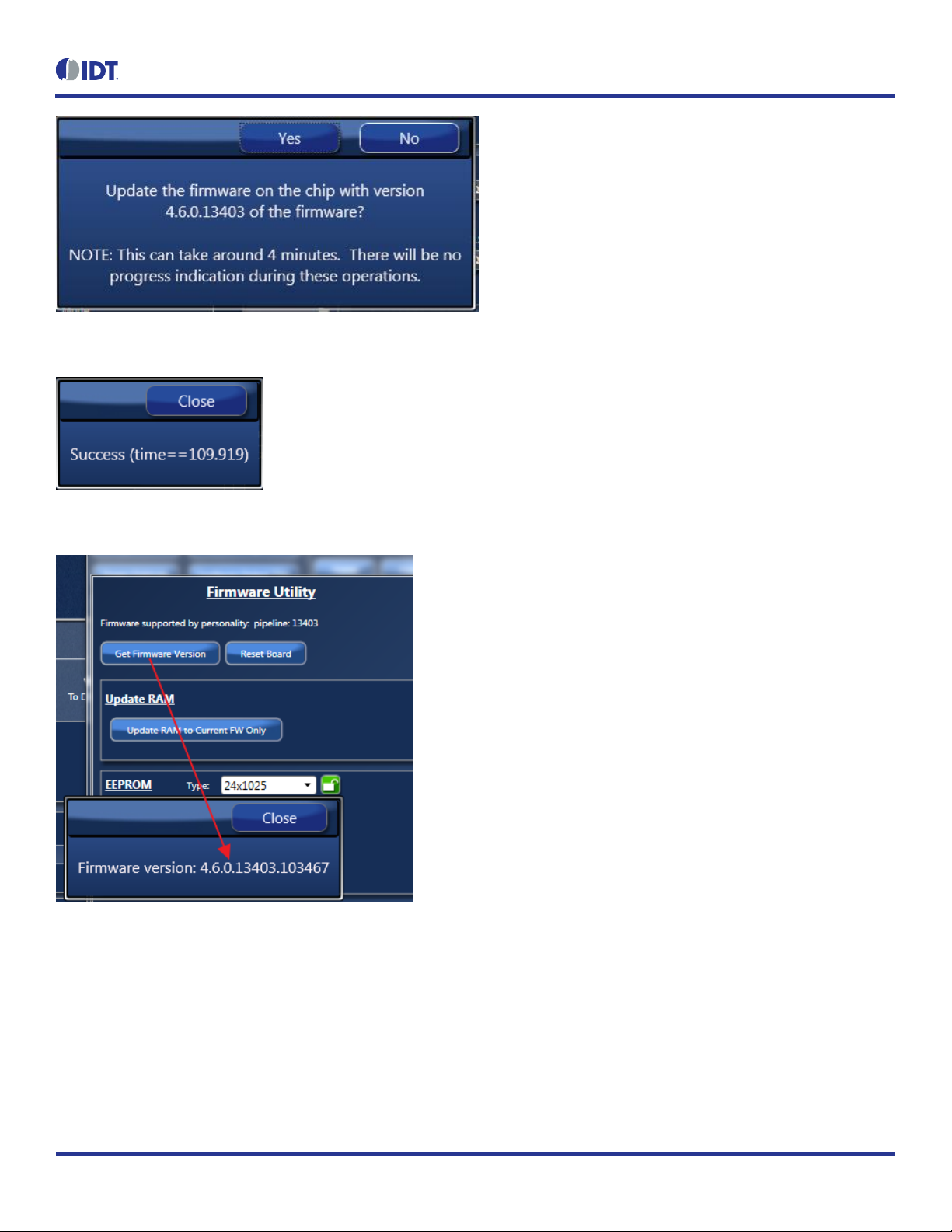

5. Update the Firmware first. Press “Update RAM to Current FW Only”.

6. In the next window, press “Yes” and wait around 3-4 minutes.

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

17

February 14, 2019

7. Once the firmware is updated, the following window will indicate a successful update. Click “Close”.

8. Press “Get Firmware Version” to verify that the RAM was updated correctly, then click “Close”.

8A3xxxx 72QFN EVK User Manual

© 2019 Integrated Device Technology, Inc.

18

February 14, 2019

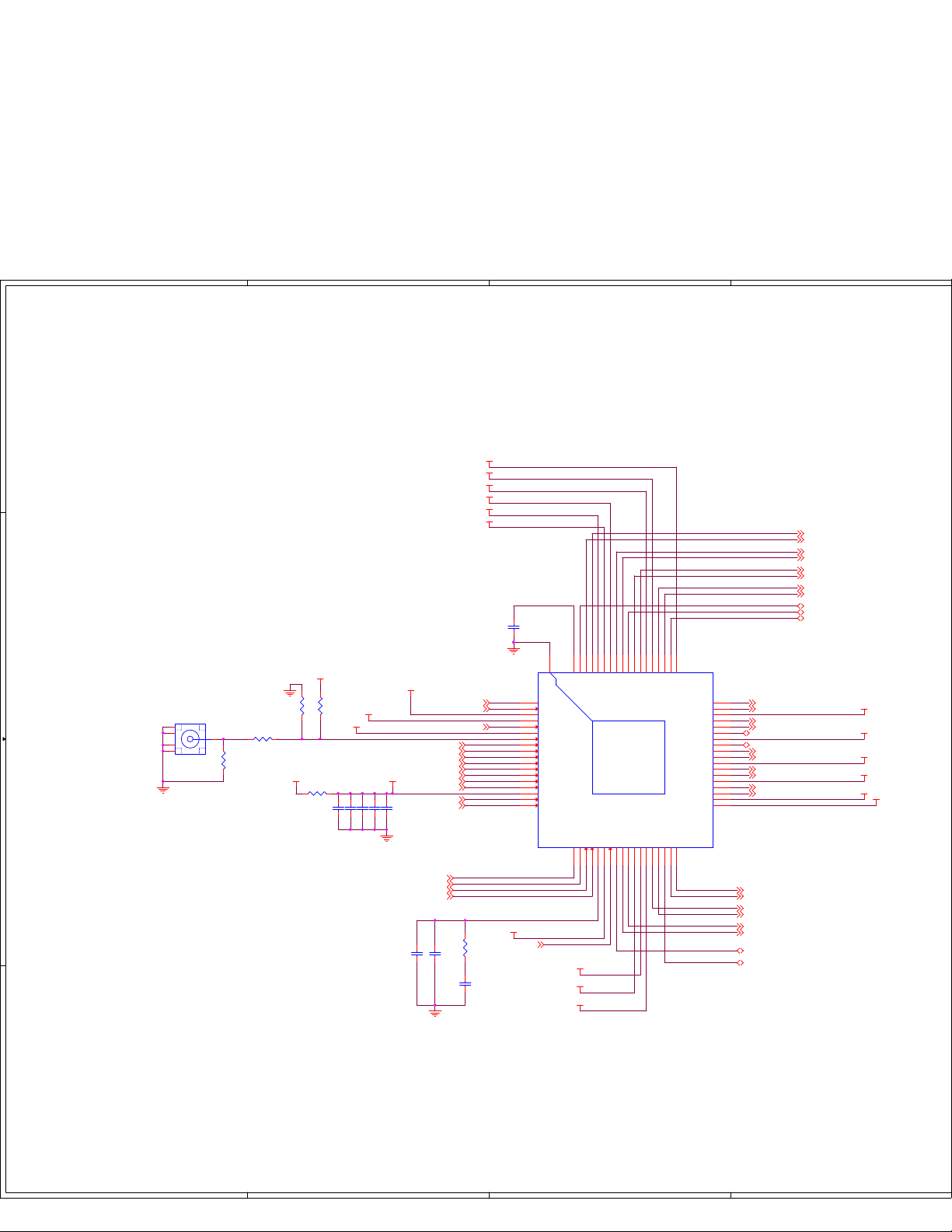

4. Schematics

Please see the schematics located at the end of this document.

5. Ordering Information

Orderable Part Number

Description

8A34044-EVK

8A3xxxx 72QFN Evaluation Kit

6. Revision History

Revision Date

Description of Change

February 14, 2019

Initial release.

Corporate Headquarters

6024 Silver Creek Valley Road

San Jose, CA 95138

www.IDT.com

Sales

1-800-345-7015 or 408-284-8200

Fax: 408-284-2775

www.IDT.com/go/sales

Tech Support

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its affiliated companies (herein referred to as “IDT”) reserve the ri ght to modify the products and/or specifications described herein at any time,

without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determine d in an independent state and are not guaranteed to perform the same

way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limite d to, the suitability

of IDT's products for any particular purpose, an implied warranty of merchantability, or non -infringement of the intellectual property rights of others. This document is presented only as a guide and does not

convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT pro duct can be

reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the

property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit www.idt.com/go/glossary. All contents of this document are copyright of Integrated

Device Technology, Inc. All rights reserved.

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

OF

PROJECT NAME

DRAWN

CHECK

DESIGN TITLE

DRAWING NUMBER REVISION

RELEASE DATE SHEET

SUBTITLE

1.2SK-10280-01

IDT8A34001

91

Fidus Systems

375 Terry Fox Drive, Ottawa, ON K2K 0J8

Indira3

DB

DB

DB

27 October 2016

Block Diagram

OF

PROJECT NAME

DRAWN

CHECK

DESIGN TITLE

DRAWING NUMBER REVISION

RELEASE DATE SHEET

SUBTITLE

1.2SK-10280-01

IDT8A34001

91

Fidus Systems

375 Terry Fox Drive, Ottawa, ON K2K 0J8

Indira3

DB

DB

DB

27 October 2016

Block Diagram

OF

PROJECT NAME

DRAWN

CHECK

DESIGN TITLE

DRAWING NUMBER REVISION

RELEASE DATE SHEET

SUBTITLE

1.2SK-10280-01

IDT8A34001

91

Fidus Systems

375 Terry Fox Drive, Ottawa, ON K2K 0J8

Indira3

DB

DB

DB

27 October 2016

Block Diagram

5

5

4

4

3

3

2

2

1

1

D D

C C

B B

A A

SILKSCRN:

XO_DPLL

Maximum voltage on pin 7 = 1.8V

Place close to ClockMatrix

VDDO_Q0

VDDO_Q1

VDDO_Q2

VDDO_Q3

VDDO_Q4

VDDO_Q5

VDDO_Q6

VDDO_Q7

VDDO_Q8

VDDO_Q9

VDDO_Q10

VDDO_Q11

VDD_FOD_0

VDD_FOD_2

VDD_FOD_5

VDDA_0

VDDA_1

VDD_FOD_0

VDD_CLK0_0

VDDD VDDD_0

VDD_FOD

CLK_Q0_P 8

CLK_Q0_N 8

CLK_Q1_P 8

CLK_Q1_N 8

CLK_Q2_P 8

CLK_Q2_N 8

CLK_Q3_P 8

CLK_Q3_N 8

CLK_Q4_P 8

CLK_Q4_N 8

CLK_Q5_P 8

CLK_Q5_N 8

CLK_Q6_P 8

CLK_Q6_N 8

CLK_Q7_P 8

CLK_Q7_N 8

CLK_Q8_P 8

CLK_Q8_N 8

CLK_Q9_P 8

CLK_Q9_N 8

CLK_Q10_P 8

CLK_Q10_N 8

CLK_Q11_P 8

CLK_Q11_N 8

GPIO3 5

GPIO9 5

GPIO1 5

GPIO2 5

GPIO4 5

GPIO5 5

GPIO0 5

CLK_CLK0_P

CLK_CLK0_N

CLK_CLK1_P

CLK_CLK1_N

CLK_CLK2_P

CLK_CLK2_N

CLK_CLK3_P

CLK_CLK3_N

CLK_CLK4_P

CLK_CLK4_N

OSCO

OSCI

PLL_I2C_SCL_SCLK

PLL_I2C_SDA_SDIO

PLL_I2C_SDA_SDI

PLL_I2C_SDA_CSN

JTAG_SEL

TST_CHIP_RST_N_OD

Title

Size Document Number Rev

Date: Sheet of

<Doc> <RevCode>

<Title>

C

1 1Monday, May 21, 2018

Title

Size Document Number Rev

Date: Sheet of

<Doc> <RevCode>

<Title>

C

1 1Monday, May 21, 2018

Title

Size Document Number Rev

Date: Sheet of

<Doc> <RevCode>

<Title>

C

1 1Monday, May 21, 2018

R3920

C418 2200pF

C694 0.1uF

U409

IDT8A35018

OSCO

1

OSCI

2

VDDA_PDCP_XTAL

3

VDDA_FB

4

nMR

5

VDD_CLK

6

XO_DPLL

7

CLK0

8

nCLK0

9

CLK1

10

nCLK1

11

CLK2

12

nCLK2

13

CLK3

14

nCLK3

15

VDD_DIG

16

CLK4

17

nCLK4

18

SCLK

19

SDIO

20

SDI_A1

21

CS_A0

22

FILTER

23

VDDA_LC_BG

24

nTEST

25

GPIO3

26

nQ11

27

Q11

28

VDDO_Q11

29

VDD_DIA_FOD_B

30

VDDO_Q7

31

Q7

32

nQ7

33

GPIO9

34

nQ6

35

Q6

36

VDDO_Q6 37

VDDO_Q5 38

Q5 39

nQ5 40

VDDO_Q4 41

Q4 42

nQ4 43

VDDO_Q10 44

Q10 45

nQ10 46

GPIO2 47

VDD_GPIO_FOD 48

GPIO1 49

nQ9 50

Q9 51

VDDO_Q9 52

nQ3 53

Q3 54

VDDO_Q3 55

GPIO5 56

nQ2 57

Q2 58

VDDO_Q2 59

VDDO_Q1 60

Q1 61

nQ1 62

GPIO4 63

nQ0 64

Q0 65

VDDO_Q0 66

VDD_DIA_FOD_A

67

VDDO_Q8 68

Q8 69

nQ8 70

GPIO0 71

cREG_XTAL 72

EPAD

73

R934 0

C695 0.1uF

R910 2.67kDNS

C871 0.1uF

R456

0

R467 2.67kDNS

C762 0.1uF

DNS

C761 10uF

R466 49.9

DNS

C763 0.1uF

DNS

C692 10uF

RK19-03-13

J46

5-1814832-1

C693 0.1uF

OSCI

OSCO

This manual suits for next models

1

Table of contents

Other IDT Motherboard manuals

IDT

IDT Tsi84 User manual

IDT

IDT EVK-UFT285-6-7 User manual

IDT

IDT ZSSC4151 User guide

IDT

IDT EB-LOGAN-23 User manual

IDT

IDT PhiClock 9FGV1001 User manual

IDT

IDT ZSSC4151 User manual

IDT

IDT VersaClock 3S User manual

IDT

IDT 8A34xxx 48QFN series User manual

IDT

IDT 89EBPES48H12 User manual

IDT

IDT 8A34 Series User manual