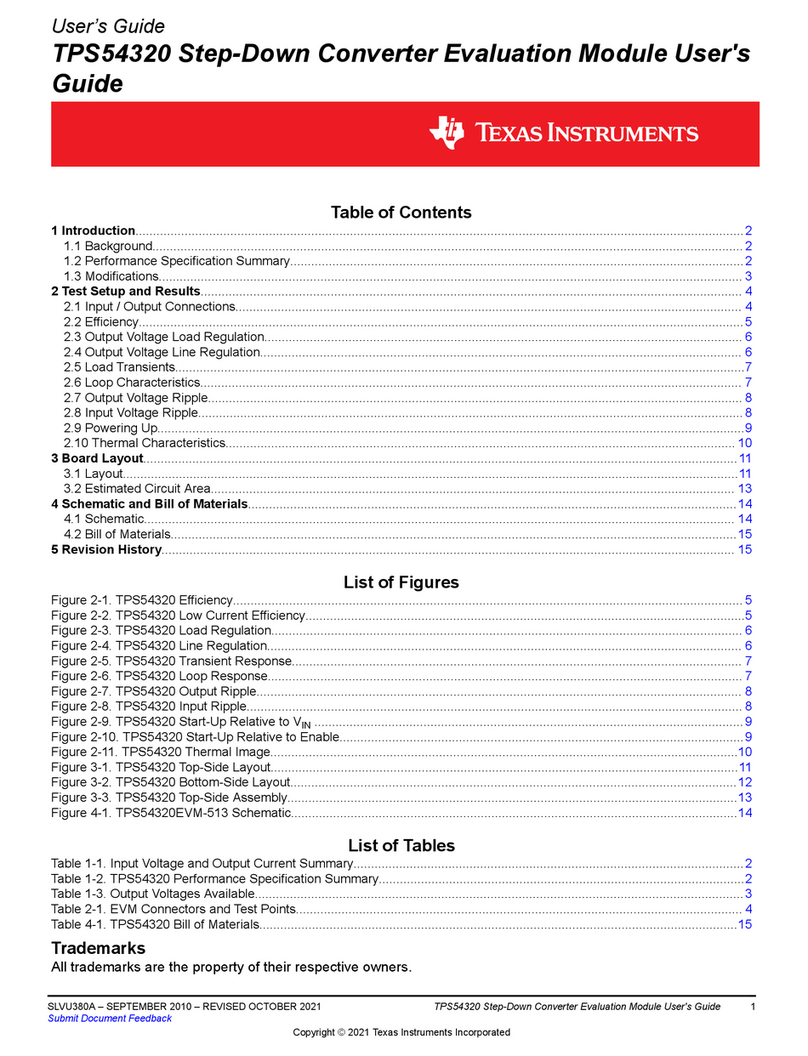

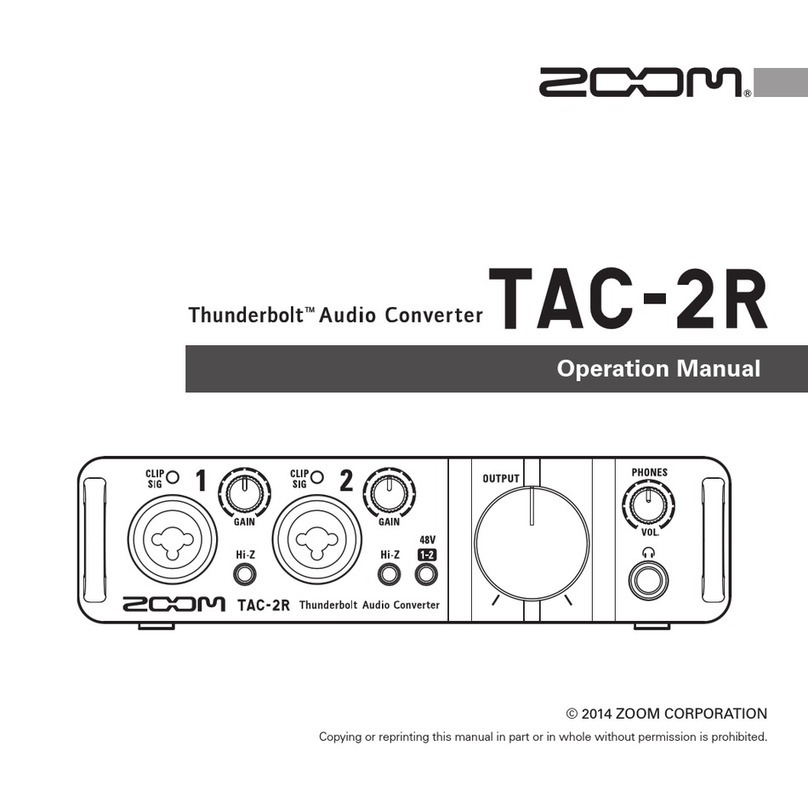

// Example C Code for setting up WSS/CGMS Line Mode Registers

//

// Load C-RAM

//

// NTSC WSS/CGMS Line Mode setup for line 20 of both fields

I2CWriteByte(TVP5151, 0xEC, 0x09); // line 20 field 1 (0xEC), mode bits = 0x09

I2CWriteByte(TVP5151, 0xED, 0x09); // line 20 field 2 (0xED), mode bits = 0x09

I2CWriteByte(TVP5151, 0xCB, 0x4E); // Set Pixel Alignment [7:0]to 0x4E

I2CWriteByte(TVP5151, 0xCC, 0x00); // Set Pixel Alignment [9:8]to 0x00

// PAL WSS/CGMS Line Mode setup for line 23 (source input) of both fields.

// PAL line numbering has 3 line offset so the Line 26 line mode registers are used.

I2CWriteByte(TVP5151, 0xF8, 0x08); // line 26 field 1 (0xF8), mode bits = 0x08

I2CWriteByte(TVP5151, 0xF9, 0x08); // line 26 field 2 (0xF9), mode bits = 0x08

I2CWriteByte(TVP5151, 0xCB, 0x4E); // Set Pixel Alignment [7:0]to 0x4E

I2CWriteByte(TVP5151, 0xCC, 0x00); // Set Pixel Alignment [9:8]to 0x00

Line Mode Registers

www.ti.com

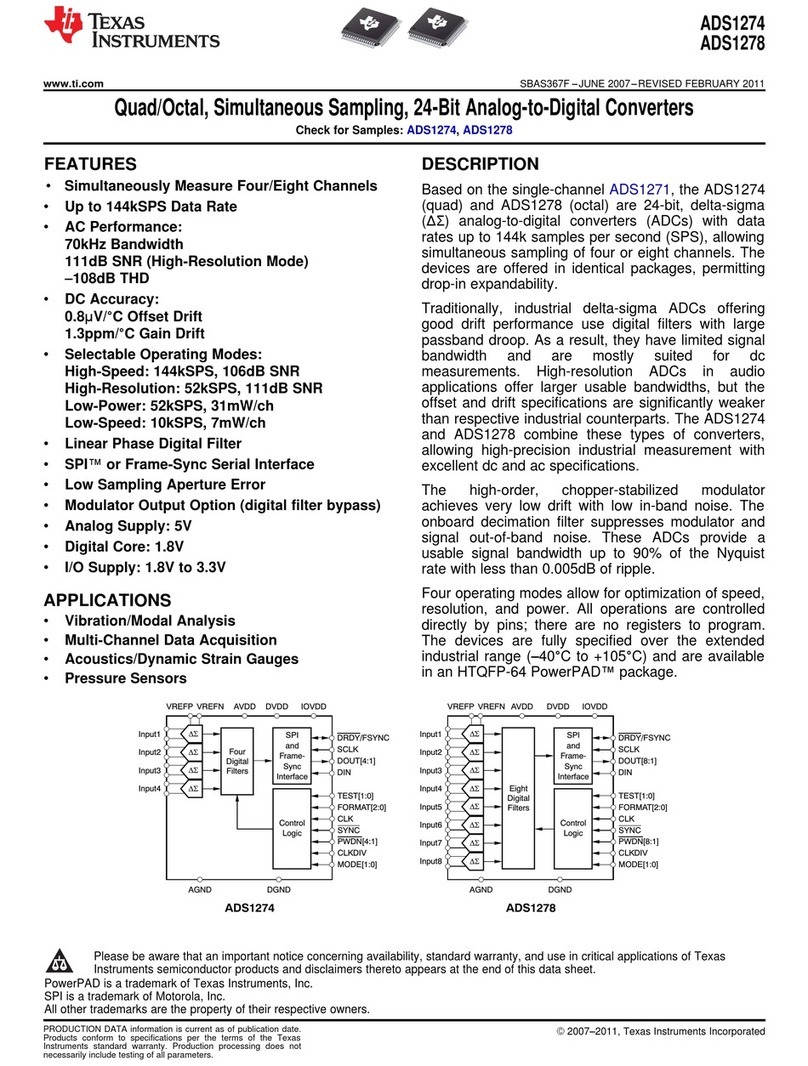

3 Line Mode Registers

After the VDP Configuration RAM is loaded, the Line Mode Registers (D0h-FBh) must be properly

configured for the desired VBI data service. Each register in this register bank is linked to a specific video

line number and video field. Video lines 6 through 27 of both Field 1 and Field 2 are supported. For each

desired data service, the proper mode configuration bits need to be loaded into the line mode register that

is linked to the correct video line number. Additional data slicing options such as filtering, error correction,

and FIFO routing are also available in the line mode registers. Unused line mode and line address

registers must be programmed with FFh. A detailed description of these registers is shown in Appendix A.

The TVP5151 VDP is based on an NTSC line numbering convention, resulting in a 3-line VDP offset

relative to actual PAL line numbers. For PAL systems, the Line Mode register for line “N+3” must be used

to configure a data service transmitted on line N of the input source. Figure 3 shows example C code for

configuring WSS/CGMS data services for NTSC and PAL. Included in this example is an I2C write to the

Pixel Alignment Registers (CBh-CCh), which define the horizontal position where data slicing begins. The

value used (4Eh) is recommended for all data services.

Table 3. Line Mode Configuration Bits for Supported Modes

Line Mode Register Name Video Line Number Description

(D0h-FCh) Bits [3:0]

0000b WST SECAM 6-23 (field 1, 2) Teletext, SECAM

0001b WST PAL B 6-22 (field 1, 2) Teletext, PAL, System B

0010b WST PAL C 6-22 (field 1, 2) Teletext, PAL, System C

0011b WST, NTSC B 10-21 (field 1, 2) Teletext, NTSC, System B

0100b NABTS, NTSC C 10-21 (field 1, 2) Teletext, NTSC, System C

0101b NABTS, NTSC D 10-21 (field 1, 2) Teletext, NTSC, System D (Japan)

0110b CC, PAL/SECAM 22 (field 1, 2) Closed caption PAL/SECAM

0111b CC, NTSC 21 (field 1, 2) Closed caption NTSC

1000b WSS/CGMS, PAL/SECAM 23 (field 1, 2) Wide-screen signal, PAL/SECAM

1001b WSS/CGMS, NTSC 20 (field 1, 2) Wide-screen signal, NTSC

1010b VITC, PAL/SECAM 6-22 Vertical interval timecode, PAL/SECAM

1011b VITC, NTSC 10-20 Vertical interval timecode, NTSC

1100b VPS, PAL 16 Video program system, PAL

1101b EPG/Gemstar Electronic program guide - Custom mode

1110b x x Reserved

1111b Active Video Active Video Active video/full field

Figure 3. Line Mode Setup for WSS/CGMS

6TVP5151 VBI Quick Start SLEA103–July 2010

Copyright © 2010, Texas Instruments Incorporated